并行編碼模數轉換器(ADC),ADC的基本原理

背景知識:模數轉換器(Analog to digital Converter,簡稱ADC)是模擬與數字世界的接口,為了適應計算機、通訊、多媒體技術的飛速發展以及高新技術領域的數字化進程的不斷加快,ADC正朝著低功耗、高速、高分辨率方向發展。目前市場化的ADC有很多種類型。

近年來,我國在有限的工藝水平條件下積極開展了對ADC的研究,并取得了令人鼓舞的成果,但是與國際水平相比尚有差距,電路結構設計也略顯單調,折疊式、流水線型、E一△型結構鮮見報道。統計資料表明,8-12位精度范圍的高速A/D轉換器是應用最廣泛、需求最迫切的品種,因此研制出我國具有自主知識產權的高速高精度、高速、低功耗的ADC具有十分重要的意義。目前市場化的ADC有多種結構,如并行(Flash,或稱Parallel)A DC,逐次逼近型ADC、積分型ADC,壓頻變換型ADC以及流水線型ADC和Delta-Sigma型ADC等,其中后兩種ADC是新發展起來的,這些ADC各有各的特點,根據不同的應用場合,選用的ADC的結構也是不同的。

基本原理:

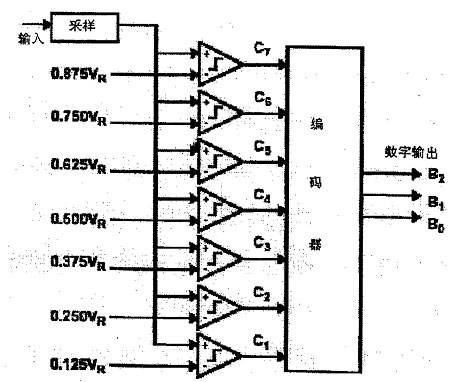

并行ADC轉換器是目前速度很快的一種結構。該結構在設計思想很容易理解。一個n位的并行ADC包含2n-1個比較器和2n-1個參考電壓值(對于一般的電壓模電路,對于電流模電路,是參考電流值)。每一個比較器對輸入信號采樣并把輸入信號與參考電壓相比較,然后每一個比較器產生一位輸出,表明輸入信號比參考電壓大還是小。2n-1個比較器輸出通常稱為溫度計代碼。該名稱的來源是,如果把比較器的輸出根據參考電壓值的大小順序排成一列,所有的1都在下面,所有的0都在上面,0和1的分界線表示信號值所在的范圍,由于和水銀溫度計表示溫度的方法相類似,因此稱為溫度計代碼。如圖為一個簡單的3位并行ADC的結構圖。譯碼器把比較器產生的溫度計代碼轉換成如表所示的二進制代碼。如圖所示,所有的比較器并行工作。因此,轉換速度僅僅受比較器的速度或采樣速度的限制,所以并行ADC具有很高轉換速度。

并行ADC的不足之處是硬件需求量大和對比較器偏移比較敏感。上面己經提到,一個n位的ADC需要2n-1個比較器。因此,高分辨率的并行ADC需要較大的芯片面積,這樣電路的功耗也增加很多。此外,大量的比較器使采樣電路要驅動很大的電容。n位分辨率的并行ADC要求比較器的偏移小于VR/2n。在較高的分辨率下,這要求比較器的偏移非常小。由于小偏移的比較器設計難度大、價格高,而且所用的比較器數量很大,因此超過8位的ADC很少用全并行結構。

非常好我支持^.^

(15) 100%

不好我反對

(0) 0%

相關閱讀:

( 發表人:admin )