雙平衡模擬乘法器的基本原理

2010年03月24日 13:55 www.xsypw.cn 作者:佚名 用戶評論(0)

關鍵字:乘法器(36289)

雙平衡模擬乘法器的基本原理

基本原理

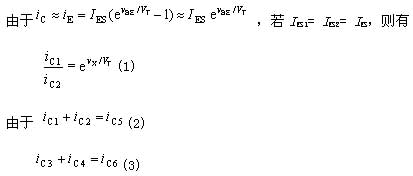

雙平衡式四象限乘法電路如圖1(a)所示,該電路由兩個并聯工作的差分式電路T1、T2和T3、T4及T5、T6構成的壓控電流源電路組成。圖1(b)為模擬乘法器符號。

由式(1)和式(2) 同理可得

在圖中假定正向的條件下,輸出電壓vO為

式中 輸入電壓vX、vY均可為正值或負值,故是一種四象限模擬乘法器。它的缺點是當輸入信號較大時,會帶來嚴重的非線性影響。

非常好我支持^.^

(12) 100%

不好我反對

(0) 0%

相關閱讀:

- [電子說] 觸控小家電國產MCU新選擇—LKT6850 2023-10-13

- [可編程邏輯] FPGA浮點IP內核究竟有哪些優勢呢? 2023-09-25

- [模擬技術] 使用模擬乘法器的同步解調與基于開關的乘法器 2023-10-04

- [電子說] INA226驅動程序 2023-07-17

- [電子說] 乘法器的Verilog HDL實現方案 2023-06-21

- [電子說] 基于DSP48E1的FIR濾波器設計 2023-06-02

- [電子說] HMC575LP4ETR有源寬帶倍頻器典型應用 2023-05-31

- [電子說] FPGA常用運算模塊-復數乘法器 2023-05-22

( 發表人:admin )