四進制電平,四進制電平是什么意思

四進制電平,四進制電平是什么意思

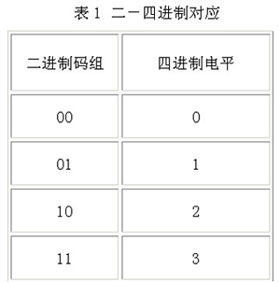

在二進制數(shù)字通信系統(tǒng)中,每個碼元或每個符號只能是“1”和“0”兩個狀態(tài)之一。若將每個碼元可能取的狀態(tài)增加到4、8、16…等等,就需用4、8、16…進制等信號。四狀態(tài)用 3、2、1和0四種電平表示的四電平四進制信號。這里一個四進制符號代表兩位二進制碼組,其編碼規(guī)則和二-四進制對應關(guān)系如表1所示。八狀態(tài)用八電平表示。

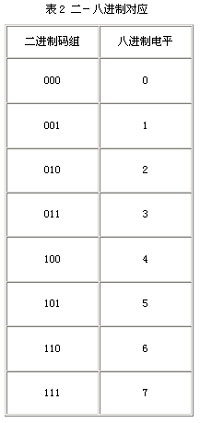

上圖為二進制與多進制波形示意圖 這里一個八進制符號代表三位二進制碼組,其編碼組,其編碼規(guī)則如表2所示。四進制級差為E/3,八進制級差為E/7。顯然,進制越高,級差越小,抗干擾能力越差。但是進制越高,每個符號所代表的信息量愈大。在信息論中對符號所載荷的信息量有嚴格定義。在二進制電平數(shù)字傳輸中,若數(shù)字序列里1和0的概率各占1/2,并且前后碼元是相互獨立的 ,序列中每個二進制碼元所載荷的信息量就是1比特 ,而多進制電平數(shù)字傳輸中,每個符號所含的信息量有所增加,對于四電平的符號包含2bit信息量,八電平的符號包含3bit的信息量。從圖3中可以看出四電平的四種狀態(tài),分別代表兩個二進制組成的四種狀態(tài),即00,01,10和11。因此一個四進制符號包含2比特信息量。同樣一個八進制符號代 表三個二進制符號,因此包含3比特信息量。

非常好我支持^.^

(210) 98.6%

不好我反對

(3) 1.4%

相關(guān)閱讀:

- [電子說] 既然ODR能控制管腳高低電平,為什么還需要BSRR寄存器呢? 2023-10-24

- [電子說] ARM系列-P Channel簡析 2023-10-24

- [電子說] 對于波形和電平不標準的時鐘信號一般應進行怎樣的處理? 2023-10-24

- [電子說] 電平信號與電壓信號的區(qū)別 不同的電平信號怎么進行“溝通”? 2023-10-24

- [電子說] TTL與BJT的基礎(chǔ)知識 2023-10-21

- [電子說] 邏輯電平測試筆設(shè)計方案 2023-10-18

- [EMC/EMI設(shè)計] 淺談系統(tǒng)應用EMI傳導問題2 2023-10-18

- [PCB設(shè)計] 針對雙面PCB的在線測試儀模塊構(gòu)成 2023-10-17

( 發(fā)表人:admin )