信號(hào)完整性問(wèn)題是高速PCB設(shè)計(jì)者必需面對(duì)的問(wèn)題。阻抗匹配、合理端接、正確拓?fù)浣Y(jié)構(gòu)解決信號(hào)完整性問(wèn)題的

2010-10-11 10:43:57 1941

1941

通常說(shuō)的信號(hào)完整性就是指信號(hào)無(wú)失真的進(jìn)行傳輸。前面我們討論很多信號(hào)完整性問(wèn)題,包括時(shí)序、串?dāng)_、衰減、反射、電源完整性、EMC等等。

2022-09-29 17:00:06 1045

1045 在實(shí)際的應(yīng)用場(chǎng)景中,會(huì)遇到多種信號(hào)完整性問(wèn)題,典型問(wèn)題有如下幾種:反射、串?dāng)_,電源/地噪,時(shí)序等。其中,發(fā)射和串?dāng)_是引起信號(hào)完整性問(wèn)題的兩大主要原因。

2022-10-09 10:56:55 3291

3291 信號(hào)完整性分析是一個(gè)很復(fù)雜的系統(tǒng)工程,它是各種影響信號(hào)質(zhì)量和時(shí)序的問(wèn)題的疊加組合。且隨著信號(hào)速率的提高,信號(hào)完整性問(wèn)題變得越來(lái)越復(fù)雜,需要考慮的因素越來(lái)越多。

2023-06-15 15:07:59 995

995

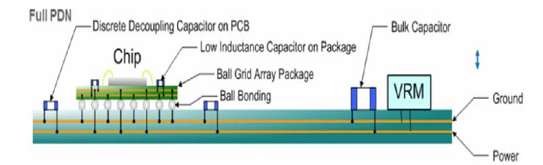

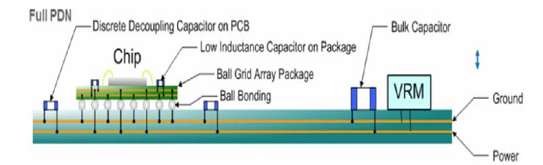

電源的作用是為系統(tǒng)提供穩(wěn)定的電壓及電流。電源完整性問(wèn)題是指電源的電壓、紋波及噪聲不滿足系統(tǒng)的工作要求,通過(guò)合理的電源供電網(wǎng)絡(luò)設(shè)計(jì)可以減小電源塌陷等電源完整性問(wèn)題,提高系統(tǒng)的穩(wěn)定性。

2024-02-22 10:09:11 466

466

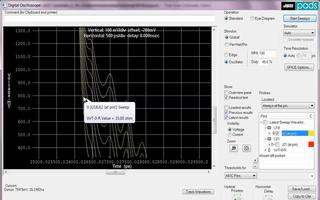

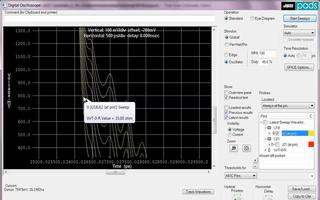

寬、眼圖與數(shù)據(jù)完整性 介紹眼圖分析的重要性,常見(jiàn)眼圖反映的信號(hào)完整性、數(shù)據(jù)完整性問(wèn)題;抖動(dòng)的概念及產(chǎn)生的原因;抖動(dòng)的分類和分解方法;抖動(dòng)分析的方法;抖動(dòng)測(cè)試和分析實(shí)例。分析趨膚效應(yīng)下的導(dǎo)線損耗和介質(zhì)

2010-12-16 10:03:11

測(cè)試結(jié)果。由于信號(hào)完整性問(wèn)題經(jīng)常作為間歇性錯(cuò)誤出現(xiàn),因此重視同步切換控制、仿真和封裝,保證設(shè)計(jì)符合信號(hào)完整性要求,在硅片制造前解決問(wèn)題。對(duì)于IC應(yīng)用,可利用仿真來(lái)選擇合理的端接元件和優(yōu)化元器件的布局,更

2013-12-05 17:44:44

信號(hào)完整性資料

2015-09-18 17:26:36

很不錯(cuò)的一本信號(hào)完整性教材。其實(shí)EMC、EMI問(wèn)題最終都是信號(hào)完整性問(wèn)題。

2011-12-09 22:49:23

信號(hào)完整性分析與設(shè)計(jì)信號(hào)完整性設(shè)計(jì)背景???什什么是信號(hào)完整D??信信號(hào)完整性設(shè)計(jì)內(nèi)è??典典型信號(hào)完整性問(wèn)題與對(duì)2現(xiàn)在數(shù)字電路發(fā)展的趨ê??速速率越來(lái)越???芯芯片集成度越來(lái)越高£P(guān)C板板越來(lái)越

2009-09-12 10:20:03

的表達(dá)方式具有不同的適應(yīng)能力,因此,需要進(jìn)一步根據(jù)實(shí)際的傳輸環(huán)境來(lái)選擇或優(yōu)化可行的傳輸協(xié)議及數(shù)據(jù)內(nèi)容表達(dá)方式。 圖1 背板信號(hào)傳輸?shù)南到y(tǒng)示意圖 版圖完整性問(wèn)題、分析與設(shè)計(jì) 上述背板系統(tǒng)中的硬件支撐

2015-01-07 11:33:53

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì),不看肯定后悔

2021-05-12 06:40:35

值仿真工具,這些分析可以應(yīng)用于建模和仿真。7、測(cè)量無(wú)源器件和互連線的電氣特性的儀器一般有三種:阻抗分析儀、網(wǎng)絡(luò)分析儀和時(shí)域反射儀。8、這些儀器對(duì)減小設(shè)計(jì)風(fēng)險(xiǎn)、提高建模和仿真過(guò)程精度的可信度起著重要作用。9、理解這四種信號(hào)完整性問(wèn)題可以得出消除這些問(wèn)題的最重要的方法。

2015-12-12 10:30:56

本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題?

2021-01-25 06:51:11

信號(hào)完整性問(wèn)題和印制電路板設(shè)計(jì)

2023-09-28 06:11:27

來(lái)電來(lái)函咨詢)五、研討內(nèi)容 案例分析與討論 介紹與討論如何發(fā)現(xiàn)信號(hào)完整性問(wèn)題;如何布局保證信號(hào)完整等等。 六、培訓(xùn)方式:結(jié)合交流、討論、案例分析等互動(dòng)的方式。并為學(xué)員與專家、學(xué)員與學(xué)員之間建立廣闊

2010-05-29 13:29:11

邏輯分析儀和 89601A 矢量信號(hào)分析軟件(數(shù)字 VSA)技術(shù)綜述

2019-10-15 10:58:07

邏輯分析儀是什么?邏輯分析儀和示波器的區(qū)別是什么?

2021-11-12 06:23:04

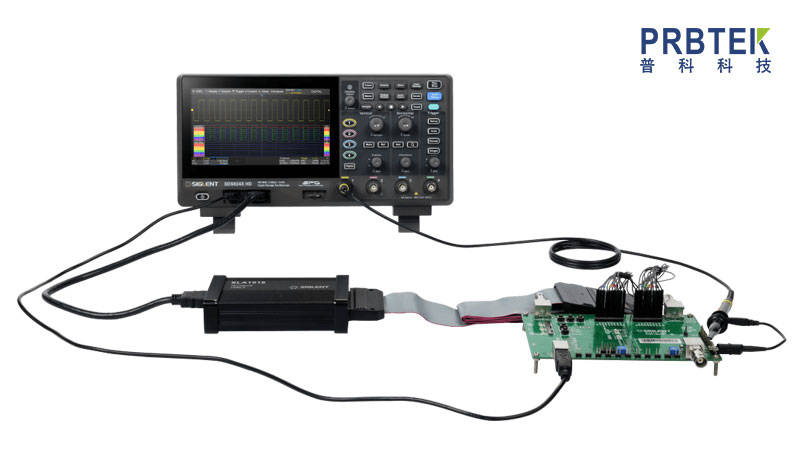

成為基本的測(cè)試工具。 邏輯分析儀是利用時(shí)鐘從測(cè)試設(shè)備上采集和顯示數(shù)字信號(hào)的儀器,最主要作用在于時(shí)序判定。由于邏輯分析儀不像示波器那樣有許多電壓等級(jí),通常只顯示兩個(gè)電壓(邏輯1和0),因此設(shè)定了參考電壓

2017-09-28 09:30:56

邏輯分析儀在數(shù)字電路測(cè)試中的觸發(fā)選擇延遲觸發(fā)有哪幾種類型?邏輯定時(shí)分析儀和邏輯狀態(tài)分析儀的區(qū)別是什么?

2021-04-12 06:55:10

僅能對(duì)傳輸線阻抗、信號(hào)反射和信號(hào)間串?dāng)_等多種設(shè)計(jì)中存在的信號(hào)完整性問(wèn)題以圖形的方式進(jìn)行分析,而且還能利用規(guī)則檢查發(fā)現(xiàn)信號(hào)完整性問(wèn)題,同時(shí),Altium Designer還提供一些有效的終端選項(xiàng),來(lái)幫助您選擇

2015-12-28 22:25:04

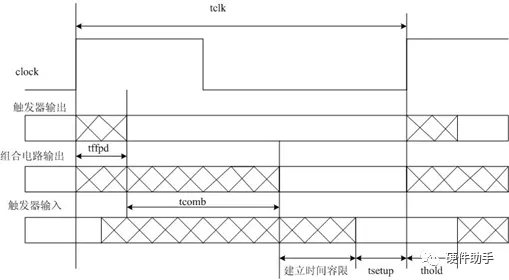

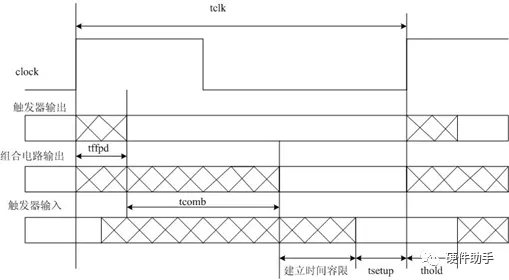

的速度傳輸,信號(hào)從驅(qū)動(dòng)端發(fā)出到達(dá)接收端,其間存在一個(gè)傳輸延遲。過(guò)多的信號(hào)延遲或者信號(hào)延遲不匹配可能導(dǎo)致時(shí)序錯(cuò)誤和邏輯器件功能混亂。 基于信號(hào)完整性分析的高速數(shù)字系統(tǒng)設(shè)計(jì)分析不僅能夠有效地提高產(chǎn)品的性能

2018-11-27 15:22:34

`編輯推薦《國(guó)外電子與通信教材系列:信號(hào)完整性與電源完整性分析(第二版)》強(qiáng)調(diào)直覺(jué)理解、實(shí)用工具和工程素養(yǎng)。作者以實(shí)踐專家的視角指出造成信號(hào)完整性問(wèn)題的根源,并特別給出了設(shè)計(jì)階段前期的問(wèn)題解決

2017-09-19 18:21:05

`編輯推薦本書(shū)全面論述了信號(hào)完整性與電源完整性問(wèn)題。主要講述信號(hào)完整性分析及物理設(shè)計(jì)概論,6類信號(hào)完整性問(wèn)題的實(shí)質(zhì)含義,物理互連設(shè)計(jì)對(duì)信號(hào)完整性的影響,電容、電感、電阻和電導(dǎo)的特性分析,求解信號(hào)

2017-08-08 18:03:31

`` 本帖最后由 lzr858585 于 2021-4-6 11:11 編輯

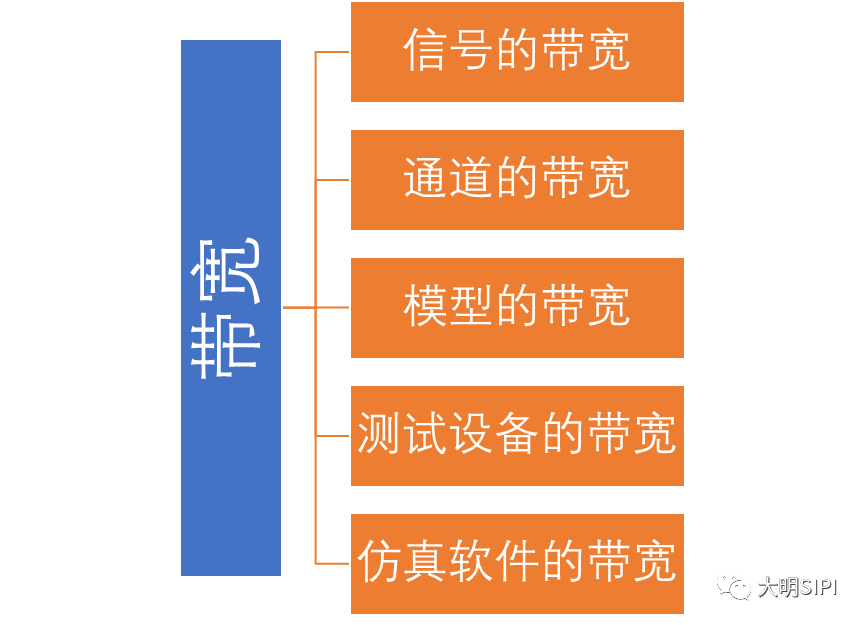

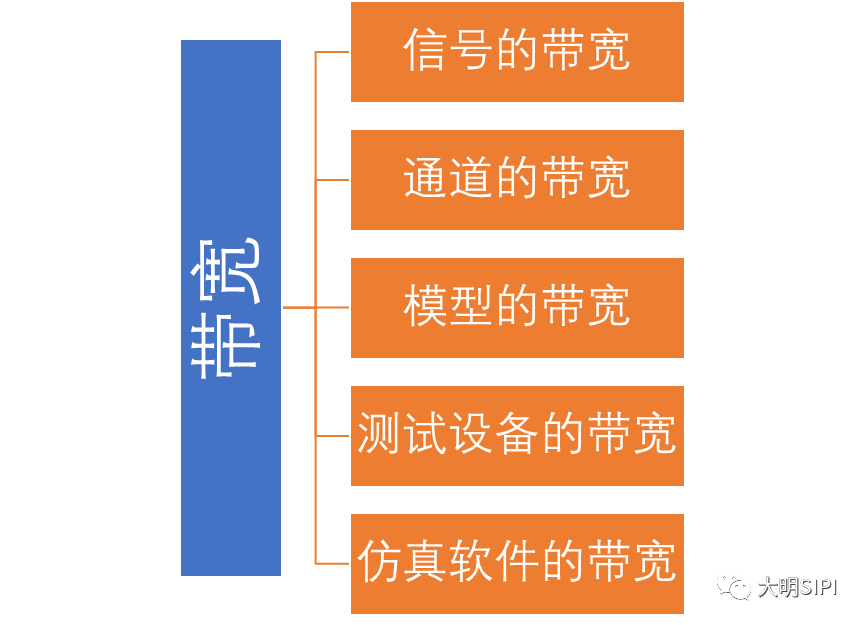

本書(shū)主要介紹信號(hào)完整性和物理設(shè)計(jì)概論,帶寬、電感和特性阻抗的實(shí)質(zhì),電阻電容電感和阻抗的相關(guān)分析。解決SI完整性問(wèn)題的四個(gè)實(shí)用技術(shù)手段,物理互連設(shè)計(jì)對(duì)信號(hào)的影響,數(shù)學(xué)推導(dǎo)背后邏輯,改進(jìn)信號(hào)完整性的推薦設(shè)計(jì)準(zhǔn)則等。``

2021-04-06 11:10:15

、持續(xù)時(shí)間和電壓幅度到達(dá)接收端時(shí),該電路就有很好的信號(hào)完整性。當(dāng)信號(hào)不能正常響應(yīng)時(shí),就出現(xiàn)了信號(hào)完整性問(wèn)題。信號(hào)完整性包含:1、波形完整性(Waveform integrity)2、時(shí)序完整性(Timi...

2021-12-30 08:15:58

在高速設(shè)計(jì)中,如何解決信號(hào)的完整性問(wèn)題?差分布線方式是如何實(shí)現(xiàn)的?對(duì)于只有一個(gè)輸出端的時(shí)鐘信號(hào)線,如何實(shí)現(xiàn)差分布線?

2021-10-26 06:59:21

在高速設(shè)計(jì)中,如何解決信號(hào)的完整性問(wèn)題?

2009-09-06 08:42:10

采取有效的控制措施,提高電路設(shè)計(jì)質(zhì)量,是必須考慮的問(wèn)題。借助功能強(qiáng)大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對(duì)高速信號(hào)進(jìn)行信號(hào)完整性仿真分析是一種高效可行的分析方法

2015-01-07 11:30:40

安捷倫科技邏輯分析儀和FuturePlus系統(tǒng)合作

2019-09-27 15:12:29

時(shí)序分析-- 信號(hào)完整性問(wèn)題(SI)

2014-05-16 10:44:11

用Keysight邏輯分析儀和89601A矢量信號(hào)分析軟件實(shí)現(xiàn)數(shù)字矢量信號(hào)分析

2019-09-23 14:16:58

如何快速解決高速系統(tǒng)的信號(hào)完整性問(wèn)題?

2021-04-27 06:03:49

高速PCB設(shè)計(jì)的信號(hào)完整性問(wèn)題 隨著器件工作頻率越來(lái)越高,高速PCB設(shè)計(jì)所面臨的信號(hào)完整性等問(wèn)題成爲(wèi)傳統(tǒng)設(shè)計(jì)的一個(gè)瓶頸,工程師在設(shè)計(jì)出完整的解決方案上面臨越來(lái)越大的挑戰(zhàn)。盡管有關(guān)的高速仿真工具

2012-10-17 15:59:48

高速pcb的信號(hào)完整性問(wèn)題主要有哪些?應(yīng)如何消除?

2023-04-11 15:06:07

高速pcb的信號(hào)完整性問(wèn)題主要有哪些?應(yīng)如何消除?

2023-04-07 17:32:10

在高速電路設(shè)計(jì)中信號(hào)完整性分析由于系統(tǒng)時(shí)鐘頻率和上升時(shí)間的增長(zhǎng),信號(hào)完整性設(shè)計(jì)變得越來(lái)越重要。不幸的是,絕大多數(shù)數(shù)字電路設(shè)計(jì)者并沒(méi)意識(shí)到信號(hào)完整性問(wèn)題的重要性,或者是直到設(shè)計(jì)的最后階段才初步認(rèn)識(shí)到

2009-10-14 09:32:02

本文分析了高速電路設(shè)計(jì)中的信號(hào)完整性問(wèn)題,提出了改善信號(hào)完整性的一些措施,并結(jié)合一個(gè)VGA視頻分配器系統(tǒng)的設(shè)計(jì)過(guò)程,具體分析了改善信號(hào)完整性的方法。

2021-06-03 06:22:05

本文分析了高速電路設(shè)計(jì)中的信號(hào)完整性問(wèn)題,提出了改善信號(hào)完整性的一些措施,并結(jié)合一個(gè)VGA視頻分配器系統(tǒng)的設(shè)計(jì)過(guò)程,具體分析了改善信號(hào)完整性的方法。

2021-06-04 06:16:07

深入研究高速數(shù)字電路設(shè)計(jì)中的信號(hào)完整性問(wèn)題;分析電路中破壞信號(hào)完整性的原因;結(jié)合一個(gè)實(shí)際的DSP 數(shù)據(jù)采集系統(tǒng), 闡述實(shí)現(xiàn)信號(hào)完整性的具體方法。

2009-04-15 09:08:03 16

16 深入研究高速數(shù)字電路設(shè)計(jì)中的信號(hào)完整性問(wèn)題;分析電路中破壞信號(hào)完整性的原因;結(jié)合一個(gè)實(shí)際的DSP 數(shù)據(jù)采集系統(tǒng), 闡述實(shí)現(xiàn)信號(hào)完整性的具體方法。

2009-05-18 13:24:58 17

17 高速電路信號(hào)完整性分析與設(shè)計(jì)—信號(hào)完整性仿真:仿真信號(hào)仿真中有兩類信號(hào)可稱之為高速信號(hào):高頻率的信號(hào)(>=50M)上升時(shí)間tr很短的信號(hào):信號(hào)上

2009-10-06 11:19:50 0

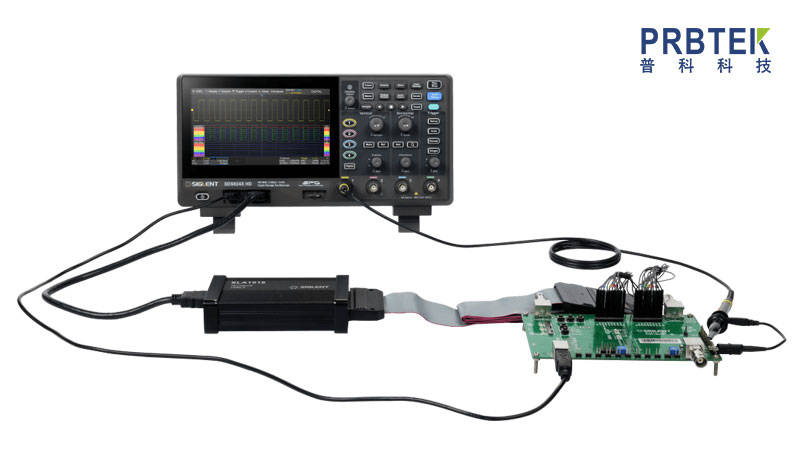

0 高速并行總線信號(hào)完整性測(cè)試技術(shù):隨著信號(hào)速度的顯著提高,信號(hào)完整性問(wèn)題已經(jīng)成為高速數(shù)字設(shè)計(jì)中的關(guān)鍵。本文介紹了一種新的信號(hào)完整性分析技術(shù),通過(guò)集成邏輯分析儀和

2009-10-17 17:11:55 0

0 信號(hào)完整性原理分析

什么是“信號(hào)完整性”?在傳統(tǒng)的定義中“完整性(integrity)”指完整和末受損的意思。因此,具有良好完整性的數(shù)字信號(hào)應(yīng)是干凈,

2009-11-04 12:07:06 210

210 在高速設(shè)計(jì)中,如何解決信號(hào)的完整性問(wèn)題?

信號(hào)完整性基本上是阻抗匹配的問(wèn)題。而影響阻抗匹配的因素有信號(hào)源的架構(gòu)和輸出阻

2010-01-02 11:15:06 1097

1097

SPARQ系列信號(hào)完整性網(wǎng)絡(luò)分析儀。SPARQ在高達(dá)4端口上測(cè)量頻率40GHz的S參數(shù),一鍵操作,而且成本只有傳統(tǒng)測(cè)量

2010-10-10 08:36:25 1692

1692 深入了解怎樣在當(dāng)前日益復(fù)雜的嵌入式系統(tǒng)中迅速定位、隔離和檢定難檢的信號(hào)完整性問(wèn)題。

2010-11-16 11:18:25 548

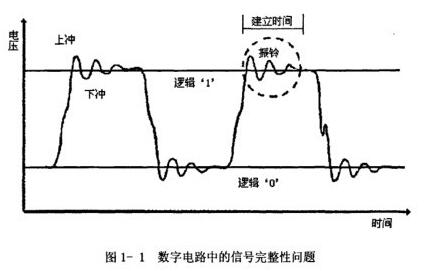

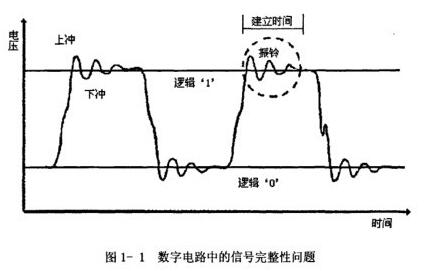

548 文章介紹了數(shù)字電路設(shè)計(jì)中的信號(hào)完整性問(wèn)題, 探討了振鈴、邊沿畸變、反射、地彈、串?dāng)_和抖動(dòng)等各種信號(hào)完整性問(wèn)題的成因和抑制措施。針對(duì)常見(jiàn)的反射和串?dāng)_給出了較為詳細(xì)的分

2011-09-07 16:14:58 104

104 采用全波分析工具研究高頻時(shí)多層PCB(Printed Circuit Board)板中電源平面與地平面之間的諧振模式及其對(duì)信號(hào)完整性的影響。同時(shí)分析了不同過(guò)孔方式,去耦電容的大小和位置對(duì)信號(hào)完整性

2011-09-21 14:23:34 0

0 介紹引起信號(hào)完整性問(wèn)題的主要因素, 利用。進(jìn)行信號(hào)仿真的步驟, 給出了的信號(hào)仿真的時(shí)比結(jié)果, 并以該信號(hào)作為分析對(duì)象, 詳細(xì)分析了為判斷信號(hào)質(zhì)童的優(yōu)劣, 對(duì)仿真波形進(jìn)行定量分析

2011-11-30 11:09:46 0

0 為了使設(shè)計(jì)人員對(duì)信號(hào)完整性與電源完整性有個(gè)全面的了解,文中對(duì)信號(hào)完整性與電源完整性的問(wèn)題進(jìn)行了仿真分析與設(shè)計(jì),也從系統(tǒng)的角度對(duì)其進(jìn)行了探討。

2011-11-30 11:12:24 0

0 本專題詳細(xì)介紹了信號(hào)完整性各部分知識(shí),包括信號(hào)完整性的基礎(chǔ)概述,信號(hào)完整性設(shè)計(jì)分析及仿真知識(shí),還有具體應(yīng)用中的一些小經(jīng)驗(yàn)分享等等,充分翔實(shí)的向大家描述了信號(hào)完整性。

2011-11-30 11:44:35

信號(hào)完整性分析 美國(guó)Eric教授著作,李玉山教授編譯

2015-11-11 16:51:55 0

0 本書(shū)全面論述了信號(hào)完整性問(wèn)題。主要講述了信號(hào)完整性和物理設(shè)計(jì)概論,帶寬、電感和特性阻抗的實(shí)質(zhì)含義,電阻、電容、電感和阻抗的相關(guān)分析,解決信號(hào)完整性問(wèn)題的四個(gè)實(shí)用技術(shù)手段,物理互連設(shè)計(jì)對(duì)信號(hào)完整性

2015-11-10 17:36:24 0

0 繪制電路圖過(guò)程的信號(hào)完整性問(wèn)題,好東西,喜歡的朋友可以下載來(lái)學(xué)習(xí)。

2016-01-18 17:03:29 0

0 信號(hào)完整性分析,有需要的朋友可以下來(lái)看看

2016-02-19 16:48:21 0

0 電地完整性、信號(hào)完整性分析導(dǎo)論,有需要的下來(lái)看看

2016-02-22 16:18:01 69

69 10129@52RD_信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

2016-12-14 21:27:39 0

0 數(shù)字信號(hào)傳輸系統(tǒng)各個(gè)環(huán)節(jié)的信號(hào)完整性模型。 (2)在設(shè)計(jì)原理圖過(guò)程中,利用信號(hào)完整性模型對(duì)關(guān)鍵網(wǎng)絡(luò)進(jìn)行信號(hào)完整性預(yù)分析,依據(jù)分析結(jié)果來(lái)選擇合適的元器件參數(shù)和電路拓?fù)浣Y(jié)構(gòu)等。 (3)在原理圖設(shè)計(jì)完成后,結(jié)合PCB的疊層設(shè)計(jì)參數(shù)和原理圖

2017-12-04 10:46:30 0

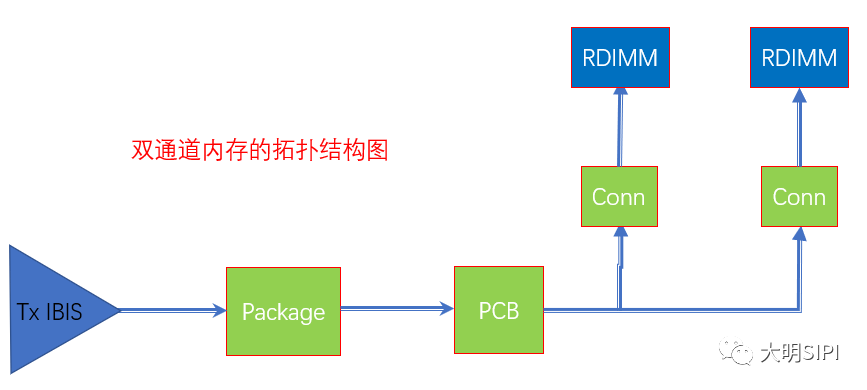

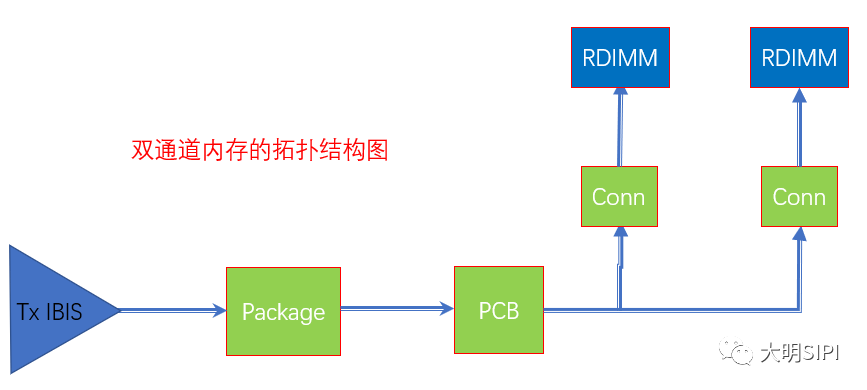

0 當(dāng)信號(hào)在高速PCB板上沿傳輸線傳輸時(shí)可能會(huì)産生信號(hào)完整性問(wèn)題。布線拓?fù)鋵?duì)信號(hào)完整性的影響,主要反映在各個(gè)節(jié)點(diǎn)上信號(hào)到達(dá)時(shí)刻不一致,反射信號(hào)同樣到達(dá)某節(jié)點(diǎn)的時(shí)刻不一致,所以造成信號(hào)質(zhì)量惡化。一般來(lái)講,星型拓?fù)浣Y(jié)構(gòu),可以通過(guò)控制同樣長(zhǎng)的幾個(gè)分支,使信號(hào)傳輸和反射時(shí)延一致,達(dá)到比較好的信號(hào)質(zhì)量。

2019-06-18 15:09:36 635

635 幅度到達(dá)接收端,就表明該電路具有較好的信號(hào)完整性。反之,就說(shuō)明出現(xiàn)了信號(hào)完整性問(wèn)題。在數(shù)字電路中,信號(hào)完整性問(wèn)題主要表現(xiàn)為振鈴、過(guò)沖、欠沖、時(shí)延、同步切換噪聲和地彈等現(xiàn)象。

2019-05-27 13:58:16 1753

1753

借助功能強(qiáng)大的Cadence公司SPEECTRAQuest仿真軟件,利用IBIS模型,對(duì)高速信號(hào)進(jìn)行信號(hào)完整性仿真分析是一種高效可行的分析方法,可以發(fā)現(xiàn)信號(hào)完整性問(wèn)題,根據(jù)仿真結(jié)果在信號(hào)完整性相關(guān)問(wèn)題上做出優(yōu)化的設(shè)計(jì),從而達(dá)到提高設(shè)計(jì)質(zhì)量,縮短設(shè)計(jì)周期的目的。

2019-05-20 15:25:37 1098

1098

當(dāng)前要?jiǎng)?chuàng)建高難度的電子產(chǎn)品,需要采取戰(zhàn)略性的方法來(lái)解決信號(hào)和電源完整性問(wèn)題。在 Layout 開(kāi)始之前提前研究敏感信號(hào)中存在的信號(hào)完整性問(wèn)題,有助于實(shí)施布線策略、端接方法和疊層選擇,并最終減少測(cè)試工作量、降低電路板設(shè)計(jì)遍數(shù)、并縮短設(shè)計(jì)時(shí)間。

2019-05-20 06:20:00 2527

2527

使用 HyperLynx? 可以輕松地查找并修復(fù) PCB 上的

信號(hào)完整性問(wèn)題。從 PCB Layout 導(dǎo)出設(shè)計(jì)后,您可以采用批量模式和/或交互模式運(yùn)行仿真,以查找

信號(hào)完整性問(wèn)題。內(nèi)置的端接器向?qū)?/div>

2019-05-16 06:22:00 3879

3879

在PCB信號(hào)完整性問(wèn)題可以很容易地定位和固定使用HyperLynx?。出口你的設(shè)計(jì)從PCB布局之后,可以以批處理方式運(yùn)行模擬和/或交互模式發(fā)現(xiàn)信號(hào)完整性問(wèn)題。內(nèi)置的終結(jié)者向?qū)Э梢?b class="flag-6" style="color: red">分析一個(gè)拓?fù)浜徒ㄗh

2019-10-12 07:08:00 2565

2565 今天的設(shè)計(jì)技術(shù),可以導(dǎo)致嚴(yán)重的信號(hào)完整性問(wèn)題如果處理不當(dāng)。墊,您可以運(yùn)行pre-layout分析來(lái)確定高速約束、層分層盤旋飛行,和終止策略。驗(yàn)證結(jié)果與布線后如果分析以確保設(shè)計(jì)滿足你所有的高需求,再被發(fā)送出去制造業(yè)。

2019-10-11 07:03:00 4609

4609 《信號(hào)完整性分析》作者以實(shí)踐專家的視角提出了造成信號(hào)完整性問(wèn)題的根源,特別給出了在設(shè)計(jì)前期階段的問(wèn)題解決方案。這是面向電子工業(yè)界的設(shè)計(jì)工程師和產(chǎn)品負(fù)責(zé)人的一本具有實(shí)用價(jià)值的參考書(shū),其目的在于幫助他們

2019-11-21 14:09:46 143

143 本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題? 信號(hào)完整性是指高速產(chǎn)品設(shè)計(jì)中由互連線引起的所有問(wèn)題。包括以下幾部分: 時(shí)序 噪聲 電磁干擾(EMI) 數(shù)據(jù)采樣

2020-09-18 11:01:48 4328

4328 在這里,我們將討論潛在的信號(hào)完整性問(wèn)題,它們的來(lái)源,理解它們的重要性,以及我們?nèi)绾?b class="flag-6" style="color: red">分析和解決這些問(wèn)題。關(guān)于電氣設(shè)計(jì),信號(hào)完整性應(yīng)該集中在兩個(gè)主要方面:定時(shí)和信號(hào)質(zhì)量。

2020-09-26 09:22:36 7239

7239 本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題?

2021-01-20 14:22:53 1011

1011

本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題?

信號(hào)完整性是指高速產(chǎn)品設(shè)計(jì)中由互連線引起的所有問(wèn)題。包括以下幾部分:

時(shí)序

噪聲

2022-02-09 16:14:50 996

996

本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題?

2021-01-23 08:45:50 28

28 本文主要介紹信號(hào)完整性是什么,信號(hào)完整性包括哪些內(nèi)容,什么時(shí)候需要注意信號(hào)完整性問(wèn)題?

信號(hào)完整性是指高速產(chǎn)品設(shè)計(jì)中由互連線引起的所有問(wèn)題。包括以下幾部分:

時(shí)序

噪聲

電磁干擾(EMI

2021-01-26 09:28:30 12

12 信號(hào)完整性問(wèn)題與PCB設(shè)計(jì)說(shuō)明。

2021-03-23 10:57:06 0

0 信號(hào)完整性與電源完整性的仿真(5V40A開(kāi)關(guān)電源技術(shù)參數(shù))-信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)!!!

2021-09-29 12:11:21 89

89 信號(hào)完整性與電源完整性分析信號(hào)完整性(SI)和電源完整性(PI)是兩種不同但領(lǐng)域相關(guān)的分析,涉及數(shù)字電路正確操作。在信號(hào)完整性中,重點(diǎn)是確保傳輸?shù)?在接收器中看起來(lái)就像 1(對(duì)0同樣如此)。在電源

2021-11-08 12:20:59 62

62 信號(hào)完整性分析第1版中文版國(guó)外電子與通信教程。本書(shū)全面論述了信號(hào)完整性問(wèn)題。它以入門式的切入方式使得讀者很容易認(rèn)識(shí)到物理互連影響電氣性能的實(shí)質(zhì)從而可以盡快掌握信號(hào)完整性設(shè)計(jì)技術(shù)。本書(shū)作者從實(shí)踐的角度指出了造成信號(hào)完整性問(wèn)題的根源特別給出了在設(shè)計(jì)前期階段的問(wèn)題解決方案。

2021-12-08 09:47:47 0

0 、持續(xù)時(shí)間和電壓幅度到達(dá)接收端時(shí),該電路就有很好的信號(hào)完整性。當(dāng)信號(hào)不能正常響應(yīng)時(shí),就出現(xiàn)了信號(hào)完整性問(wèn)題。信號(hào)完整性包含:1、波形完整性(Waveform integrity)2、時(shí)序完整性(Timi...

2022-01-07 15:38:32 0

0 高速電路信號(hào)完整性分析與設(shè)計(jì)—信號(hào)完整性仿真

2022-02-10 17:29:52 0

0 定義:信號(hào)完整性(Signal Integrity,簡(jiǎn)稱SI)是指在信號(hào)線上的信號(hào)質(zhì)量。差的信號(hào)完整性不是由某一單一因素導(dǎo)致的,而是板級(jí)設(shè)計(jì)中多種因素共同 引起的。當(dāng)電路中信號(hào)能以要求的時(shí)序、持續(xù)時(shí)間和電壓幅度到達(dá)接收端時(shí),該電路就有很好的信號(hào)完整性。當(dāng)信號(hào)不能正常響應(yīng)時(shí),就出現(xiàn)了信號(hào)完整性問(wèn)題。

2022-11-16 14:56:00 1778

1778 編者注:在分析信號(hào)完整性和電源完整性問(wèn)題時(shí)經(jīng)常會(huì)提到在時(shí)域中分析和在頻域中分析。不管是什么分析,分析都是同一個(gè)對(duì)象。因?yàn)橛械膯?wèn)題在時(shí)域中難以描述,比如能量損失,因?yàn)槟芰渴且粋€(gè)系統(tǒng)概念,很難對(duì)應(yīng)到物理

2023-05-14 10:45:12 540

540

時(shí)域是真實(shí)存在的域,頻域只是一個(gè)數(shù)學(xué)構(gòu)造,但頻域?qū)ξ覀?b class="flag-6" style="color: red">分析解決信號(hào)完整性問(wèn)題非常重要。那么如何將頻域和時(shí)域建立聯(lián)系方便的分析解決信號(hào)完整性問(wèn)題?因此引出了時(shí)域和頻域之間的紐帶--帶寬。對(duì)于信號(hào)完整性分析來(lái)說(shuō),帶寬實(shí)在是太重要了,這里再嘮叨嘮叨。

2023-06-14 10:20:06 1045

1045

業(yè)界經(jīng)常流行這么一句話:“有兩種設(shè)計(jì)師,一種是已經(jīng)遇到了信號(hào)完整性問(wèn)題,另一種是即將遇到信號(hào)完整性問(wèn)題”。固態(tài)硬盤作為一種高集成度的高時(shí)鐘頻率的硬件設(shè)備,信號(hào)完整性的重要性不言而喻。借著這句話本文主要跟大家聊下信號(hào)完整性的一些基本內(nèi)容。

2023-06-27 10:43:26 1112

1112

何為信號(hào)完整性的分析信號(hào)完整性包含:波形完整性(Waveformintegrity)時(shí)序完整性(Timingintegrity)電源完整性(Powerintegrity)信號(hào)完整性分析的目的就是

2023-08-17 09:29:30 3111

3111

分析儀和示波器進(jìn)行詳細(xì)比較,以便讀者能夠更好地理解它們之間的差別,同時(shí)也能夠了解如何根據(jù)自身的需要選擇適合的儀器。 邏輯分析儀和示波器的原理和功能 邏輯分析儀是一種可以捕捉和分析數(shù)字信號(hào)的設(shè)備。它通常被用于驗(yàn)證

2023-09-19 16:03:19 3126

3126 。本文將詳細(xì)討論邏輯分析儀和網(wǎng)絡(luò)分析儀的區(qū)別和聯(lián)系。 一、邏輯分析儀的定義 邏輯分析儀是一種電子測(cè)試儀器,可以用來(lái)測(cè)試、監(jiān)測(cè)和分析數(shù)字電路、模擬電路和微處理器的信號(hào)。它能夠顯示各種數(shù)字電子信號(hào)的高低電平、時(shí)序

2023-09-19 16:03:29 412

412 伯格丁_信號(hào)完整性分析

2022-12-30 09:21:05 8

8 信號(hào)傳輸并非嚴(yán)格針對(duì)網(wǎng)絡(luò)設(shè)計(jì)師,您的PCB設(shè)計(jì)可能會(huì)遇到相同類型的問(wèn)題。由于您無(wú)需費(fèi)力地?cái)[弄耳朵,因此防止電源完整性和信號(hào)完整性問(wèn)題對(duì)于您的PCB設(shè)計(jì)流暢且無(wú)靜電至關(guān)重要。

2023-11-08 17:25:01 344

344

導(dǎo)致信號(hào)失真、時(shí)序錯(cuò)誤、帶寬衰減等問(wèn)題,從而影響整個(gè)系統(tǒng)的可靠性和性能。為了解決信號(hào)完整性問(wèn)題,以下是一些必要的措施和方法。 首先,正確的信號(hào)完整性設(shè)計(jì)需要一個(gè)全面而準(zhǔn)確的信號(hào)完整性分析。這包括對(duì)布線、噪聲

2023-11-24 14:32:28 227

227 信號(hào)完整性(Signal Integrity,簡(jiǎn)稱SI)指的是信號(hào)線上的信號(hào)質(zhì)量。信號(hào)完整性差不是由單一因素造成的,而是由板級(jí)設(shè)計(jì)中多種因素共同引起的。破壞信號(hào)完整性的原因包括反射、振鈴、地彈、串?dāng)_等。隨著信號(hào)工作頻率的不斷提高,信號(hào)完整性問(wèn)題已經(jīng)成為高速PCB工程師關(guān)注的焦點(diǎn)。

2024-01-11 15:31:02 123

123 將詳細(xì)探討

邏輯分析儀探頭在保持?jǐn)?shù)字

信號(hào)完整性中的重要性和作用。 首先,

邏輯分析儀探頭的設(shè)計(jì)和制造對(duì)于保持?jǐn)?shù)字

信號(hào)的

完整性至關(guān)重要。數(shù)字

信號(hào)的

完整性是指

信號(hào)在傳輸過(guò)程中能夠保持原始性和精確性。而探頭作為

信號(hào)傳輸?shù)?/div>

2024-01-31 11:00:51 159

159

已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論