??????? 我在測(cè)試的時(shí)候,有些DC參數(shù)在同樣的條件下幾次測(cè)試的結(jié)果相差很大。不明白是為什么?

你使用的測(cè)試機(jī)臺(tái)是什么型號(hào)?測(cè)試的產(chǎn)品是屬于哪種?還有具體什么參數(shù),相差多少?

我們用的是credence kalos,測(cè)試的是memory,在測(cè)ICC時(shí),可能從幾百u(mài)A--幾十mA,實(shí)際值應(yīng)該在十幾mA。

credence kalos 我沒(méi)有用過(guò),不過(guò)ICC不穩(wěn)定原因有很多,如果其他同批產(chǎn)品沒(méi)有這個(gè)問(wèn)題的話可能是這個(gè)IC的問(wèn)題,可以先做下BENCHTEST,一般初期診斷是更換測(cè)試機(jī)臺(tái)或者用標(biāo)準(zhǔn)器件做比較。個(gè)人看法,僅供參考

benchtest是什么意思?還有就是同一顆IC多次測(cè)試他為什么會(huì)不穩(wěn)定。

狀態(tài)不穩(wěn)定可能是ICC不穩(wěn)定的原因 如果同一個(gè)芯片測(cè)試不穩(wěn)定而且誤差比較大,可從以下2方面去看:

1. 在測(cè)量時(shí)芯片所處的狀態(tài)是否穩(wěn)定。

2. 芯片的Input pin是否有Floating,Output pin是否在不停的翻轉(zhuǎn)

就是自己搭模擬電路測(cè)試,用電源,示波器...比較麻煩,而且需要APPLICATION BOARD,不知道你們有沒(méi)有。如果是同一顆不穩(wěn)定,一般會(huì)交給DA或者FA去分析,CURVE TRACE先吧。

電源干凈么? 先看一下電源腳是否干凈。然后換一下電流的range來(lái)看一下,最好用樣品校驗(yàn)一下。

電源很干凈,range應(yīng)該也沒(méi)有問(wèn)題,它有10mA左右的電流,用25mA的range。應(yīng)該沒(méi)有問(wèn)題,只是有時(shí)電流會(huì)變成100uA左右。樣品在10mA左右很穩(wěn)定。

如果是MEMORY測(cè)試,可以對(duì)其寫(xiě)相同的數(shù)據(jù)讓口上不翻轉(zhuǎn).然后看看會(huì)不會(huì)好點(diǎn).但是據(jù)你所說(shuō)樣品沒(méi)有問(wèn)題的話,可能這個(gè)問(wèn)題無(wú)解.

多比較

IDD (ICC)一般為一個(gè)器件的特征值,分布范圍不會(huì)很大,100uA-10mA的變化肯定是異常的。

1) 如果真的是樣品在10mA左右很穩(wěn)定, 那么設(shè)備及測(cè)試程序沒(méi)有問(wèn)題,產(chǎn)品的問(wèn)題可能很大,也不需要花費(fèi)很大腦筋,正如Code631兄說(shuō)的,交給DA/FA。

2)如果產(chǎn)品沒(méi)有問(wèn)題,則要確認(rèn)Hardware, Test Program方面的問(wèn)題

-〉 Hardware重點(diǎn)確認(rèn)Relay的動(dòng)作是否穩(wěn)定,可以在程序Meter讀之前設(shè)置斷點(diǎn),然后不停的Strobe Meter,看Meter值是否穩(wěn)定。這是驗(yàn)證Hardware動(dòng)作靜止的情況下,電流值是否跳動(dòng)。

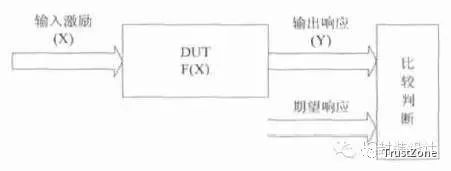

-〉 確認(rèn)Drive Pattern是否正常,IDD和Pattern有直接的關(guān)系,如果Pattern編寫(xiě)不正常,會(huì)造成DUT功耗不穩(wěn)定。

但是,如果標(biāo)準(zhǔn)樣品穩(wěn)定,就不必分析測(cè)試系統(tǒng)的問(wèn)題。

把DEVICE交給DA的結(jié)果無(wú)非就是確認(rèn)電路某個(gè)壞點(diǎn)或者觀察一下curve trace的圖形。基于樓主的描述,基本上可以確定是這顆產(chǎn)品的問(wèn)題,driving pattern和i/o的assignment應(yīng)該不會(huì)有錯(cuò),否則標(biāo)準(zhǔn)件不會(huì)過(guò)關(guān)。

如果要究其原因,我想大概要聯(lián)系到半導(dǎo)體物理的內(nèi)容了。電路參數(shù)的fluctuation造成的intermitent failure有可能是alpha粒子的轟擊或者電路內(nèi)部EMI(電磁輻射,如果片內(nèi)有感性器件的話)所造成的,我想工程上是不需要涉及到這個(gè)LEVEL的。

目前的解決方法就是請(qǐng)DA出一個(gè)報(bào)告,主要是benchtest和curve trace的報(bào)告,觀察在靜態(tài)(無(wú)relay動(dòng)作下)條件下ICC/VCC的曲線特征。做到這一步也就可以了。

測(cè)試穩(wěn)定性關(guān)系到你本身產(chǎn)品的性能、測(cè)試方法、還有硬件(設(shè)備、Test Board)。

1、測(cè)試不穩(wěn)定的參數(shù)是否僅有VOUT一項(xiàng)?(占空比,頻率?VOUT其它電壓條件的如何?)

2、尋找測(cè)試結(jié)果的分布規(guī)律,是否變動(dòng)很大?還是總是偏大/偏小?

3、你的參數(shù)測(cè)試方法?使用哪些硬件資源,DUT外圍器件如何?

不知道你使用的Test Board電路如何?

因?yàn)?576是開(kāi)關(guān)電路,測(cè)試電路的EMI(電磁干擾)問(wèn)題尤為重要。

- 輸入、輸出端的連線要盡量短

- 使用單點(diǎn)接地方式

- 是否使用的是肖特基二極管1N5822(或者快恢復(fù)二極管)。這點(diǎn)往往被工程師或略,常用1N4XXX等普通整流/開(kāi)關(guān)管代替,這樣會(huì)造成EMI增大,輸出效率降低,是不穩(wěn)定的一個(gè)禍因。

以前我處理過(guò)LM/MC34063,也是遇到測(cè)試穩(wěn)定性差的問(wèn)題。

看看你的pattern和電源濾波電容有沒(méi)有問(wèn)題

ICC應(yīng)該讓chip不停的run,那么你的pattern應(yīng)該是loop的,如果loop的首尾連接不好就可能出現(xiàn)這樣的問(wèn)題

另外,測(cè)試儀也是個(gè)問(wèn)題,你可以反復(fù)測(cè)試幾個(gè)DUT,看看有什么規(guī)律沒(méi)有Pin有沒(méi)有I/O類型的,如果有外面結(jié)法是否應(yīng)該檢查一下內(nèi)部有沒(méi)有電容,charge pump一類的功耗元件

如果都不是,就要看看版圖or加工了,是否內(nèi)部有虛短的東西,這個(gè)比較難分析了

也就是TL431吧?3PIN(TO92/8SOP)Voltage Reference,我們生產(chǎn)過(guò)。你能肯定是測(cè)試還是FAB的問(wèn)題?30ea是否為真的不良,有沒(méi)有驗(yàn)證過(guò)?

查連線吧

因?yàn)樵贔T時(shí)會(huì)有Handler的接觸電阻和Handler和Tester通訊的cable的電阻.所以建議用Socket將這些Fail的芯片直接在Tester上測(cè),如果OK就查連線吧.

SPEC Limit是多少?

首先,每個(gè)管芯(PASS的)測(cè)試時(shí),Vout是否十分穩(wěn)定,偏差是否在+-10mv之內(nèi),如果是,那么你CP和FT是否同一個(gè)測(cè)試系統(tǒng),或者在CP的探針卡上和DUT BOARD 上同時(shí)用Socket驗(yàn)證一個(gè)管芯!

要測(cè)到所有的命令,寄存器和堆棧.那你就要在設(shè)計(jì)時(shí)保證這些是可測(cè)的.即可以通過(guò)測(cè)試模式訪問(wèn)到這些寄存器和堆棧.因?yàn)槭歉咚?a target="_blank">CPU所以時(shí)間不是問(wèn)題,只是寫(xiě)Pattern的人比較累.

ICC測(cè)不穩(wěn)也有可能是測(cè)試模塊有自激引起

有的時(shí)候樣品能通過(guò),但芯片不通過(guò),這有兩中可能:1、芯片做的有點(diǎn)問(wèn)題,芯片本身會(huì)存在自激;2、測(cè)試模塊也可能有輕微自激,可以用示波器在輸出端看一下波形既可,當(dāng)然輸入端不要接信號(hào)

看看有沒(méi)有交流成份存在

雖然萬(wàn)用表可以只測(cè)直流部分,但是在高速測(cè)試時(shí)

交流或其他波動(dòng)對(duì)測(cè)試直流的影響非常大

建議用示波器看看是否存在交流成份

如果有,是難以測(cè)準(zhǔn)的

是否用示波器的交流檔去看有沒(méi)有交流電流?做icc測(cè)試時(shí)速度應(yīng)該不算很快,peroid = 100ns, delay 100ms后去測(cè),應(yīng)該可以了吧

你可以多設(shè)幾個(gè)采樣點(diǎn)(SAMPLE & AVERAGE),因?yàn)槟愕牟蓸狱c(diǎn)要是在翻轉(zhuǎn)邊沿上則會(huì)很大,否則可能很小。

1、遮光問(wèn)題。半導(dǎo)體器件受光線影響巨大(封裝后光線影響徹底消失)

2、濕度問(wèn)題。晶園測(cè)試環(huán)境的濕度異常的話,測(cè)出來(lái)的參數(shù)根本就不能說(shuō)明問(wèn)題

3、封裝本身也會(huì)使參數(shù)有些漂移(中心值漂移或離散度加大),根本原因還是封裝前后環(huán)境變了。而半導(dǎo)體器件跟測(cè)試環(huán)境息息相關(guān)。

LM1875是音頻功放,測(cè)試的參數(shù)和方法也與通用運(yùn)放不一樣,應(yīng)該按照一般功率放大器的方法進(jìn)行。可以根據(jù)DATASHEET確定測(cè)試參數(shù),測(cè)試電路也是根據(jù)應(yīng)用電路和測(cè)試方法共同確定。

一般在單電源供電時(shí)得使用電容耦合,為了消除1/2VCC DC偏置。但是,應(yīng)用工程師一般不希望使用這個(gè)電容,特別在HiFi情況下,會(huì)考慮電容帶來(lái)的失真。所以他們不得不使用對(duì)稱雙電源。

在測(cè)試時(shí),如果使用電容耦合,THD至少不同程度地受電容性能的影響,特別如果電容出問(wèn)題,測(cè)試就會(huì)出錯(cuò)。所以,建議能夠不用電容最好。

請(qǐng)問(wèn)用TL494控制直流180W有刷電機(jī)。電機(jī)初始階段為何有噪音,怎樣消除?謝謝。

IC出廠時(shí)都經(jīng)過(guò)了100%測(cè)試的,測(cè)試通過(guò)的芯片參數(shù)都在標(biāo)準(zhǔn)值以內(nèi)。良莠不齊的情況如果在Datasheet列出的參數(shù)表以外,就是不合格品(正宗廠家出貨不會(huì)出現(xiàn)的)。客戶對(duì)芯片測(cè)試投入太大,我的看法是沒(méi)有必要。不知道你們用的是什么片子?怎會(huì)出現(xiàn)這種情況?

FE是什么工作?學(xué)要什么準(zhǔn)備知識(shí)?職業(yè)發(fā)展前途如何? 問(wèn)題如題目樓主是紐卡時(shí)而大學(xué)~~^_^方便看英超了。

FE=failure analysis, 屬于DA的一種,不合格產(chǎn)品的分析,手段包括物理切開(kāi)后用電子顯微鏡或光學(xué)顯微鏡觀察,還有用BENCHTEST測(cè)試電器性能,如VI,IDD,等等。

DFT (design for test設(shè)計(jì)IC時(shí),把IC可測(cè)試性考慮進(jìn)來(lái),以達(dá)到將來(lái)易測(cè)試的目的的一個(gè)步驟)is including: Scan Chain(對(duì)時(shí)序電路的一種測(cè)試方法,在電路內(nèi)部建立一個(gè)的測(cè)試環(huán)路), Boundary Scan(同上,測(cè)試環(huán)路過(guò)程), Logic BIST (邏輯電路內(nèi)建測(cè)試)and Memory BIST(存儲(chǔ)電路內(nèi)建測(cè)試).

Test Pattern Generation(測(cè)試圖形向量產(chǎn)生): Deterministic Pattern(定性圖形向量), Random Pattern or ATPG(自動(dòng)測(cè)試向量產(chǎn)生的隨機(jī)圖形向量)

Test Pattern Compression(測(cè)試圖形向量壓縮): Fault Simulation(錯(cuò)誤模擬), even with MISR(MISR=multi input Shift Register).

reaking :先問(wèn)題問(wèn)題吧! Code631老兄,可做過(guò)chipset的測(cè)試嗎?

code631 :chipset應(yīng)該不難吧,純LOGIC的東西。

reaking :北橋基本上是屬于純邏輯的東西,但是南橋好像并不如此。而且現(xiàn)在速度越來(lái)越快,好像問(wèn)題也就越來(lái)越多。能講一下如何深入地了解chipset嗎?

fuqipan1 哪里可以找到測(cè)試報(bào)告之類的資料!特別是pwm的!謝謝!

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論