16日,三星電子宣布在基于EUV的高級節點方面取得了重大進展,包括7nm批量生產和6nm客戶流片,以及成功完成5nm FinFET工藝的開發。 三星電子宣布其5納米(nm)FinFET工藝技術的開發

2019-04-18 15:48:47 6010

6010 全球電子設計創新企業Cadence設計系統公司日前宣布其與TSMC在3D IC設計基礎架構開發方面的合作。

2012-06-11 09:47:43 1071

1071 新思科技公司(Synopsys)在過去五年多與行業領導者合作共同開發了對FinFET技術的支持,通過提供經生產驗證的設計工具與IP來推進對FinFET技術的采用。

2013-02-19 10:42:54 823

823 ARM (LSE:ARM; Nasdaq: ARMH) 和Cadence (NASDAQ: CDNS) 今天宣布合作細節,揭示其共同開發首款基于臺積電16納米FinFET制程的ARM?Cortex?-A57處理器,實現對16納米性能和功耗縮小的承諾。

2013-04-07 13:46:44 1509

1509 Altera公司與臺積公司今日共同宣布在55納米嵌入式閃存 (EmbFlash) 工藝技術上展開合作,Altera公司將采用臺積公司的55納米前沿嵌入式閃存工藝技術生產可程序器件,廣泛支持汽車及工業等各類市場的多種低功耗、大批量應用。

2013-04-16 09:05:09 925

925 Cadence系統芯片開發工具已經通過臺積電(TSMC) 16納米 FinFET制程的設計參考手冊第0.1版與 SPICE 模型工具認證,客戶現在可以享用Cadence益華電腦流程為先進制程所提供的速度、功耗與面積優勢。

2013-06-06 09:26:45 1236

1236 昨日臺積電官方宣布,16nm FinFET Plus(簡稱16FF+)工藝已經開始風險性試產。16FF+是標準的16nm FinFET的增強版本,同樣有立體晶體管技術在內,號稱可比20nm SoC平面工藝性能提升最多40%,或者同頻功耗降低最多50%。

2014-11-14 09:31:58 2127

2127 在國際電子電路研討會大會(ISSCC)上,三星展示了采用10納米FinFET工藝技術制造的300mm晶圓,這表明三星10納米FinFET工藝技術最終基本定型。

2015-05-28 10:25:27 1715

1715 12納米領先性能(12LP)的FinFET半導體制造工藝。該技術預計將提高當前代14納米 FinFET產品的密度和性能,同時滿足從人工智能、虛擬現實到高端智能手機、網絡基礎設施等最具計算密集型處理需求的應用。 這項全新的12LP技術與當前市場上的16 /14納米 FinFET解決方案相比,電路密度提高

2017-09-25 16:12:36 8666

8666 據臺灣經濟日報最新消息,聯電(2303)與下一代ST-MRAM(自旋轉移力矩磁阻RAM)領導者美商Avalanche共同宣布,合作技術開發MRAM及相關28納米產品;聯電即日起透過授權,提供客戶具有成本效益的28納米嵌入式非揮發性MRAM技術。

2018-08-09 10:38:12 3129

3129 8月30日,中芯國際發布2018年中期業績,收入同比增長11.5%至17.22億美元;毛利同比增長5.6%至4.38億美元。中芯國際在14納米FinFET技術開發上獲得重大進展。中芯國際的第一代FinFET技術研發已進入客戶導入階段。

2018-08-31 14:44:33 5140

5140 晶體管制造工藝在近年來發展得不是非常順利,行業巨頭英特爾的主流產品長期停滯在14nm上,10nm工藝性能也遲遲得不到改善。臺積電、三星等巨頭雖然在積極推進7nm乃至5nm工藝,但是其頻率和性能

2020-07-07 11:38:14

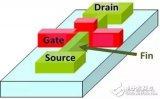

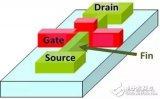

增強;同時也極大地減少了漏電流的產生,這樣就可以和以前一樣繼續進一步減小Gate寬度。目前三星和臺積電在其14/16nm這一代工藝都開始采用FinFET技術。圖6:Intel(左:22nm)和Samsung(右:14nm)Fin鰭型結構注:圖3、圖6的圖片來于網絡。

2017-01-06 14:46:20

臺積電0.18工藝電源電壓分別是多少?是1.8v跟3.3v嗎?

2021-06-25 06:32:37

臺積電宣布5nm基本完工開始試產:面積縮小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

有機會“獨吞”A7代工訂單。 臺積電作為全球規模最大的專業集成電路制造公司,其技術優勢的領先,在業界可謂屈指可數。臺積電積極開發20納米制程,花旗環球證券指出,在技術領先MAX3232EUE+T優勢下,未來1

2012-09-27 16:48:11

臺積電正在大量生產用于蘋果iPhone8手機的10nm A11處理器。消息稱,蘋果可能在下個月初正式發布iPhone 8,但是具體發貨日期仍然不確定。 據悉,臺積電已經采用10nm FinFET

2017-08-17 11:05:18

EMC設計、工藝技術基本要點和問題處理流程推薦給大家參考。。

2015-08-25 12:05:04

技術開發成功,同時透露會朝第二代的 FinFET 技術開發。若***一舉朝 7 納米前進,將會成為全球第四家 7 納米技術供應商,與英特爾、臺積電、三星分庭抗禮。同時,華為海思的麒麟980也搶先發布,首款

2018-09-05 14:38:53

Sic mesfet工藝技術研究與器件研究針對SiC 襯底缺陷密度相對較高的問題,研究了消除或減弱其影響的工藝技術并進行了器件研制。通過優化刻蝕條件獲得了粗糙度為2?07 nm的刻蝕表面;犧牲氧化

2009-10-06 09:48:48

蘋果晶圓代工龍頭臺積電16納米鰭式場效晶體管升級版(FinFET Plus)將在明年1月全產能量產,搭配整合型扇出晶圓尺寸封裝(InFO WLP)的系統級封裝(SiP)技術,在x86及ARM架構64位

2014-05-07 15:30:16

:為把openEuler 打造成全球頂尖的技術軟件,我們不僅僅要和國內的開發者社區和基金會合作,還要和國際上先進的開發者社區和基金會合作,讓他們愿意參與進來,共創 openEuler 社區。我愿意

2022-07-29 10:11:11

,未來就要看競爭對手的制程技術能否趕得上腳步。 近期高通與臺積電持續緊密合作,業界傳出在最先進的7納米制程技術上,臺積電因為技術開發領先三星電子(Samsung Electronics),可望拿回高通7

2017-09-22 11:11:12

了高通的訂單。之后,中芯國際憑借極具競爭力的價格從Globalfoundries手中奪走了訂單,成為高通電源管理芯片的主要合作伙伴。我們知道,在高通的幫助下,中芯國際實現了28nm工藝量產,而且還加快14nm硅片的量產。由于產能、價格及新芯片技術的原因,此次高通將電源管理芯片交給了臺積電生產。

2017-09-27 09:13:24

。這場戰役兩家大廠互有消長,首先是三星的14nm較臺積電的16nm搶先半年投入量產,因兩家大廠的鰭式晶體管(FinFET)設計也確有雷同之處,后續又衍生了競業禁止官司訴訟等故事,無論如何,最終臺積電還是

2018-06-14 14:25:19

Nano-Proprietary旗下的Applied Nanotech公司與Funai Electric先進應用技術研究所日前宣布,雙方將針對一個研究項目進行合作,共同開發基于酶涂層碳納米

2018-11-19 15:20:44

CPLD技術在PCI總線開關中的應用使用CPLD技術開發PCI板卡有什么優點

2021-04-08 06:47:28

PCB部件使用PI膜作為柔性芯板,并覆蓋聚酰亞胺或丙烯酸膜。粘合劑使用低流動性預浸料,最后將這些基材層壓在一起以制成剛撓性PCB。剛柔性PCB制造工藝技術的發展趨勢:未來,剛柔結合PCB將朝著超薄,高密度

2019-08-20 16:25:23

業界對哪種半導體工藝最適合某一給定應用存在著廣泛的爭論。雖然某種特殊工藝技術能更好地服務一些應用,但其它工藝技術也有很大的應用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-07-05 08:13:58

業界對哪種半導體工藝最適合某一給定應用存在著廣泛的爭論。雖然某種特殊工藝技術能更好地服務一些應用,但其它工藝技術也有很大的應用空間。像CMOS、BiCMOS、砷化鎵(GaAs)、磷化銦(InP

2019-08-20 08:01:20

交給代工廠來開發和交付。臺積電是這一階段的關鍵先驅。

半導體的第四個時代——開放式創新平臺

仔細觀察,我們即將回到原點。隨著半導體行業的不斷成熟,工藝復雜性和設計復雜性開始呈爆炸式增長。工藝技術

2024-03-13 16:52:37

各類常用工藝庫臺積電,中芯國際,華潤上華

2015-12-17 19:52:34

工藝技術的演進遵循摩爾定律,這是這些產品得以上市的主要促成因素。對整個行業來說,從基于大體積平面晶體管向FinFET三維晶體管的過渡是一個重要里程碑。這一過渡促使工藝技術經過了幾代的持續演進,并且減小

2019-07-17 06:21:02

如何利用TI DLP Pico 技術開發頭戴式顯示應用?為什么要選擇DLP Pico技術開發HMD應用?

2021-06-01 06:52:55

一半,而性能提高兩倍。通過選擇一個高性能低功耗的工藝技術,一個覆蓋所有產品系列的、統一的、可擴展的架構,以及創新的工具,賽靈思將最大限度地發揮 28 納米技術的價值, 為客戶提供具備 ASIC 級功能

2019-08-09 07:27:00

如何通過軟件無線電的架構加速無線技術的開發與測試?如何應對無線標準和技術的快速更新?

2021-05-07 07:05:26

如何提高多層板層壓品質在工藝技術

2021-04-25 09:08:11

本帖最后由 華強芯城 于 2023-3-17 09:16 編輯

晶圓代工巨頭——臺積電近日傳出漲價20%的消息,業內轟動。這是臺積電繼2020年底上漲超10%之后,一年之內,又一次的大幅上漲

2021-09-02 09:44:44

的工藝技術可用于晶圓凸起,每種技術有各自的優缺點。其中金線柱焊接凸點和電解或化學鍍金焊接凸點主要用于引腳數較少的封裝應用領域包括玻璃覆晶封裝、軟膜覆晶封裝和RF模塊。由于這類技術材料成本高、工序

2011-12-01 14:33:02

的小珠子,使其最后形成一個10X5比例的長方形。從這個實驗不難看出,要達成這個目標非常不容易,由此可以了解到,各大廠面臨的困境有多么艱難。三星和臺積電都在完成14 納米、16 納米 FinFET 的量產

2016-06-29 14:49:15

的長方形。從這個實驗不難看出,要達成這個目標非常不容易,由此可以了解到,各大廠面臨的困境有多么艱難。三星和臺積電都在完成14 納米、16 納米 FinFET 的量產,并以此為資本爭奪下一代iPhone

2016-12-16 18:20:11

穿戴電子開發項目,可技術合作共同開發!各位網友大家好,明年是穿戴式電子元年,google glass 年底上市注定會刮起一陣電子穿戴風,穿戴電子市場有很大的發展空間,必定會為合作伙伴帶來機會,我們

2013-06-29 17:35:47

,所以只能以舊工藝(16nm制程)制造A10處理器。除此之外,臺積電還將獨家代工重大變化的2017年版iPhone采用的A11處理器。據稱A11芯片將采用10納米FinFET工藝,最早有望于明年二季度

2016-07-21 17:07:54

生產。如果臺積電真的能夠完全按照這一時間展開工作的話,那么就將使該公司徹底走在了芯片制造領域的最前端。 目前,業內設備制造廠商大多剛剛開始擁抱14納米芯片工藝,蘋果最新的iPhone 6s系列就是

2016-01-25 09:38:11

請詳細敘述腐蝕工藝工段的工藝流程以及整個前道的工藝技術

2011-04-13 18:34:13

中芯國際將45納米工藝技術延伸至40納米以及55納米

上海2009年10月14日電 -- 中芯國際集成電路制造有限公司(“中芯國際”,紐約

2009-10-15 08:22:44 793

793 中芯國際(SMIC)和Cadence 共同推出用于65納米的低功耗解決方案Reference Flow 4.0

完全集成的能效型流程令快速、輕松地設計低功耗尖端器件成為可能

2009-10-31 07:48:01 1228

1228 中芯國際(SMIC)和Cadence共同推出用于65納米的低功耗解決方案Reference Flow 4.0

全球電子設計創新領先企業Cadence設計系統公司今天宣布推出一款全面的低功耗設計流程,面向

2009-11-04 17:05:17 589

589 高通攜手TSMC,繼續28納米工藝上合作

高通公司(Qualcomm Incorporated)與其專業集成電路制造服務伙伴-TSMC前不久日共同宣布,雙方正在28納米工藝技術進行密切合作。此

2010-01-13 08:59:23 910

910 新思科技與中芯國際合作推出用于中芯65納米低漏電工藝技術的、獲得USB標志認證的DesignWareUSB 2.0 nanoPHY

通過芯片驗證的DesignWare PHY IP

2010-05-20 17:39:09 588

588 據外國媒體報道,IBM和ARM計劃加強移動電子市場合作的同時,還會共同合作提高14納米半導體技術。

2011-01-19 08:09:55 330

330 中國頂尖IC設計公司已經采用了28納米尖端技術開發芯片,而9.2% 本地無晶圓廠半導體公司亦采用先進的45納米或以下的工藝技術進行設計及大規模量產。

2011-09-07 11:23:50 1556

1556 中國頂尖設計公司已經采用28納米尖端技術開發芯片,而本地9.2%無晶圓廠半導體公司亦采用先進的45納米或以下的工藝技術進行設計及大規模量產

2011-09-13 09:00:40 3212

3212 Crocus科技和中芯國際正式簽署合作技術開發和晶圓制造協議。共同研發高溫MLU的應用技術。

2011-12-09 19:04:21 637

637 Cadence與三星的合作為移動消費電子產品帶來了新的工藝進展,使得20納米及未來工藝節點設計成為可能。

2012-06-10 10:43:54 984

984 隨著芯片微縮,開發先進工藝技術的成本也越來越高。TSMC對外發言人孫又文表示,臺積電會繼續先進工藝技術節點的投入和開發,今年年底臺積電將推出20nm工藝

2012-08-30 14:34:30 1782

1782 全球電子設計創新領先企業Cadence設計系統公司日前宣布TSMC已選擇Cadence解決方案作為其20納米的設計架構。Cadence解決方案包括Virtuoso定制/模擬以及Encounter RTL-to-Signoff平臺。

2012-10-22 16:48:03 909

909 該14納米產品體系與芯片是ARM、Cadence與IBM之間在14納米及以上高級工藝節點上開發系統級芯片(SoC)多年努力的重要里程碑。使用FinFET技術以14納米標準設計的SoC能夠大幅降低功耗。 這

2012-11-16 14:35:55 1270

1270 新思科技公司日前宣布:該公司與三星在FinFET技術上的多年合作已經實現了一個關鍵性的里程碑,即采用三星的14LPE工藝成功實現了首款測試芯片的流片

2013-01-09 12:11:31 1062

1062 ,采用臺積公司先進的16納米FinFET (16FinFET)工藝打造擁有最快上市、最高性能優勢的FPGA器件。

2013-05-29 18:21:14 869

869 日前,聯華電子與SuVolta公司宣布聯合開發28納米工藝技術,該工藝將SuVolta的SuVolta的Deeply Depleted Channel晶體管技術集成到聯華電子的28納米High-K/Metal Gate高效能移動工藝。

2013-07-25 10:10:52 1049

1049 全球電子創新設計Cadence公司與上海華力微電子,15日共同宣布了華力微電子基于Cadence Encounter數字技術交付55納米平臺的參考設計流程。華力微電子首次在其已建立55納米工藝上實現了從RTL到GDSII的完整流程。

2013-08-16 11:08:11 1383

1383 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)與上海華力微電子有限公司,今天共同宣布華力微電子基于Cadence ? Encounter? 數字技術交付出55納米平臺的參考設計流程。

2013-08-16 12:02:40 1445

1445 益華電腦宣布,晶圓代工業者GLOBALFOUNDRIES已經認證Cadence實體驗證系統適用于65nm至14nm FinFET制程技術的客制/類比、數位與混合訊號設計實體signoff。同時

2014-03-25 09:33:50 862

862 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)今天宣布,立即推出基于臺積電16納米FinFET制程的DDR4 PHY IP(知識產權)。

2014-05-21 09:44:54 1769

1769 全球知名電子設計創新領先公司Cadence設計系統公司 (NASDAQ: CDNS),今日宣布臺積電采用了Cadence?16納米FinFET單元庫特性分析解決方案。

2014-10-08 19:03:22 1594

1594 設計參考手冊(Design Rule Manual,DRM) 與SPICE認證,相比于原16納米FinFET制程,可以使系統和芯片公司通過此新工藝在同等功耗下獲得15%的速度提升、或者在同等速度下省電30%。

2014-10-08 19:10:45 663

663 美國加州圣何塞(2014年9月26日)-全球知名的電子設計創新領導者Cadence設計系統公司(NASDAQ: CDNS)今日宣布為臺積電16納米FinFET+ 制程推出一系列IP組合。

2014-10-08 19:19:22 919

919 三星于2015年第一季度發布了半導體芯片行業首款采用14nmLPE (Low-Power Early) 工藝量產的Exynos 7 Octa處理器,成為FinFET邏輯制程上的行業引領者。

2016-01-15 17:12:47 927

927 2016年3月22日,中國上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS)今日宣布,用于10納米 FinFET工藝的數字、定制/模擬和簽核工具通過臺積電(TSMC)V1.0設計參考手冊(DRM)及SPICE認證。

2016-03-22 13:54:54 1026

1026 2016年5月19日,北京訊——ARM今日發布了首款采用臺積電公司(TSMC)10納米FinFET工藝技術的多核 64位 ARM?v8-A 處理器測試芯片。仿真基準檢驗結果顯示,相較于目前常用于多款頂尖智能手機計算芯片的16納米FinFET+工藝技術,此測試芯片展現更佳運算能力與功耗表現。

2016-05-19 16:41:50 662

662 確保連續四代全可編程技術及多節點擴展的領先優勢四代先進工藝技術和3D IC以及第四代FinFET技術合作 2015年5月28日, 中國北京 - All Programmable 技術和器件的全球領先

2017-02-09 03:48:04 198

198 2017年4月18日,中國上海 – 楷登電子(美國Cadence公司,NASDAQ: CDNS)今日正式發布針對7nm工藝的全新Virtuoso? 先進工藝節點平臺。通過與采用7nm FinFET

2017-04-18 11:09:49 1165

1165 三星10納米工藝技術公告:全球領先的三星電子先進的半導體元器件技術正式宣布,其第二代10納米(nm)FinFET工藝技術,10LPP(Low Power Plus)已經合格并準備就緒用于批量生產。

2017-05-03 01:00:11 580

580 2017年6月2日,上海——楷登電子(美國 Cadence 公司,NASDAQ: CDNS) 今日宣布其數字、簽核與定制/模擬工具成功在三星電子公司7LPP和8LPP工藝技術上實現。較前代高階工藝

2017-06-02 16:04:34 1237

1237 賽靈思、Arm、Cadence和臺積公司今日宣布一項合作,將共同構建首款基于臺積7納米FinFET工藝的支持芯片間緩存一致性(CCIX)的加速器測試芯片,并計劃在2018年交付

2017-09-23 10:32:12 4003

4003 Technology (12FFC) 和最新版本 7nm FinFET Plus 工藝的認證。Nitro-SoCTM 布局和布線系統也通過了認證,可以支持 TSMC 的 12FFC 工藝技術。

2017-10-11 11:13:42 2372

2372 在2011年初,英特爾公司推出了商業化的FinFET,使用在其22納米節點的工藝上[3]。從IntelCorei7-3770之后的22納米的處理器均使用了FinFET技術。由于FinFET具有

2018-07-18 13:49:00 119524

119524

楷登電子(美國 Cadence 公司)今日正式公布其與臺灣積體電路制造股份有限公司(TSMC)全新12nm FinFET緊湊型(12FFC)工藝技術開發的合作內容。憑借Cadence 數字

2018-05-08 11:07:00 1422

1422 Synopsys設計平臺用于高性能、高密度芯片設計 重點: Synopsys設計平臺獲得TSMC工藝認證,支持高性能7-nm FinFET Plus工藝技術,已成功用于客戶的多個設計項目。 針對

2018-05-17 06:59:00 4461

4461 中芯國際14納米FinFET技術獲得重大進展 8月9日,中芯國際公布了在14納米FinFET技術開發上獲得的重大進展。第一代FinFET技術研發已進入客戶導入階段。除了28納米PolySiON和HKC,28納米HKC+技術開發也已完成。28納米HKC持續上量,良率達到業界水平。

2018-08-18 10:31:00 3773

3773 外,在技術研發方面,中芯國際表示,第一代 FinFET 14 納米技術進入客戶驗證階段,產品可靠度與良率已進一步提升。同時,12 納米的技術開發也開始有所突破。

2019-02-18 17:03:10 3076

3076

4月16日,三星官網發布新聞稿,宣布已經完成5納米FinFET工藝技術開發,現已準備好向客戶提供樣品。

2019-04-16 17:27:23 3008

3008 UltraScale+ 器件系列以低功耗半導體工藝(TSMC 16 納米FinFET+)為基礎,與 7 系列 FPGA 及 SoC 相比,能將整體器件級電源節省達 60%。架構改進。

2019-08-01 15:46:33 1252

1252 目前從全球范圍來說,也就只有臺積電和三星這兩家能做到5納米工藝以下了。6月29日晚間,據外媒報道,三星宣布其基于柵極環繞型 (Gate-all-around,GAA) 晶體管架構的3nm工藝技術已經

2021-07-02 11:21:54 2254

2254 Cadence 和 TSMC 聯手進行 N3 和 N4 工藝技術合作, 加速賦能移動、人工智能和超大規模計算創新 雙方共同客戶現可廣泛使用已經認證的 N3 和 N4 流程 PDK 進行設計 完整

2021-10-26 15:10:58 1928

1928 工藝技術的FINFLEX架構認證 此外,該認證也可擴展到臺積電N4工藝技術 Ansys宣布Ansys電源完整性解決方案榮獲臺積電FINFLEX創新架構以及N4工藝技術認證,持續深化與臺積電的長期技術合作

2022-11-17 15:31:57 696

696 來源:Cadence楷登 2023年4月26日,楷登電子近日宣布基于臺積電 3nm(N3E)工藝技術的 Cadence? 16G UCIe? 2.5D 先進封裝 IP 成功流片。該 IP 采用

2023-04-27 16:35:40 453

453

,包括最新的 N3E 和 N2 工藝技術。這一新的生成式設計遷移流程由 Cadence 和臺積電共同開發,旨在實現定制和模擬 IC 設計在臺積電工藝技術之間的自動遷移。與人工遷移相比,已使用該流程的客戶成功地將遷移時間縮短了 2.5 倍。

2023-05-06 15:02:15 801

801 恩智浦和臺積電聯合開發采用臺積電16納米FinFET技術的嵌入式MRAM IP? 借助MRAM,汽車廠商可以更高效地推出新功能,加速OTA升級,消除量產瓶頸 恩智浦計劃于2025年初推出采用該技術

2023-05-26 20:15:02 396

396 流程現已通過 Intel 16 FinFET 工藝技術認證,其 Design IP 現可支持 Intel Foundry Services(IFS)的此工藝節點。 與此同時,Cadence 和 Intel 共同發布

2023-07-14 12:50:02 381

381

Cadence近日宣布,其數字和定制/模擬流程在Intel的18A工藝技術上成功通過認證。這一里程碑式的成就意味著Cadence的設計IP將全面支持Intel的代工廠在這一關鍵節點上的工作,并提

2024-02-27 14:02:18 160

160

電子發燒友App

電子發燒友App

評論