本文介紹了EDA技術(shù)主要特點(diǎn)和功能,并對(duì)將EDA技術(shù)引入到數(shù)字電路設(shè)計(jì)工作方案進(jìn)行了探討。##EDA技術(shù)在數(shù)字系統(tǒng)中應(yīng)用以基于A(yíng)lteraEPM7128SLC84-15芯片和MAX PlusII 10.0軟件平臺(tái)數(shù)字鐘設(shè)計(jì)為例,討論EDA技術(shù)在數(shù)字系統(tǒng)中具體應(yīng)用。

2014-01-24 14:38:14 3494

3494

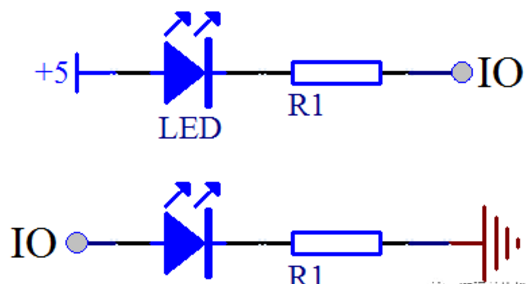

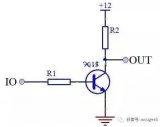

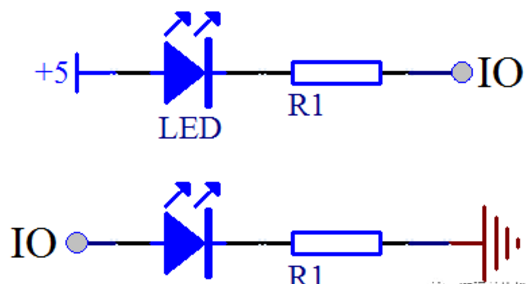

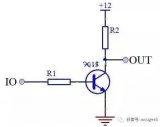

三極管在數(shù)字電路里的開(kāi)關(guān)特性,最常見(jiàn)的應(yīng)用有 2 個(gè):一個(gè)是控制應(yīng)用,一個(gè)是驅(qū)動(dòng)應(yīng)用。

2018-01-07 09:44:10 22758

22758

和專(zhuān)用集成電路(ASIC)逐漸取代了通用全硬件LSI電路,可編程邏輯器件(PLD)尤其是現(xiàn)場(chǎng)可編程邏輯器件(FPLD)被大量地應(yīng)用在A(yíng)SIC的制作中,在可編程集成電路的開(kāi)發(fā)過(guò)程中,EDA技術(shù)的出現(xiàn)帶來(lái)了電子系

2008-06-24 13:47:25

和專(zhuān)用集成電路(ASIC)逐漸取代了通用全硬件LSI電路,可編程邏輯器件(PLD)尤其是現(xiàn)場(chǎng)可編程邏輯器件(FPLD)被大量地應(yīng)用在A(yíng)SIC的制作中,在可編程集成電路的開(kāi)發(fā)過(guò)程中,EDA技術(shù)的出現(xiàn)帶來(lái)了電子系

2008-06-12 10:01:04

師可以從概念、算法、協(xié)議等開(kāi)始設(shè)計(jì)電子系統(tǒng),大量工作可以通過(guò)計(jì)算機(jī)完成,并可以將電子產(chǎn)品從電路設(shè)計(jì)、性能分析到設(shè)計(jì)出IC版圖或PCB版圖的整個(gè)過(guò)程在計(jì)算機(jī)上自動(dòng)處理完成。 現(xiàn)代EDA技術(shù)是采用高級(jí)語(yǔ)言

2008-06-26 10:13:58

EDA技術(shù)是什么?EDA常用軟件有哪些?電子電路設(shè)計(jì)與仿真工具包括哪些呢?

2022-01-24 06:34:54

EDA雙鞭天線(xiàn)及匹配網(wǎng)絡(luò)設(shè)計(jì)方案EDA雙鞭天線(xiàn)及匹配網(wǎng)絡(luò)設(shè)計(jì)方案.docx

2012-08-11 09:55:16

在數(shù)字電路中TTL與非門(mén)的多余的輸入端應(yīng)如何處理?有幾種方法?

2023-04-28 10:49:44

數(shù)字電子鐘設(shè)計(jì)方案數(shù)字鐘是一種用數(shù)字電路技術(shù)實(shí)現(xiàn)時(shí)、分、秒計(jì)時(shí)的裝置,與機(jī)械式時(shí)鐘相比具有更高的準(zhǔn)確性和直觀(guān)性,且無(wú)機(jī)械裝置,具有更更長(zhǎng)的使用壽命,因此得到了廣泛的使用。數(shù)字鐘從原理上講是一種典型

2009-12-17 11:31:30

數(shù)字電路-數(shù)字時(shí)鐘電路設(shè)計(jì) 希望大家喜歡。

2016-12-06 09:46:39

數(shù)字電路設(shè)計(jì)與Verilog HDL

2015-07-16 16:21:19

在數(shù)字電子技術(shù)基礎(chǔ)課程中,數(shù)字電路設(shè)計(jì)的數(shù)學(xué)基礎(chǔ)是布爾函數(shù),并利用卡諾圖進(jìn)行化簡(jiǎn)。卡諾圖只適用于輸入比較少的邏輯函數(shù)的化簡(jiǎn)。數(shù)字電路的設(shè)計(jì)方法是:組合電路設(shè)計(jì):提出問(wèn)題→確定邏輯關(guān)系→列真值表→邏輯

2019-02-27 11:55:00

FPGA CPLFPGA CPLD 數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享FPGA/CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享摘要:在數(shù)字電路的設(shè)計(jì)中,時(shí)序設(shè)計(jì)是一個(gè)系統(tǒng)性能的主要標(biāo)志,在高層次設(shè)計(jì)方法中,對(duì)時(shí)序控制的抽象度也相應(yīng)

2012-08-11 10:17:18

在數(shù)字電路的設(shè)計(jì)中,時(shí)序設(shè)計(jì)是一個(gè)系統(tǒng)性能的主要標(biāo)志,在高層次設(shè)計(jì)方法中,對(duì)時(shí)序控制的抽象度也相應(yīng)提高,因此在設(shè)計(jì)中較難把握,但在理解 RTL 電路時(shí)序模型的基礎(chǔ)上,采用合理的設(shè)計(jì)方法在設(shè)計(jì)復(fù)雜數(shù)字

2012-02-02 15:40:10

本帖最后由 xianer317 于 2014-6-21 19:34 編輯

FPGA/CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享

2014-06-21 19:33:20

在數(shù)字電路的設(shè)計(jì)中,時(shí)序設(shè)計(jì)是一個(gè)系統(tǒng)性能的主要標(biāo)志,在高層次設(shè)計(jì)方法中,對(duì)時(shí)序控制的抽象度也相應(yīng)提高,因此在設(shè)計(jì)中較難把握,但在理解RTL電路時(shí)序模型的基礎(chǔ)上,采用合理的設(shè)計(jì)方法在設(shè)計(jì)復(fù)雜數(shù)字系統(tǒng)

2012-03-05 16:33:30

FPGACPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享

2012-08-07 21:46:49

labview在數(shù)字電路課程中的應(yīng)用

2012-05-06 11:22:54

關(guān)于數(shù)字電路設(shè)計(jì)的一些經(jīng)驗(yàn)

2015-03-17 21:27:38

什么是電磁干擾?電容有哪些類(lèi)型?三極管在數(shù)字電路中具有哪些應(yīng)用?

2021-09-28 07:49:16

三極管在數(shù)字電路里有什么應(yīng)用

2021-03-12 06:17:13

的輸出與輸入之間的邏輯關(guān)系,因而在數(shù)字電路中不能采用模擬電路的分析方法,例如,小信號(hào)模型分析法。由于數(shù)字電路中的器件主要工作在開(kāi)關(guān)狀態(tài),因而采用的分析工具主要是邏輯代數(shù),用功能表、真值表、邏輯表達(dá)式

2009-04-06 23:45:00

分享一款不錯(cuò)的基于可編程邏輯器件PLD的數(shù)字電路設(shè)計(jì)方案

2021-04-30 06:34:54

本帖最后由 gk320830 于 2015-3-5 00:03 編輯

華為《高速數(shù)字電路設(shè)計(jì)教材》

2012-08-20 13:23:04

華為《高速數(shù)字電路設(shè)計(jì)教材》這本書(shū)是專(zhuān)門(mén)為電路設(shè)計(jì)工程師寫(xiě)的。主要描述模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用

2014-09-01 23:09:11

華為《高速數(shù)字電路設(shè)計(jì)教材》這本書(shū)是專(zhuān)門(mén)為電路設(shè)計(jì)工程師寫(xiě)的。主要描述模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用

2014-09-01 23:20:19

),在數(shù)字系統(tǒng)設(shè)計(jì)和控制電路中越來(lái)越受到重視。介紹了這種電路的基本結(jié)構(gòu)、性能特點(diǎn)、應(yīng)用領(lǐng)域及使用中的注意事項(xiàng)。對(duì)基于EDA技術(shù)的FPGA進(jìn)行了展望。指出EDA技術(shù)將是未來(lái)電子產(chǎn)品設(shè)計(jì)技術(shù)發(fā)展的主要方向。

2019-09-03 06:17:15

本帖最后由 eehome 于 2013-1-5 10:02 編輯

就算作一個(gè)數(shù)字電路設(shè)計(jì),附有 protuse仿真圖還有 相關(guān)用到的資料

2012-06-08 14:12:12

多種EDA工具的FPGA設(shè)計(jì)方案

2012-08-17 10:36:17

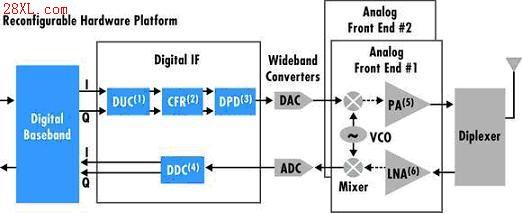

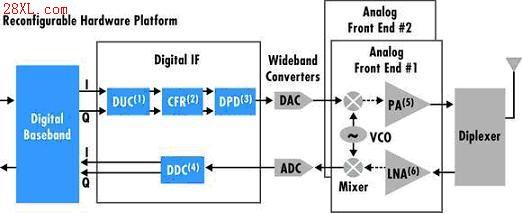

FPGA芯片是由哪些部分組成的?如何去實(shí)現(xiàn)一種基于FPGA芯片的可重構(gòu)數(shù)字電路設(shè)計(jì)?

2021-11-05 08:38:57

射頻和數(shù)字電路設(shè)計(jì)的區(qū)別是什么?

2021-05-18 06:05:19

怎么實(shí)現(xiàn)基于可編程邏輯器件的數(shù)字電路設(shè)計(jì)?

2021-05-06 08:36:18

大家好,我是電子愛(ài)好者新手,現(xiàn)在想學(xué)點(diǎn)數(shù)字電路設(shè)計(jì)。剛把數(shù)字電路這么課程學(xué)完。我想學(xué)電路設(shè)計(jì),不知道如何下手。比如FPGA什么的,這些都怎么開(kāi)始學(xué)習(xí)啊。請(qǐng)知情者指點(diǎn)下。謝謝

2013-08-02 08:17:31

[獵頭職位]國(guó)家重要芯片研發(fā)中心職位:數(shù)字電路設(shè)計(jì)工程師【崗位職責(zé)】負(fù)責(zé)USB、MIPI等高速接口IP或AD/DA的數(shù)字電路設(shè)計(jì)【任職資格】1.電子工程、微電子等相關(guān)專(zhuān)業(yè)碩士以上學(xué)歷,兩年以上

2015-02-27 10:52:58

時(shí)鐘簡(jiǎn)介時(shí)序在數(shù)字電路中的作用,就像通信中用到的載波,載波并不起眼,但是很重要。時(shí)鐘也一樣,現(xiàn)象上只是某種頻率波峰波谷跳動(dòng),一成不變。但是有了它,就像人類(lèi)的歷史有了時(shí)間軸一樣,什么時(shí)候該干什么事才有

2021-08-02 06:38:21

時(shí)鐘簡(jiǎn)介時(shí)序在數(shù)字電路中的作用,就像通信中用到的載波,載波并不起眼,但是很重要。時(shí)鐘也一樣,現(xiàn)象上只是某種頻率波峰波谷跳動(dòng),一成不變。但是有了它,就像人類(lèi)的歷史有了時(shí)間軸一樣,什么時(shí)候該干什么事才有

2021-08-12 07:16:05

時(shí)鐘簡(jiǎn)介時(shí)序在數(shù)字電路中的作用,就像通信中用到的載波,載波并不起眼,但是很重要。時(shí)鐘也一樣,現(xiàn)象上只是某種頻率波峰波谷跳動(dòng),一成不變。但是有了它,就像人類(lèi)的歷史有了時(shí)間軸一樣,什么時(shí)候該干什么事才有了可能。程序中發(fā)生的事件,能夠按照自己的意愿發(fā)生。...

2021-08-12 07:17:58

晶振具有的等效電氣特性晶振電路設(shè)計(jì)方案,電路中各元器件的作用是什么?消除晶振不穩(wěn)定和起振問(wèn)題有什么具體的建議和措施嗎?

2021-04-13 06:19:09

為什么淘寶上這本書(shū)的銷(xiāo)量那么低?有其他數(shù)字電路設(shè)計(jì)的實(shí)用書(shū)也可以推薦~謝謝!

2017-10-19 17:18:52

常見(jiàn)的電源符號(hào)有哪幾種?電源符號(hào)在數(shù)字電路中有何作用?

2021-11-04 07:44:03

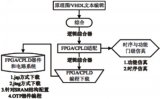

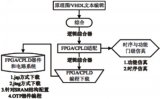

、設(shè)計(jì)方案、電路安裝等,激發(fā)學(xué)生的創(chuàng)新思維。設(shè)計(jì)性實(shí)驗(yàn)的實(shí)施過(guò)程,如圖1所示。 為了提高學(xué)生的電子設(shè)計(jì)能力和創(chuàng)新能力,中心根據(jù)高職教育教學(xué)特點(diǎn)與規(guī)律,構(gòu)建了基礎(chǔ)型、提高型、創(chuàng)新型三個(gè)遞進(jìn)層次的數(shù)字電路設(shè)計(jì)

2012-10-28 14:58:16

、綜合素質(zhì)、創(chuàng)新能力[’]。2005年我校電子技術(shù)實(shí)驗(yàn)教學(xué)中心(以下簡(jiǎn)稱(chēng)中心)以“加強(qiáng)基礎(chǔ)訓(xùn)練,培養(yǎng)能力,注重創(chuàng)新”為指導(dǎo)思想,在面向各類(lèi)專(zhuān)業(yè)的數(shù)字電路實(shí)驗(yàn)教學(xué)中,開(kāi)設(shè)了以學(xué)生為主、教師為輔的數(shù)字電路設(shè)計(jì)

2012-10-25 11:59:02

【簡(jiǎn)介】本書(shū)從高速數(shù)字電路的定義談起,介紹了傳輸線(xiàn)的基本理論,并涉及到了如何運(yùn)用Grounding/Guard降低噪聲等內(nèi)容,還以高速數(shù)字電路電氣特性,如串?dāng)_、反射及時(shí)鐘脈沖不對(duì)稱(chēng)等為例,闡述了一些

2017-12-12 08:51:55

《高速數(shù)字電路設(shè)計(jì)及EMC設(shè)計(jì)》分享。

2015-08-04 11:50:33

高速數(shù)字電路設(shè)計(jì)的幾個(gè)基本概念高速數(shù)字電路設(shè)計(jì)的基本要求是什么

2021-04-27 06:19:05

EDA軟件在電路設(shè)計(jì)中的應(yīng)用

摘要: 在EDA軟件的基礎(chǔ)上, 介紹了仿真功能在數(shù)字邏輯電路設(shè)計(jì)中的應(yīng)用, 佐證了由傳統(tǒng)實(shí)驗(yàn)教學(xué)向現(xiàn)代化創(chuàng)新性教學(xué)的重要性。并進(jìn)

2009-12-05 16:22:13 0

0 基于LabVIEW的數(shù)字電路設(shè)計(jì)和仿真

數(shù)字電路設(shè)計(jì)和仿真是電子工程領(lǐng)域的基本技術(shù)。介紹了基于LabV IEW的數(shù)字電路設(shè)計(jì)和仿真的原理和方法,比較了其與專(zhuān)業(yè)EDA軟

2010-03-30 16:09:49 123

123 數(shù)字電路實(shí)驗(yàn)的虛擬化設(shè)計(jì)方案

介紹了虛擬儀器的簡(jiǎn)單使用方法及其在數(shù)字電路實(shí)驗(yàn)教學(xué)中的應(yīng)用, 列舉了幾個(gè)例子, 并通過(guò)虛擬儀器與傳統(tǒng)儀器的比較得出

2010-03-30 16:15:28 20

20 摘要:在數(shù)字電路課程設(shè)計(jì)中引入先進(jìn)的EDA技術(shù)是數(shù)字電路實(shí)驗(yàn)教學(xué)改革的方向,本文通過(guò)一個(gè)數(shù)字電路課程設(shè)計(jì)的實(shí)例,說(shuō)明了基于EDA技術(shù)中的VHDL語(yǔ)言和CPLD/FPGA器件進(jìn)行數(shù)字系

2010-04-26 10:08:50 23

23 本書(shū)是專(zhuān)門(mén)為電路設(shè)計(jì)師工程師寫(xiě)的

它主要描述模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用

1-3章分別介紹了模擬電路術(shù)語(yǔ)、邏輯門(mén)高速特性和標(biāo)準(zhǔn)高速電路測(cè)量

2010-06-23 18:02:57 63

63 流水線(xiàn)技術(shù)在高速數(shù)字電路設(shè)計(jì)中的應(yīng)用

2010-07-17 16:37:21 6

6 在進(jìn)行數(shù)字電路設(shè)計(jì)和應(yīng)用開(kāi)發(fā)的過(guò)程中,經(jīng)常遇到在實(shí)驗(yàn)室調(diào)試很好的電路板一到工作現(xiàn)場(chǎng)就會(huì)出現(xiàn)這樣或那樣的問(wèn)題,這主要是由于設(shè)計(jì)未充分考慮到外界環(huán)境存在的干擾,如

2010-08-06 15:42:32 49

49 這本書(shū)是專(zhuān)門(mén)為電路設(shè)計(jì)工程師寫(xiě)的。它主要描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用。通過(guò)列舉很多的實(shí)例,作者詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴

2010-11-08 16:49:54 0

0 高速數(shù)字電路設(shè)計(jì)

關(guān)于高速數(shù)字電路的電氣特性,設(shè)計(jì)重點(diǎn)大略可分為三項(xiàng) : Ø 正時(shí) (Timing) :由于數(shù)字電路大多依據(jù)時(shí)脈信號(hào)來(lái)做信號(hào)間的同

2007-10-16 17:22:57 2746

2746 數(shù)字電路設(shè)計(jì)

關(guān)于高速數(shù)字電路的電氣特性,設(shè)計(jì)重點(diǎn)大略可分為三項(xiàng):

正時(shí)(Timing) :由于數(shù)字電路大

2009-08-26 19:08:06 2665

2665 數(shù)字信號(hào)處理技術(shù)和大規(guī)模集成電路技術(shù)的迅猛發(fā)展,為我們?cè)O(shè)計(jì)數(shù)字電路提供了新思路和新方法。當(dāng)前數(shù)字系統(tǒng)設(shè)計(jì)正朝著

2010-11-12 18:06:30 745

745 為使數(shù)字鐘從電路設(shè)計(jì)、性能分析到設(shè)計(jì)出PCB版(即印制電路版)圖的整個(gè)過(guò)程能夠在計(jì)算機(jī)上自動(dòng)處理完成,從而縮短設(shè)計(jì)周期、提高設(shè)計(jì)效率、減小設(shè)計(jì)風(fēng)險(xiǎn)。本系統(tǒng)基于EDA技術(shù)的設(shè)

2011-03-18 16:56:36 0

0 《VHDL與數(shù)字電路設(shè)計(jì)》是有盧毅、賴(lài)杰主編的,主要介紹涉及數(shù)字系統(tǒng)設(shè)計(jì)的多方面原理、技術(shù)及應(yīng)用,主要內(nèi)容有數(shù)字系統(tǒng)的基本設(shè)計(jì)思想、設(shè)計(jì)方法和設(shè)計(jì)步驟, VHDL 硬件描述語(yǔ)言

2011-07-11 15:54:27 0

0 本文介紹了 PSpice軟件 在輔助分析和設(shè)計(jì)數(shù)字電路中的應(yīng)用,并通過(guò)PSPICE軟件有效方針典型數(shù)字電路與系統(tǒng)的實(shí)例,證明該軟件在數(shù)字電子技術(shù)課程的計(jì)算機(jī)輔助教學(xué)及綜合電子系統(tǒng)的

2011-08-23 16:11:31 177

177 闡述了電路虛擬技術(shù)在《數(shù)字電路》課程實(shí)驗(yàn)中的輔助作用,分析了在數(shù)字電路課程實(shí)驗(yàn)中虛擬技術(shù)應(yīng)用的利與弊,給出了應(yīng)用虛擬電路技術(shù)在數(shù)字電路課程實(shí)驗(yàn)教學(xué)的建議。

2012-02-22 11:23:34 10

10 主要介紹電子設(shè)計(jì)自動(dòng)化EDA技術(shù)的仿真軟件Multisim的主要功能特點(diǎn),并通過(guò)該軟件對(duì)基于555定時(shí)器設(shè)計(jì)的多諧振蕩器的波形仿真這一實(shí)例來(lái)進(jìn)一步說(shuō)明它在數(shù)字電路設(shè)計(jì)中的應(yīng)用。在與傳

2013-02-22 15:27:53 97

97 高速數(shù)字電路設(shè)計(jì)及EMC設(shè)計(jì)!資料來(lái)源網(wǎng)絡(luò),如有侵權(quán),敬請(qǐng)見(jiàn)諒

2015-11-19 14:48:57 0

0 高速數(shù)字電路設(shè)計(jì)及EMC設(shè)計(jì)(華為),下來(lái)看看。

2016-03-29 15:41:20 52

52 高速數(shù)字電路設(shè)計(jì)大全

2017-01-17 19:54:24 55

55 數(shù)字電路設(shè)計(jì)方案中DSP與FPGA的比較與選擇

2017-01-18 20:39:13 15

15 基于EDA與ISP技術(shù)的數(shù)字電路的設(shè)計(jì)

2017-02-07 14:58:18 20

20 通過(guò)仿真確定設(shè)計(jì)基本成功后,即可通過(guò)Byteblaster下載電纜線(xiàn)將設(shè)計(jì)項(xiàng)目以JTAG方式下載到器件中,完成設(shè)計(jì)所有工作。通過(guò)此例設(shè)計(jì)流程講述可知,EDA技術(shù)及其工具在數(shù)字電路系統(tǒng)(包括模擬電路系統(tǒng))中正發(fā)揮著越來(lái)越重要作用,其應(yīng)用深度和廣度正在向更深層次延伸。

2018-07-18 13:59:00 1007

1007 EDA設(shè)計(jì)方法又稱(chēng)為基于芯片設(shè)計(jì)方法,集成化程度更高,可實(shí)現(xiàn)片上系統(tǒng)集成,進(jìn)行更加復(fù)雜電路芯片化設(shè)計(jì)和專(zhuān)用集成電路設(shè)計(jì),使產(chǎn)品體積小、功耗低、可靠性高;可在系統(tǒng)編程或現(xiàn)場(chǎng)編程,使器件編程、重構(gòu)、修改簡(jiǎn)單便利,可實(shí)現(xiàn)在線(xiàn)升級(jí);可進(jìn)行各種仿真,開(kāi)發(fā)周期短,設(shè)計(jì)成本低,設(shè)計(jì)靈活性高。

2018-07-27 18:33:00 4986

4986 三極管在數(shù)字電路里的開(kāi)關(guān)特性,最常見(jiàn)的應(yīng)用有 2 個(gè):一個(gè)是控制應(yīng)用,一個(gè)是驅(qū)動(dòng)應(yīng)用。

2017-12-22 17:16:22 11257

11257

這本書(shū)是專(zhuān)門(mén)為電路設(shè)計(jì)工程師寫(xiě)的。它主要描述了模擬電路原理在高速數(shù)字電路設(shè)計(jì)中的分析應(yīng)用。通過(guò)列舉很多的實(shí)例,作者詳細(xì)分析了一直困擾高速電路路設(shè)計(jì)工程師的鈴流、串?dāng)_和輻射噪音等問(wèn)題。

2018-09-10 08:00:00 61

61 EDA技術(shù)涉及面很廣,內(nèi)容豐富,從教學(xué)和實(shí)用角度看,主要應(yīng)掌握如下4個(gè)方面內(nèi)容:一是大規(guī)模可編程邏輯器件;二是硬件描述語(yǔ)言;三是軟件開(kāi)發(fā)工具;四是實(shí)驗(yàn)開(kāi)發(fā)系統(tǒng)。其中,大規(guī)模可編程邏輯器件是利用EDA

2019-02-14 15:45:45 1530

1530

EDA(電子線(xiàn)路設(shè)計(jì)座自動(dòng)化)是以計(jì)算機(jī)為工作平臺(tái)、以硬件描述語(yǔ)言(VHDL)為設(shè)計(jì)語(yǔ)言、以可編程器件(CPLD/FPGA)為實(shí)驗(yàn)載體、以ASIC/SOC芯片為目標(biāo)器件、進(jìn)行必要元件建模和系統(tǒng)仿真電子產(chǎn)品自動(dòng)化設(shè)計(jì)過(guò)程。

2019-02-15 15:11:58 1392

1392 高速數(shù)字電路設(shè)計(jì)跟低速數(shù)字電路設(shè)計(jì)不同的是:他強(qiáng)調(diào)組成電路的無(wú)源部件對(duì)電路的影響。這些無(wú)源器件包括導(dǎo)線(xiàn)、電路板和組成數(shù)字產(chǎn)品的集成電路。在低速設(shè)計(jì)中,這些部件單純

的只是電路的一部分,根本不用多做考慮,可是在高速設(shè)計(jì)中,這些部件對(duì)電路的性能有著直接的影響。

2019-04-11 11:38:32 3581

3581

485接口EMC電路設(shè)計(jì)方案!

2020-02-05 12:53:27 4078

4078 電子設(shè)計(jì)自動(dòng)化(Electronic Design Automation,EDA)技術(shù)是新興的電子設(shè)計(jì)自動(dòng)化工具,是目前世界電子設(shè)計(jì)的最新技術(shù)方向和潮流 [1]。在數(shù)字電路實(shí)驗(yàn)中,EDA 作為一種重要的實(shí)驗(yàn)工具使傳統(tǒng)數(shù)字電路實(shí)驗(yàn)的教學(xué)模式得到了改變,實(shí)驗(yàn)的操作過(guò)程得到了一定的簡(jiǎn)化。

2020-08-16 11:58:32 2218

2218

在當(dāng)今電子技術(shù)行業(yè)發(fā)展過(guò)程中,對(duì)高速電路數(shù)字設(shè)計(jì)十分關(guān)注,高速數(shù)字電路是利用多個(gè)電子元件組成的,可以讓計(jì)算機(jī)高速數(shù)字電路技術(shù)進(jìn)一步提高,因此在計(jì)算機(jī)中使用高速數(shù)字電路設(shè)計(jì)技術(shù)也就更加普遍。

2020-08-21 17:41:10 2924

2924 高速數(shù)字電路設(shè)計(jì)-華為

2021-04-21 15:45:08 0

0 華為高速數(shù)字電路設(shè)計(jì)教材資源下載

2021-06-04 11:06:00 86

86 1. 前言 在數(shù)字電路課程中,老師在講組合邏輯的時(shí)候,一般都會(huì)講競(jìng)爭(zhēng)與冒險(xiǎn)。sky當(dāng)時(shí)也聽(tīng)的云里霧里,沒(méi)有想清楚如下問(wèn)題: 1) 競(jìng)爭(zhēng)與冒險(xiǎn)究竟是什么東西?有啥物理現(xiàn)象? 2) 在數(shù)字電路設(shè)計(jì)

2021-08-09 14:43:08 2657

2657

小信號(hào)放大電路設(shè)計(jì)方案匯總

2021-09-14 15:01:12 127

127 FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.(電源技術(shù)發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51 實(shí)用電子電路設(shè)計(jì)與調(diào)試數(shù)字電路教材資料免費(fèi)下載。

2022-04-07 14:46:38 26

26 黑魔書(shū) 351頁(yè)- 高速數(shù)字設(shè)計(jì)PDF版,華為內(nèi)部數(shù)字電路設(shè)計(jì)教材

2022-06-08 14:33:25 0

0 高速數(shù)字電路設(shè)計(jì)教材-華為

2022-06-13 14:55:54 0

0 數(shù)字電路設(shè)計(jì)是數(shù)字電路最為關(guān)鍵及重要的一步,今天我們將從各個(gè)流程為大家介紹完整的數(shù)字電路設(shè)計(jì)!

2022-07-10 17:14:16 6046

6046 在數(shù)字電路設(shè)計(jì)中,IP 是通過(guò)EDA工具創(chuàng)建的,通常包括 IP 核的設(shè)計(jì)、測(cè)試、驗(yàn)證、封裝、文檔管理等過(guò)程。EDA技術(shù)可以提供一系列工具和軟件,幫助設(shè)計(jì)人員在IP的設(shè)計(jì)上實(shí)現(xiàn)快速開(kāi)發(fā)、高效驗(yàn)證和重用。

2023-04-10 17:30:47 4105

4105 數(shù)字電路用什么儀器測(cè)試? 數(shù)字電路測(cè)試是數(shù)字電路設(shè)計(jì)的重要環(huán)節(jié)。它是驗(yàn)證數(shù)字電路功能是否按照所期望的方式工作的過(guò)程。在數(shù)字電路測(cè)試過(guò)程中,要使用一些專(zhuān)門(mén)的儀器來(lái)驗(yàn)證電路是否按照設(shè)計(jì)預(yù)期的方式工作

2023-09-19 16:33:13 570

570 高速數(shù)字電路設(shè)計(jì)

2022-12-30 09:22:18 19

19 高速數(shù)字電路設(shè)計(jì)教材-華為

2022-12-30 09:22:18 41

41 電子發(fā)燒友網(wǎng)站提供《OrCAD PSpiceA_D在數(shù)字電路仿真中的應(yīng)用.pdf》資料免費(fèi)下載

2023-11-17 15:38:09 0

0 電子發(fā)燒友網(wǎng)站提供《OrCAD PSpice A_D在數(shù)字電路仿真中的應(yīng)用.pdf》資料免費(fèi)下載

2023-11-18 09:22:55 1

1 電子發(fā)燒友網(wǎng)站提供《FPGA/CPLD數(shù)字電路設(shè)計(jì)經(jīng)驗(yàn)分享.pdf》資料免費(fèi)下載

2023-11-21 11:03:12 3

3 芯片設(shè)計(jì)企業(yè)關(guān)注的焦點(diǎn)。作為芯片產(chǎn)業(yè)的根技術(shù)和硬科技,EDA和IP在大規(guī)模數(shù)字電路設(shè)計(jì)中發(fā)揮著不可替代的作用,也是集成電路技術(shù)發(fā)展的重要助推器。其運(yùn)用的好壞,決定著

2023-12-28 08:23:15 655

655

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論