引言

對于應用0.18mm及以下工藝的設計而言,二維提取進行Sign-off靜態時序分析就顯得有些粗略,而且精度不夠。這是因為對于0.18mm及以下工藝,毗鄰金屬連線所產生的耦合電容在設計中已經成為不得不考慮的寄生參數,于是先進的寄生參數提取工具就可以檢測到相同層次之間產生耦合電容的影響。因此對0.18mm及以下工藝的設計,通過物理驗證,在進行流片之前,需要用專門的寄生參數抽取工具將每一個節點的RC網絡信息寫成文件傳遞給設計,即所謂的反標,再用靜態時序分析工具做精確的版圖時序分析。

Star-RCXT工具介紹

Star- RCXT以其高精度、友好的用戶界面以及和其它工具良好的結合成為目前業界比較流行的一款寄生參數提取工具,是專門針對0.18mm及以下工藝的寄生參數提取所設計的。它采用了二點五維的幾何提取技術,達到了三維的提取精度,但比三維的抽取工具速度快很多,能夠快速準確地對上百萬門的設計進行全局的寄生參數提取。

用Star-RCXT進行寄生參數提取的條件

應用Star-RCXT進行精細寄生參數提取,還需要兩個與工藝參數有關的文件:mapping文件和ITF(Interconnect Technology Format)文件。ITF文件是由晶圓代工廠直接提供的,它包含的信息主要有:工藝采用的各個層次(包括電介質、過孔和金屬導線等),各個層次在工藝流程中的厚度、寬度等物理尺寸,各個層次的電氣參數(如介電常數、方塊阻值等)。Star-RCXT不能直接使用ITF格式的文件,它提供grdgenxo 命令將晶圓代工廠提供的ITF格式文件轉換成Star-RCXT所需要的.nxtgrd格式文件,Mapping文件用于實現這種轉換過程,將目標.nxtgrd文件中各個層次名稱與設計數據庫中的層名稱相對應起來。

Star-RCXT支持的格式

寄生參數提取工具Star-RCXT支持多種格式輸入,主要有Milkyway、Lef/Def、Hercules和Calibre格式。也支持多種格式輸出,如輸出格式為IEEE 1481標準的SPEF(Standard Parastic Exchange Format)格式;輸出與PrimeTime靜態時序分析工具最有效對接的SBPF(Synopsys Binary Parasitic Format)格式;輸出格式包含了每一個節點RC網絡信息的DSPF (Detailed Standard Parasitic Format)格式;還有STAR、NETNAME、MW、CONLY等格式。因為寄生電容值與其毗鄰的金屬連線有密切關系,版圖上一個圖形有可能會影響到其相鄰模塊中某一條連線的寄生參數提取,因此寄生參數提取是針對flat版圖,提取出來的寄生參數信息是不帶有層次的。也正是由于這個原因,寄生參數提取一般需要花費較長的時間,并占用較大的硬件資源。

Primetime工具介紹

PrimeTime 是Synopsys公司提供的一個針對復雜全芯片進行靜態時序分析的工具。PrimeTime可以集成于邏輯綜合和物理綜合的流程,讓設計者分析并解決復雜的時序問題,提高時序收斂的速度。它是一種窮盡分析方法,不依賴于激勵,分析檢查電路或設計對象中的所有時序路徑,包括無效路徑,能夠保證100%的覆蓋率。它運行速度快,占用內存少,完全克服了動態時序驗證的缺陷,適用于超大規模芯片系統的電路驗證。

PrimeTime分析原理

PrimeTime 進行靜態時序分析時把整個芯片按照時鐘分成許多時序路徑。路徑的起點是時序單元的輸出引腳或是設計的輸入端口,路徑的終點是時序單元的輸入引腳或是設計的輸出端口。根據起點和終點的不同,可將邏輯電路分解為圖1中用虛線表示的四種路徑,分別代表了以下四種類型: 路徑1起始于輸入端口,終止于時序單元的數據輸入端;路徑2起始于時序單元的時鐘引腳,終止于時序單元的數據輸入端;路徑3起始于時序單元的時鐘引腳,終止于輸出端口;路徑4起始于輸入端口,終止于輸出端口。

圖1 邏輯電路中的四種時序路徑

PrimeTime 工具把設計打散成一系列時序路徑之后,沿每條路徑計算延時。路徑的總延時是該路徑中所有單元延時和連線延時的和。單元延時為路徑中從邏輯門的輸入到輸出的延時量,若沒有提供反標延時信息,PrimeTime會根據工藝庫中提供的此單元延遲表來計算單元延時。典型的單元延遲表是輸入傳輸時間和輸出負載電容的函數,基于二維表格來計算每個單元的延時。對于在表格中找不到對應點的情況,可通過內插或外推表格中的值來獲得當前條件下的延時值。連線延時是時序路徑中從一個單元的輸出到下一個單元輸入的延時總和。PrimeTime可讀取由專門提取工具得到的詳細內部互聯網絡的寄生電容和電阻值,并基于此精確地計算連線延時,以完成精確的版圖時序分析。

PrimeTime分析要求

靜態時序分析的目的是保證設計中的以上四種類型路徑可以滿足建立時間和保持時間的要求。即無論其起點是什么,信號都可以被及時地傳遞到該路徑的終點,并且在電路正常工作所必需的時間段內保持恒定。如果建立時間和保持時間不能得到滿足,觸發器就無法采樣到正確的數據。

對FFT處理器進行寄生參數提取和靜態時序分析

當 FFT處理器完成版圖設計,通過Calibre DRC和LVS進行Sign-off的靜態時序分析時,可用專門的寄生參數提取工具Star-RCXT將每一個節點的RC網絡信息寫成文件傳遞給設計,再用靜態時序分析工具PrimeTime讀取由Star-RCXT工具得到的詳細內部互聯網絡的寄生電容和電阻值,并基于此精確地計算連線延遲,做精確的版圖時序分析。

對FFT處理器進行寄生參數提取

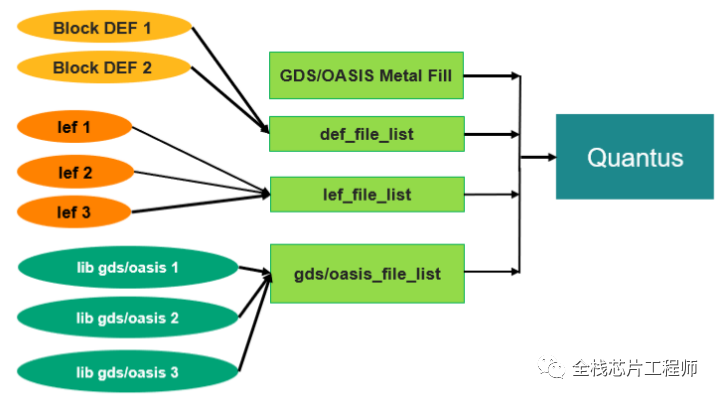

由于FFT項目采用Mentor公司的 Calibre工具進行DRC和LVS,因此寄生參數提取工具Star-RCXT采用的輸入格式為Calibre,基于CCI(Calibre Connectiity Interface)的Star-RCXT寄生參數提取流程如圖2所示。

圖2 基于CCI的寄生參數提取流程

在 Calibre中采用flat方式對FFT處理器進行LVS,通過LVS后自動產生SVDB目錄,并將配置LVS運行時設置的內容保存為lvsset文件。然后編寫query.cmd文件,該文件指定基于CCI的Star-RCXT寄生參數提取所需文件的位置,如標注的GDSII版圖、層映射信息、頂層端口信息、理想版圖網表、網絡名信息、交互表等。編寫好query.cmd文件后,在calibredrv工具的命令行中執行命令:Calibre- query svdb

本設計用運行Star-RCXT命令文件(star.cmd)來進行寄生參數提取,在編寫star.cmd命令文件時要輸入:模塊名稱xtalkdetailDRCLVS、層映射文件SmicVTMP_LO_SRAM _MR_MM_HV_LC_018.map、電源/地網絡名稱VDD和GND、加工工藝文件smic018.nxtgrd、提取參數的輸出格式SPEF、提取網絡的范圍、是否要將耦合電容折算成對地電容、配置LVS運行的設置文件lvsset和指定進行基于CCI寄生參數提取所需文件位置的文件 query.cmd等。然后在Star-RCXT中運行StartXtract -clean star.cmd命令即可完成寄生參數提取,輸出文件名為xtalkdetailDRCLVS.spef。

對FFT處理器進行靜態時序分析

首先在PrimeTime的啟動文件(.synopsys_pt.setup)中設置與庫文件相關的信息,如用set_link_library { * smic18_ss.db smic18IO_line_ss.db}命令來設置鏈接庫,用set target_library {* smic18_ss.db smic18_IO_line_ss.db}命令來設置目標庫、用set_min_library命令來指定工藝庫用于最大延遲和最小延遲分析等。然后用 primetime命令啟動PrimeTime的圖形用戶界面,對FFT處理器進行Sign-off的靜態時序分析。具體流程包括:讀入設計數據、約束時序、設定環境和分析條件、檢查設計數據和分析設置參數,以及執行分析和檢查結果5步。

讀入設計數據

讀入網表文件用read_verilog命令,讀入由Star-RCXT提取輸出的SPEF格式寄生網表用read_parasitics命令。若要分析建立時間則要讀入最壞情況的寄生電容和電阻信息,若要分析保持時間則要讀入最好情況的寄生電容和電阻信息。

約束時序

進行Sign-off靜態時序分析時,由于現在的網表中已經包括了實際的時鐘信息,用create_clock命令來定義一個時鐘的基本信息,如周期、波形等,將該時鐘信號在實際的時鐘樹中傳播,進而得到實際的時鐘延時和偏移。用set_propagated_ clock命令可以根據時鐘樹,自動計算出時鐘信號到達終點的延時和偏移。Sign-off靜態時序分析可不設置時鐘的確定性,但有時為了提高設計可靠性,用set_clock_uncertainty命令對建立時間和保持時間都設置一個很小時間值。根據設計規范要求用set_input_delay命令直接設置輸入延時值,用set_output_delay命令直接設置輸出延時值等。

設定環境和分析條件

PrimeTime 中set_operating_conditions命令用來根據工藝庫指定工藝、溫度和電壓的工作條件。分析建立時間時工作條件應當在最壞情況進行,即 set_operating_conditions worst;分析保持時間時工作條件應當在最好情況進行,即set_operating_conditions best。用set_load命令設置輸出端口的負載,用set_driving_cell命令指定輸入端口的驅動單元等。另外可用 set_case_analysis命令在某個端口設置為固定邏輯常數或邏輯轉換限制該信號在設計中傳播,如果在時序分析時不考慮掃描鏈的影響,可執行 set_case_analysis 0 [get_ports scan_en_pad]命令。

檢查設計數據和分析設置參數

在進行時序分析前要先檢查設計數據,如層次、庫、端口、單元等,以及分析設置參數,如時鐘、輸入延遲約束、輸出延遲約束等是否已經設置或設置是否正確。如, 用check_timing命令來檢查是否存在未定義的時鐘、未定義的輸入到達時間和未定義的輸出約束等;用report_design命令輸出當前設計的一系列屬性,如分析類型、所選的工作條件、線負載模型和設計規則等;用report_port命令顯示端口名、引腳電容、線電容和輸入輸出延遲等端口信息。

執行分析和檢查結果

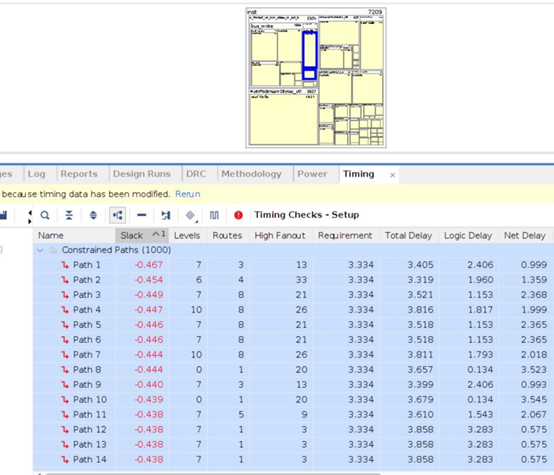

在設計數據和參數設置均正確的情況下進行時序分析,然后查看分析結果,獲得設計具體的時間信息。如用report_timing命令產生一條最大時延路徑的詳細報告,包括路徑信息(工作條件、線負載模型的模式、路徑起點、路徑終止點和路徑類型等)、路徑延時、路徑延時要求和總結部分。用report_constraint-all_violator命令報告所有的建立時間時序違規。為了準確了解FFT處理器所有路徑的建立時間情況,可執行菜單命令Timing→Histogram→Endpoint Slack…彈出Endpoint Slack對話框,在Delay type中選擇max后按OK可得如圖3所示的所有路徑建立時間情況,從中可知建立時間最小值為0.13792,滿足建立時間要求。再運行命令 report_analysis_coverage得PrimeTime分析的路徑條數為45957,分析的覆蓋率為100%,建立時間的違規率為0%。

圖3 建立時間的分析結果

為了準確了解FFT處理器所有路徑的保持時間情況,可進行與分析建立時間過程相同的步驟。

結語

靜態時序分析已經成為數字集成電路設計必不可少的環節。本文應用寄生提取工具Star-RCXT基于CCI流程對FFT處理器進行寄生參數提取,再用靜態時序分析工具PrimeTime讀取由Star-RCXT抽取工具得到的內部互連網絡的詳細寄生電容和電阻值,進行精確的版圖時序分析。它不需要輸入測試向量就能覆蓋所有的路徑,且運行速度很快,占用內存較少,可以對芯片設計進行全面的時序驗證。

電子發燒友App

電子發燒友App

評論