三星16/32位ARM處理器S3C4510B是目前在國內(nèi)應(yīng)用非常廣泛的一種性價比很高的ARM處理器,本文在介紹S3C4510B中HDLC通道結(jié)構(gòu)特點的基礎(chǔ)上,詳細(xì)說明了4510中HDLC通道在DMA收發(fā)方式下的工作過程

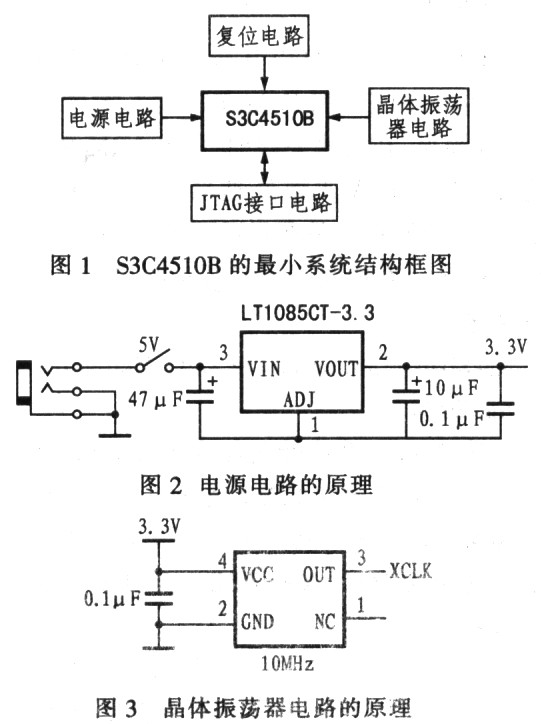

三星16/32位ARM處理器S3C4510B是目前在國內(nèi)應(yīng)用非常廣泛的一種性價比很高的ARM處理器,本文在介紹S3C4510B中HDLC通道結(jié)構(gòu)特點的基礎(chǔ)上,詳細(xì)說明了4510中HDLC通道在DMA收發(fā)方式下的工作過程,使用方法和編程中的一些注意事項。 1:S3C4510B簡介 S3C4510B(以下簡稱4510)是韓國三星公司開發(fā)的一款基于ARM7TDMI架構(gòu)的16/32位高性能微處理器。具用豐富的外圍接口,如以太網(wǎng),HDLC等,可靈活配置,適用于多種應(yīng)用。4510具有以下性能特點: ◆ 8K字節(jié)的內(nèi)部CACHE,也可用作內(nèi)部SRAM ◆ 兩線IIC接口,作為IIC主器件使用 ◆ 以太網(wǎng)控制器 ◆ 雙通道HDLC控制器 ◆ 雙UART ◆ 雙GDMA通道 ◆ 兩個32位定時器 ◆ 18個可編程IO端口 ◆ 中斷控制功能 ◆ 外部SDRAM/DRAM/FLASH/ROM控制 本文主要介紹4510中HDLC通道的使用和編程方法。 2:S3C4510B的HDLC通道簡介 HDLC協(xié)議幀結(jié)構(gòu)和特性請參閱相關(guān)書籍和4510數(shù)據(jù)手冊,這里不詳細(xì)介紹。 4510的HDLC通道結(jié)構(gòu)如附圖1所示。

具有以下特點: 1. FIFO:發(fā)送和接收模塊都有32字節(jié)(8字)FIFO,提供CPU內(nèi)部總線到HDLC串行接口之間的數(shù)據(jù)緩存功能。 2. DMA:HDLC通道的發(fā)送和接收支持DMA方式。 3. 波特率產(chǎn)生:4510的HDLC通道包含一個可編程的波特率產(chǎn)生計數(shù)器,能夠產(chǎn)生各種波特率的傳輸速率。 4. DPLL:4510的HDLC通道包含一個數(shù)字鎖相環(huán)(DPLL),提供了時鐘恢復(fù)功能,可從編碼后的數(shù)據(jù)流中迅速提取出時鐘信息。 5. 編碼方式:4510的HDLC通道支持五種編碼方式,分別為NRZ,NRZI,FM0,FM1和差分曼徹斯特編碼,編碼波形請參看附圖2。 詳細(xì)的內(nèi)容請參閱4510數(shù)據(jù)手冊。 3:S3C4510B的HDLC通道工作過程介紹 4510的HDLC通道收發(fā)可工作在CPU模式和DMA模式下,在我們的應(yīng)用和編程中使用了DMA方式,因此這里主要介紹DMA方式下的工作過程。 4510的HDLC通道工作過程大致可以分為通道初始化,數(shù)據(jù)發(fā)送,數(shù)據(jù)接收三個部分。 3.1: HDLC通道初始化過程 HDLC通道初始化過程可分為七個步驟;一:通道復(fù)位,恢復(fù)其默認(rèn)配置;二:通過設(shè)置工作模式寄存器(HMODE)來配置HDLC工作模式;三:通過設(shè)置控制寄存器(HCON)來控制HDLC通道的工作;四:通過設(shè)置中斷控制寄存器(HINT)來控制HDLC通道的中斷產(chǎn)生;五:設(shè)置站址寄存器(HSAR0-HSAR3)和站址屏蔽寄存器(HMASK),以完成接收操作的地址比較功能;六:建立DMA方式的發(fā)送和接收BUFFER描述符鏈表結(jié)構(gòu),并初始化DMA發(fā)送BUFFER描述符指針寄存器(HDMATxPTR)和DMA接收BUFFER描述符指針寄存器(HDMARxPTR);七:使能 HDLC通道的收發(fā)功能。

3.1.1:HDLC通道復(fù)位 HDLC通道復(fù)位可通過設(shè)置控制寄存器(HCON)前4比特來完成,請參閱4510數(shù)據(jù)手冊。

3.1.2:HDLC通道工作模式配置 工作模式寄存器(HMODE)中的不同位定義了不同的工作模式,這里介紹較常用的幾種模式設(shè)置,詳細(xì)內(nèi)容和配置方法請參閱4510數(shù)據(jù)手冊。 1. 數(shù)據(jù)編碼方式選擇:從所支持的五種編碼方式中選擇。 2. 波特率時鐘源選擇:如果使用4510的內(nèi)部波特率產(chǎn)生器,則需要為其選擇時鐘源,同時根據(jù)不同的時鐘源配置波特率產(chǎn)生計數(shù)器(HBRGTC)產(chǎn)生需要的時鐘信號。 3. DPLL時鐘源選擇:如果使用DPLL,則需要為其選擇要跟蹤的時鐘源。 4. 發(fā)送時鐘選擇:4510的HDLC通道支持多種發(fā)送時鐘源,可通過設(shè)置HDLC通道的模式寄存器中的相應(yīng)位來選擇。 5. 接收時鐘選擇:4510的HDLC通道支持多種接收時鐘源,可通過設(shè)置HDLC通道的模式寄存器中的相應(yīng)位來選擇。

3.1.3:HDLC通道控制寄存器配置 控制寄存器(HCON)控制HDLC通道工作情況,這里介紹常用的控制選項,詳細(xì)的內(nèi)容和配置方法請參閱4510數(shù)據(jù)手冊。 1. 波特率產(chǎn)生/DPLL使能:如果使用了內(nèi)部的波特率產(chǎn)生器或者DPLL,為使它們工作,需要設(shè)置HDLC通道的控制寄存器中相應(yīng)位來啟動工作。 2. 收發(fā)FIFO深度設(shè)置:當(dāng)使用CPU方式進(jìn)行HDLC收發(fā)時,可設(shè)置收發(fā)FIFO深度。FIFO深度可設(shè)置為8字節(jié)/32字節(jié)。當(dāng)使用DMA方式時,此設(shè)置無效。 3. DMA發(fā)送停止/跳過方式設(shè)置:使用DMA方式發(fā)送時,如果當(dāng)前使用的發(fā)送BUFFER描述符不屬于DMA所有,可根據(jù)此設(shè)置來停止DMA發(fā)送,或是跳到發(fā)送BUFFER描述符鏈表中的下一個描述符。 4. DMA接收停止/跳過方式設(shè)置:使用DMA方式接收時,如果當(dāng)前使用的接收BUFFER描述符不屬于DMA所有,可根據(jù)此設(shè)置來停止DMA接收,或是跳到接收BUFFER描述符鏈表中的下一個描述符。 5. 通道空閑標(biāo)志模式設(shè)置:確定通道空閑時發(fā)送哪種空閑標(biāo)志(全1或者0X7E)。 6. Flag發(fā)送模式設(shè)置:確定幀分隔方式(單FLAG或者雙FLAG方式)。 7. 收發(fā)CRC校驗設(shè)置:確定HDLC收發(fā)過程中是否進(jìn)行CRC校驗。 8. HDLC環(huán)回設(shè)置:用于HDLC環(huán)回測試,正常工作時HDLC環(huán)回應(yīng)打開。

3.1.4:HDLC通道中斷控制寄存器(HINT)配置 中斷控制寄存器(HINT)控制HDLC收發(fā)中斷的產(chǎn)生。共有24種中斷產(chǎn)生條件,這里介紹DMA方式收發(fā)時編程中用到的一些中斷產(chǎn)生條件。詳細(xì)內(nèi)容請參閱4510數(shù)據(jù)手冊。 對于HDLC通道發(fā)送中斷:

1. 發(fā)送FIFO下沖:此條件(TxUIE)當(dāng)發(fā)送FIFO產(chǎn)生下沖時發(fā)生。此時DMA發(fā)送被自動禁止,因此發(fā)送中斷處理程序中必須首先清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位,然后在下次發(fā)送前使能DMA發(fā)送。

2. DMA發(fā)送Abort:此條件(DTxABTIE)當(dāng)DMA發(fā)送放棄時產(chǎn)生,發(fā)送中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位。

3. DMA發(fā)送完畢:此條件(DTxFDIE)當(dāng)DMA發(fā)送完一幀時產(chǎn)生,發(fā)送中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位。

4. DMA發(fā)送BUFFER描述符指針空:此條件(DTxNLIE)當(dāng)當(dāng)前DMA發(fā)送BUFFER描述符中指向下一個描述符的指針為空時產(chǎn)生。發(fā)送中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位。并重新初始化發(fā)送BUFFER描述符鏈表。

5. DMA發(fā)送BUFFER描述符不屬于DMA所有:此條件(DTxNOIE)當(dāng)當(dāng)前DMA發(fā)送BUFFER描述符不屬于DMA所有時發(fā)生。發(fā)送中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位。

對于HDLC通道接收中斷:

1. 接收Abort:此條件(RxABTIE)當(dāng)接收到Abort幀時產(chǎn)生,接收中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位。

2. DMA接收完畢:此條件(DRxFDIE)當(dāng)DMA接收到一個完整幀時發(fā)生,接收中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位。

3. DMA接收BUFFER描述符指針空:此條件(DRxNLIE)當(dāng)當(dāng)前DMA接收BUFFER描述符中指向下一個描述符的指針為空時產(chǎn)生。接收中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位。并重新初始化接收BUFFER描述符鏈表。

4. DMA接收BUFFER描述符不屬于DMA所有:此條件(DRxNOIE)當(dāng)當(dāng)前DMA接收BUFFER描述符不屬于DMA所有時發(fā)生。此時DMA接收被自動禁止。因此接收中斷處理程序中必須清除HDLC狀態(tài)寄存器(HSTAT)中的相應(yīng)位,并作相應(yīng)的錯誤處理,避免再次發(fā)生這種錯誤,然后使能DMA接收功能,否則不能繼續(xù)接收數(shù)據(jù)。

3.1.5:站址寄存器(HSAR0-HSAR3)和站址屏蔽寄存器(HMASK)初始化 4510利用在4個站址寄存器(HSAR0-HSAR3)中保存的站點地址配合站址屏蔽寄存器(HMASK)完成接受過程中的地址比較功能,如果一個 HDLC數(shù)據(jù)幀的地址不符,此幀將被簡單地丟棄而不做任何處理。具體的設(shè)置請參閱4510數(shù)據(jù)手冊。

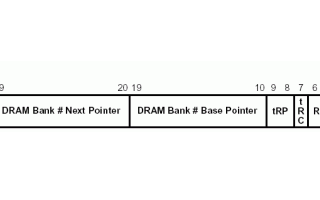

3.1.6:DMA收發(fā)BUFFER描述符鏈表結(jié)構(gòu)建立和指針寄存器初始化 4510的HDLC通道利用BUFFER描述符這種數(shù)據(jù)結(jié)構(gòu)完成DMA操作,接收和發(fā)送BUFFER 描述符以及描述符鏈表結(jié)構(gòu)分別如附圖2,3,4所示。我們的應(yīng)用中,建立了雙向環(huán)形鏈表的鏈表結(jié)構(gòu),而不是單向環(huán)形鏈表結(jié)構(gòu),雙向環(huán)形鏈表結(jié)構(gòu)與單項環(huán)形鏈表結(jié)構(gòu)不同的地方是每個鏈表中的元素多了一個指向前一元素的指針。這樣在軟件中進(jìn)行鏈表操作時不用每次都遍歷整個鏈表,提高了處理速度。 鏈表結(jié)構(gòu)建立后,需要初始化收發(fā)描述符指針寄存器,對于發(fā)送BUFFER描述符指針寄存器(HDMATxPTR),將發(fā)送BUFFER描述符鏈表結(jié)構(gòu)的頭節(jié)點地址寫入其中,之后每完成一次DMA發(fā)送操作,4510會自動更新其中的地址,指向下一個發(fā)送BUFFER描述符;對于接收BUFFER描述符指針寄存器(HDMARxPTR),將接收BUFFER描述符鏈表結(jié)構(gòu)的頭節(jié)點地址寫入其中,之后每完成一次DMA接收操作,4510會自動更新其中的地址,指向下一個接收BUFFER描述符。

3.1.7:使能HDLC通道的收發(fā)功能 所有的初始化工作做完后,就可以使能HDLC通道的收發(fā)功能。此時要分兩種情況:

一:如果使用DMA方式收發(fā),則需要使能HDLC通道控制寄存器(HCON)中的TxEN,RxEN,DTxEN,DRxEN四個比特位。不過,一般在發(fā)送時,有數(shù)據(jù)后才需要打開發(fā)送使能。

二:如果使用CPU方式收發(fā),則需要使能HDLC通道控制寄存器(HCON)中的TxEN,RxEN兩個比特位,DTxEN,DRxEN兩個比特位一定不能打開。

3.2: HDLC通道數(shù)據(jù)發(fā)送及中斷處理過程

3.2.1:HDLC通道數(shù)據(jù)發(fā)送過程 DMA方式下HDLC通道的數(shù)據(jù)發(fā)送過程可分為以下幾個步驟:

1. 讀取發(fā)送幀描述符指針寄存器HDMATxPTR,得到當(dāng)前發(fā)送幀描述符的地址,進(jìn)而得到整個發(fā)送幀描述符的內(nèi)容。

2. 得到發(fā)送幀描述符中幀數(shù)據(jù)BUFFER起始地址。

3. 將準(zhǔn)備好的HDLC幀拷貝到BUFFER中。

4. 設(shè)置當(dāng)前幀描述符中的相應(yīng)控制位。

5. 將發(fā)送幀描述符的OWERSHIP位設(shè)置為DMA所有。

6. 使能HDLC的DMA發(fā)送。 完成上面各步驟后,HDLC通道的DMA機(jī)制會自動將BUFFER中的數(shù)據(jù)拷貝到HDLC通道 的TxFIFO中發(fā)送出去。一幀發(fā)送完畢后,4510自動將已使用的發(fā)送BUFFER描述符的OWERSHIP位設(shè)置為CPU所有,并將幀描述符指針寄存器HDMATxPTR中的內(nèi)容更新為下一個未使用的發(fā)送BUFFER描述符地址。

3.2.2:HDLC通道數(shù)據(jù)發(fā)送中斷處理過程 當(dāng)一幀數(shù)據(jù)通過DMA方式發(fā)送完畢,或者發(fā)送過程中出現(xiàn)了可引起中斷的異常情況,此時軟件會進(jìn)入中斷處理程序。引起中斷的情況中斷控制寄存器的設(shè)置中已做了說明。在我們的編程中,HDLC通道發(fā)送中斷處理過程主要完成以下一些功能:

1. 進(jìn)入中斷后,首先清除4510中斷指示寄存器INTPEND中相應(yīng)的標(biāo)志位。

2. 如果DMA發(fā)送成功,則進(jìn)行數(shù)據(jù)幀發(fā)送成功狀態(tài)計數(shù),并清除HDLC通道狀態(tài)寄存器HSTAT中的相應(yīng)狀態(tài)位。

3. 如果發(fā)送出現(xiàn)異常,則完成相應(yīng)的異常狀態(tài)計數(shù),并清除HDLC通道狀態(tài)寄存器HSTAT中的相應(yīng)位。

4. 做完上述處理可關(guān)閉HDLC通道的DMA發(fā)送功能,等待有數(shù)據(jù)需要發(fā)送時再重新打開,也可以不關(guān)閉。

其中有兩個異常會影響以后的DMA操作,

一:發(fā)送下沖異常(TxU),發(fā)生此異常時,處理器會自動禁止DMA發(fā)送功能,因此下一次發(fā)送時必須重新使能DMA發(fā)送功能;

二:下一個發(fā)送幀描述符指針為空異常(DTxNL),發(fā)生此異常時,說明建立的DMA發(fā)送BUFFER描述符鏈表結(jié)構(gòu)出現(xiàn)了錯誤,因此需要重新初始化DMA發(fā)送BUFFER描述符鏈表結(jié)構(gòu)。

?3.3: HDLC通道數(shù)據(jù)接收工作原理及中斷處理過程

3.3.1:HDLC通道數(shù)據(jù)接收工作原理 DMA方式下HDLC通道的數(shù)據(jù)接收工作主要在HDLC通道初始化和DMA接收中斷處理中完成,這里主要分析HDLC通道接收工作原理,明白了數(shù)據(jù)接收原理,會給我們編程帶來極大的方便。HDLC通道接收工作原理如下所述:

1. 通道初始化階段,我們建立并初始化了HDLC接收BUFFER描述符鏈表結(jié)構(gòu),并將鏈表頭節(jié)點的地址寫入到HDLC接收BUFFER描述符指針寄存器 HDMARxPTR,這是正確完成DMA方式接收的前提,下面的工作都是在這個前提下自動完成的。

2. 當(dāng)有數(shù)據(jù)到來時,DMA機(jī)制會從HDMARxPTR指向的接收BUFFER描述符中找到接收BUFFER起始地址,然后把收到的數(shù)據(jù)寫入到BUFFER 中。

3. 如果接收無誤,4510自動更新HDMARxPTR寄存器的值,使其指向下一個還未使用的接收BUFFER描述符,以備下一次接收使用。使用過的接收 BUFFER描述符的OWERSHIP位將自動設(shè)置為CPU所有,因此為了能再次使用這個接收BUFFER描述符,必須將它的OWERSHIP位重置為 DMA所有。

4. 可以對已存儲在接收BUFFER中的數(shù)據(jù)作各種自定義的操作,實現(xiàn)自定義功能。

3.3.2:HDLC通道數(shù)據(jù)接收中斷處理過程 DMA方式下HDLC通道接收完一幀數(shù)據(jù),或者接收過程中出現(xiàn)了可引起中斷的異常情況,此時軟件會進(jìn)入中斷處理程序。引起中斷的情況在HDLC通道初始化的步驟4,即中斷控制寄存器的設(shè)置中已做了說明。在我們的編程中,HDLC通道接收中斷處理過程主要完成以下一些功能:

1. 進(jìn)入中斷后,首先清除4510中斷指示寄存器INTPEND中相應(yīng)的標(biāo)志位。

2. 如果DMA接收正確,則進(jìn)行數(shù)據(jù)幀接收成功狀態(tài)計數(shù),并清除HDLC通道狀態(tài)寄存器HSTAT中的相應(yīng)狀態(tài)位。對接收到的數(shù)據(jù)幀作相應(yīng)的處理后,要重新將是用過的接收BUFFER描述符的OWERSHIP位設(shè)置為DMA所有。 3. 如果接收出現(xiàn)異常,則完成相應(yīng)的異常狀態(tài)計數(shù),并清除HDLC通道狀態(tài)寄存器HSTAT中的相應(yīng)位。其中有兩個異常會影響以后的DMA操作,

一:DMA接收BUFFER描述符不屬于DMA所有(DRxNO);

二:DMA接收BUFFER描述符指針空(DRxNL)。發(fā)生這兩個異常時,說明接收BUFFER 描述符雙向環(huán)形鏈表結(jié)構(gòu)出現(xiàn)錯誤,處理器會自動禁止DMA發(fā)送功能,因此建議重構(gòu)接收BUFFER描述符雙向環(huán)形鏈表結(jié)構(gòu)并重新使能DMA發(fā)送功能。

4:S3C4510B的HDLC通道使用中的注意事項 我們編寫了4510的HDLC通道底層驅(qū)動程序,并應(yīng)用在了我們的155M SDH設(shè)備軟件中。通過對軟件的調(diào)試,感覺在使用4510的HDLC通道時,需要注意下面的問題:

1. 發(fā)送和接收數(shù)據(jù)大端/小端模式要一致,否則收到的數(shù)據(jù)與發(fā)送的數(shù)據(jù)高字節(jié)和低字節(jié)顛倒。

2. 使用DMA模式收發(fā)數(shù)據(jù)時,正常狀態(tài)下進(jìn)入中斷后,讀取發(fā)送BUFFER描述符指針寄存器(HDMATxPTR)或接收BUFFER描述符指針寄存器(HDMARxPTR)的內(nèi)容時,他們指向的都是下一個未用的BUFFER描述符。因此想處理接收到的數(shù)據(jù)或者初始化用過的發(fā)送BUFFER描述符時,需要指回到它們。

3. 使用DMA方式時,發(fā)送和接收BUFFER描述符在使用時的OWERSHIP位必須是DMA所有。因為發(fā)送是主動的,所以當(dāng)把數(shù)據(jù)放進(jìn)BUFFER描述符后,可以設(shè)置OWERSHIP位,然后啟動DMA發(fā)送;而接收是被動的,因此數(shù)據(jù)到來前,將要使用的BUFFER描述符必須是DMA所有,這就是每次進(jìn)入接收中斷后需要重置接收BUFFER描述符OWERSHIP位的原因。

4. 當(dāng)發(fā)送端的時鐘信息無法傳遞到接收端時,最好使用DPLL或者發(fā)送前導(dǎo)碼,以便接收端能夠恢復(fù)發(fā)送端的時鐘信息。

5. 當(dāng)使用外部時鐘源發(fā)送或接收數(shù)據(jù)時,注意數(shù)據(jù)采樣點和外部時鐘源的配合。我們的設(shè)備中一塊芯片為4510的HDLC通道提供時鐘,它在時鐘上升沿發(fā)送,下降沿接收,4510的HDLC通道默認(rèn)模式是時鐘下降沿發(fā)送,上升沿接收。我們以這種模式收發(fā)數(shù)據(jù),存在嚴(yán)重的數(shù)據(jù)不穩(wěn)定問題,當(dāng)改為上升沿發(fā)送,下降沿接收后,完全正常。因此數(shù)據(jù)采樣點的配合很重要。

6. 4510的HDLC通道收發(fā)方式還可以采用中斷方式,由于時間緊迫和能力有限,我們的程序沒有實現(xiàn),有興趣地可以參考4510數(shù)據(jù)手冊實現(xiàn)中斷方式收發(fā)。

5:總結(jié) KS4510B是一款性價比很高的ARM處理器,功能豐富,編程簡單,并且可以配合幾種嵌入式實時操作系統(tǒng),如pSOS,NUCLEUS等。我們的 155M SDH傳輸設(shè)備中,使用4510B和NUCLEUS操作系統(tǒng),完成了底層控制軟件。經(jīng)過調(diào)試,該軟件性能穩(wěn)定,其中HDLC通道完成了私有網(wǎng)管協(xié)議在 SDH環(huán)網(wǎng)上的傳輸轉(zhuǎn)發(fā),實現(xiàn)了遠(yuǎn)程管理的功能。 隨著各種電子,通訊產(chǎn)品對性能要求的日益提高,基于先進(jìn)的ARM架構(gòu)的各種32位微處理器也將得到越來越廣泛的應(yīng)用。因此,掌握了ARM處理器的使用和編程方法,必然能在工作中事半功倍,得到良好的結(jié)果和收益。

電子發(fā)燒友App

電子發(fā)燒友App

評論