濾波電路)。(3)注意晶振布線。晶振與單片機引腳盡量靠近,用地線把時鐘區隔離起來,晶振外殼接地并固定。此措施可解決許多疑難問題。(4)電路板合理分區,如強、弱信號,數字、模擬信號。盡可能把干擾源(如

2018-09-06 09:53:44

成本時總是要求設計者在設計中使用雙層電路板。雖然多層板(四層、六層以及八層)的解決方式無論在尺寸、噪聲,以及性能上都可以做得更好,但成本壓力迫使工程師必須盡量使用雙層板。在本文中將討論使用或不用自動布線

2016-04-28 11:45:56

1000倍。結論當一系統混合數字與模擬組件時,仔細布線是電路板成功與否的關鍵。尤其,靠近高阻抗模擬走線的經常變化之數字走線將造成嚴重的耦合噪聲,只有讓這兩種走線保持距離方可避免這種現象。更多學習交流可以加Q群310341439

2016-01-22 14:45:45

走線經常變化之數字走線將造成嚴重耦合噪聲,只有讓這兩種走線保持距離方可避免這種現象。本文量化了最棘手電路板寄生組件、電路板電容,并列舉可清楚看到電路板上性能例子來說明。 非必要電容帶來困擾 兩條

2018-09-10 16:56:40

。 5、降低噪聲和電磁干擾原則 (1) 盡量采用45°折線而不是90°折線(盡量減少高頻信號對外的發射與耦合); (2)用串聯電阻的方法來降低電路信號邊沿的跳變速率; (3) 石英晶振外殼要

2018-09-20 11:12:35

)地線設計。在DSP電路中,接地是控制干擾的重要方法,如能將接地和屏蔽正確結合起來使用,可解決大部分干擾問題。在一塊電路板上,DSP控制器同時集成了數字電路和模擬電路,設計電路板時,應使它們盡量分開

2018-09-03 11:18:48

如題目,電路板信號經過一級三極管,兩級運放放大,電路板不動的時候,電路正常工作;電路板震動的時候,電路自動產生干擾信號,干擾信號波形與振鈴波形類似,震動停止則干擾波形消失。第一次遇到這種問題,上論壇來請教下大家。

2019-05-13 03:25:58

如題目,電路板信號經過一級三極管,兩級運放放大,電路板不動的時候,電路正常工作;電路板震動的時候,電路自動產生干擾信號,干擾信號波形與振鈴波形類似,震動停止則干擾波形消失。第一次遇到這種問題,上論壇來請教下大家。

2019-02-21 10:31:14

造成電路板焊接缺陷的因素有以下三個方面的原因:1、電路板孔的可焊性影響焊接質量電路板孔可焊性不好,將會產生虛焊缺陷,影響電路中元件的參數,導致多層板元器件和內層線導通不穩定,引起整個電路功能失效

2018-03-11 09:28:49

造成線路板焊接缺陷的因素有以下三個方面的原因: 1、電路板孔的可焊性影響焊接質量 電路板孔可焊性不好,將會產生虛焊缺陷,影響電路中元件的參數,導致多層板元器件和內層線導通不穩定,引起整個電路

2018-09-21 16:35:14

很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設計印刷電路板的時候,應注意采用正確的方法。 一、地線設計在電子設備中,接地是控制干擾的重要方法。如能將接地和屏蔽正確結合起來使用,可解決

2014-11-14 09:55:11

|艾|姆|P|CB樣板貼片,麥1斯1艾1姆1科1技全國1首家P|CB樣板打板在實際電路中,造成電磁干擾的信號往往是脈沖信號,脈沖信號包含豐富的高頻成分,因此會在地線上產生較大的電壓。對于數字電路而言

2013-10-11 10:58:18

,這就是地線噪聲。在這個電壓的驅動下,會產生地線環路電流,形成地環路干擾。當兩個電路共用一段地線時,會形成公共阻抗耦合。解決地環路干擾的方法有切斷地環路,增加地環路的阻抗,使用平衡電路等。解決公共阻抗耦合的方法是減小公共地線部分的阻抗,或采用并聯單點接地,徹底消除公共阻抗。

2018-09-13 15:58:38

如圖2所示。 此電路板上,設計出的環路面積為697cm2。采用圖3所示的方法,電路板上或電路板外的輻射噪聲在環路中感應電壓的可能性可大為降低。 模擬和數字領域布線策略的不同之處 地平面是個難題

2010-01-29 09:53:33

電壓,這就是地線噪聲。在這個電壓的驅動下,會產生地線環路電流,形成地環路干擾。當兩個電路共用一段地線時,會形成公共阻抗耦合。解決地環路干擾的方法有切斷地環路,增加地環路的阻抗,使用平衡電路等。解決公共阻抗耦合的方法是減小公共地線部分的阻抗,或采用并聯單點接地,徹底消除公共阻抗.

2018-09-04 16:31:28

小結地線造成電磁干擾的主要原因是地線存在阻抗,當電流流過地線時,會在地線上產生電壓,這就是地線噪聲。在這個電壓的驅動下,會產生地線環路電流,形成地環路干擾。當兩個電路共用一段地線時,會形成公共阻抗耦合

2012-02-20 14:20:42

所示。此電路板上,設計出的環路面積為697cm2。采用圖3所示的方法,電路板上或電路板外的輻射噪聲在環路中感應電壓的可能性可大為降低。2 模擬和數字領域布線策略的不同之處2.1 地平面是個難題電路板布線

2016-06-22 12:03:52

所示。此電路板上,設計出的環路面積為697cm2。采用圖3所示的方法,電路板上或電路板外的輻射噪聲在環路中感應電壓的可能性可大為降低。2 模擬和數字領域布線策略的不同之處2.1 地平面是個難題電路板布線

2016-06-23 10:01:29

電路板上,設計出的環路面積為697cm2。采用圖3所示的方法,電路板上或電路板外的輻射噪聲在環路中感應電壓的可能性可大為降低。模擬和數字領域布線策略的不同之處 地平面是個難題 電路板布線的基本知識既

2018-11-23 11:09:06

在此單面板中,到電路板上器件的電源線和地線彼此靠近。此電路板中電源線和地線的配合比圖2中恰當。電路板中電子元器件和線路受電磁干擾(EMI)的可能性降低了679/12.8倍或約54倍 對于控制器和處理器

2011-09-02 09:36:14

PCB電路板怎樣布線_印制線路板布線訣竅分享_華強PCB 我知道很多人都談論過PCB的布線經驗,但是我在這里想分享一下我自己的感覺,和別的大師是有細微的差別的,希望大家能夠喜歡。 一般個人

2018-01-23 09:59:41

,地線的種類有很多,有系統地、屏蔽地、邏輯地、模擬地等,地線是否布局合理,將決定電路板的抗干擾能力。在設計地線和接地點的時候,應該考慮以下問題: 邏輯地和模擬地要分開布線,不能合用,將它們各自的地線分別

2018-09-11 16:05:35

PCB電路板是對零散的電子元件進行組合,可以保證電路設計的規則性,并很好的避免人工排線與接線容易造成的混亂及錯誤問題。PCB電路板的設計是電路板生產制造的基礎,下面我們來看看PCB電路板的設計流程

2019-04-15 07:35:02

(1)高頻電路往往集成度較高,布線密度大,采用多層板既是布線所必須的,也是降低干擾的有效手段。 中國IC交易網(2)高速電路器件管腳間的引線彎折越少越好。高頻電路布線的引線最好采用全直線,需要轉折

2019-01-15 13:31:06

接地,以減小相互干擾。 放在電路板邊緣。3 提高敏感器件的抗干擾性能,敏感器件盡量減少對干擾噪聲的拾取。1)布線時盡量減少回路環的面積,以降低感應噪聲。2)布線時,電源線和地線要盡量粗。除減小壓降外

2020-11-10 10:43:02

電路板上,設計出的環路面積為697cm2。采用圖3所示的方法,電路板上或電路板外的輻射噪聲在環路中感應電壓的可能性可大為降低。 模擬和數字領域布線策略的不同之處 地平面是個難題 電路板布線

2018-09-20 10:51:10

耦合,高頻時常見的輻射耦合,切斷其耦合途徑是在設計時務必應該給予充分重視的。本文主要講解PCB設計時要注意的地方,從而減低PCB板中的電磁干擾問題 PCB的設計原則 由于電路板集成度和信號頻率隨著

2018-09-21 11:51:38

的噪聲耦合。 3 結束語 本文所介紹的各種方法與技巧有利于提高PCB的EMC特性,當然這些只是EMC設計中的一部分,通常還要考慮反射噪聲,輻射發射噪聲,以及其他工藝技術問題引起的干擾。在實際的設計中,應根據設計的目標要求和設計條件,采用合理的抗電磁干擾措施,設計出具有良好EMC性能的PCB電路板。:

2018-09-11 15:07:53

。電源在向系統提供能源的同時,也將其噪聲加到所供電的系統中,系統中的復位、中斷以及其它一些控制信號最易受外界噪聲的干擾,所以,應該適當增加電容來濾掉這些來自電源的噪聲。 5)注意電路板與元器件的高頻特性

2009-03-25 08:29:05

;nbsp; 2.3 印制電路板的抗干擾設計 電路板是微機系統中器件、信號線、電源線高密度集合體,對抗干擾性能影響很大,電路板設計、布線及接地不妥可能使整個系統

2010-02-24 12:10:44

措施可解決許多疑難問題。(4)電路板合理分區,如強、弱信號,數字、模擬信號。盡可能把干擾源(如電機,繼電器)與敏感元件(如單片機)遠離。(5)用地線把數字區與模擬區隔離,數字地與模擬地要分離,最后在一

2015-02-05 17:44:48

的影響。注意高頻電容的布線,連線應靠近電源端并盡量粗短,否則,等于增大了電容的等效串聯電阻,會影響濾波效果。{讀一下電視機的原理圖或檢查下電路板就知道這句話是對是錯?}(5)布線時避免90度折線,減少高頻噪聲

2016-10-08 21:15:58

直接耦合到放大器輸入端,造成干擾。在PCB布線時,要注意電源線與弱信號線不要貼近平行走線,線凈距大于線寬的3倍(3W原則),并在電源線或數字信號線與模擬小信號線之間加地線隔離。接地處理不當,噪聲通過

2018-03-28 17:14:04

減小電磁干擾的印刷電路板設計原則印刷電路板PCB 的一般布局原則在一些相對難懂的文件中得到總結一些原則是特殊適用于微控制器的然而這些原則卻被試圖應用到所有的現代CMOS 集成電路上這個文件覆蓋

2008-07-13 11:35:45

、電感引線要盡量短。(4)電路板上每個IC要并接一個0.01μF~0.1μF高頻電容,以減小IC對電源的影響。注意高頻電容的布線,連線應靠近電源端并盡量粗短,否則,等于增大了電容的等效串聯電阻,會影響濾波

2018-08-28 17:54:26

。減小差模干擾的主要方法是布線時盡量減短走線長度, 減小信號環路面積。2.2 PCB電路板上干擾源產生方式高速數字電路各類干擾的主要產生原因是由電源自身固有噪聲頻率及外部線路上各類變化的di/dt

2011-07-16 11:50:08

達到良好結果時,即使在一個簡單電路布線設計中存在小差異,都將導致無法達到最佳效果。本文中將探討模擬與數字布線間基本異同,有關旁路電容、電源供應以及接地布線、電壓誤差,以及因電路板布線造成電磁干擾(EMI

2018-09-12 15:35:58

。 6.PROTEL的DXP手動修改布線根據抗干擾線路調整電路板布線原則,不僅僅是要求布敦,考慮到許多因素,特別是所依據的原則,使布線干擾。例如,串擾和阻抗控制。由于鄰近信號耦合將導致串擾并改變

2018-09-14 16:29:44

影響。(3)給電機加濾波電路,注意電容、電感引線要盡量短。(4)電路板上每個IC要并接一個0.01μF~0.1μF高頻電容,以減小IC對電源的影響。注意高頻電容的布線,連線應靠近電源端并盡量粗短,否則

2019-07-01 09:34:21

去掉。另外,在單片機系統中,最容易受影響的是復位線、中斷線和控制線。 1、干擾的耦合方式 (1)傳導性EMI 一種最明顯而往往被忽略的能引起電路中噪聲的路徑是經過導體。一條穿過噪聲環境的導線可撿拾噪聲

2018-12-20 09:44:50

原因是多方面的。不僅有外界因素造成的干擾(如電磁波),而且印制電路板絕緣基板的選擇、布線不合理、元器件布局不當等都可能造成干擾,這些干擾在電路設計和排版設計中如予以重視,則可完全避免。相反,如果不在

2018-09-19 16:16:06

很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設計印制電路板的時候,應注意采用正確的方法。 一、地線設計在電子設備中,接地是控制干擾的重要方法 如能將接地和屏蔽正確結合起來

2018-09-18 15:40:00

影響。例如,如果印制板兩條細平行線靠得很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設計印制電路板的時候,應注意采用正確的方法。一、地線設計 在電子設備中,接地是控制干擾的重要方法。如能

2018-08-24 16:48:13

振下方所在的布線層。 8、PCB布線 這一步驟包括了手工布線、自動布線和手工調整三個小步。 9、電路板的引出端的處理 在實際PCB設計中,電源、接地、信號的輸入和輸出等端必須與外界相連,引出

2020-06-24 15:35:20

印制板兩條細平行線靠得很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設計印制電路板的時候,應注意采用正確的方法。一、 地線設計在電子設備中,接地是控制干擾的重要方法

2009-03-25 11:47:51

很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,在設計印制電路板的時候,應注意采用正確的方法。 在電子設備中,接地是控制干擾的重要方法。如能將接地和屏蔽正確結合起來使用,可解決大部分干擾

2018-08-28 11:58:34

阻抗的耦合、輻射和串擾等問題。在輸入輸出端放置緩沖器,用于板間信號傳送,可有效防止噪聲干擾。 電路板上裝有高壓、大功率器件時,與低壓、小功率器件應保持一定間距,盡量分開布線。在大功率、大電流元器件周圍

2013-09-09 11:01:48

很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,深圳捷多邦科技有限公司的工程師提出了在設計印制電路板的時候,應注意采用正確的方法。 A、地線設計在電子設備中,接地是控制干擾的重要方法

2018-09-12 15:34:27

電子設備的可靠性產生不利影響。例如,如果印制板兩條細平行線靠得很近,則會形成信號波形的延遲,在傳輸線的終端形成反射噪聲。因此,建議設計印制電路板的時候,應注意接地是控制干擾的重要方法。如能將接地和屏蔽

2018-02-26 12:15:21

和印制線的抗剝離強度大大增加。島形焊盤多用在高頻電路中,它可以減少接點和印制導線的電感,增大地線的屏蔽面積,減少接點間的寄生耦合。 設計印制電路板時,當元器件布局和布線初步確定后,就要具體地設計印制

2023-04-20 15:21:36

正常工作,同時又能減少電子設備本身對其它電子設備的電磁干擾。印刷電路板(PCB)設計中的電磁兼容性涉及多方面因數,以下主要從三大部分加以闡述,具體選擇要綜合各方面因數。 一 印刷電路板整體布局及器件

2018-11-27 10:12:53

,一端接地為好。 對噪聲和干擾非常敏感的電路或高頻噪聲特別嚴重的電路,應該用金屬罩屏蔽起來。鐵磁屏蔽對500KHz的高頻噪聲效果并不明顯,薄銅皮屏蔽效果要好些。使用鏍絲釘固定屏蔽罩時,要注意不同材料接觸時引起的電位差造成的腐蝕。還有不少內容,有需要可以下載看看!

2012-09-06 11:25:33

隔離; (7)特別注意電流流通中的導線環路尺寸; (8)如有可能,在控制線(于印刷板上)的入口處加接R-C濾波器去耦,以便消除傳輸中可能出現的干擾因素。 3.11 PCB布線通用規則: 在設計印制線路板

2018-09-10 16:28:15

引起的噪聲干擾最大。二、印刷電路板圖設計的基本原則要求 1.印刷電路板的設計,從確定板的尺寸大小開始,印刷電路板的尺寸因受機箱外殼大小限制,以能恰好安放入外殼內為宜,其次,應考慮印刷電路板與外接元器件

2019-01-14 06:36:18

板上的傳播和將噪聲引導到地。干擾的耦合方式干擾源產生的干擾信號是通過一定的耦合通道對電控系統發生電磁干擾作用的。干擾的耦合方式無非是通過導線、空間、公共線等作用在電控系統上。分析下來主要有以下幾種

2020-12-02 09:34:28

過程,可以在連線上產生很大的dv/dt和di/dt的信號。它可以耦合到其它連線上造成電磁干擾。因而元件的選擇對于控制電磁干擾(EMI)至關重要,而且電路板的布局和連線也具有同等重要的影響。 2.1

2009-10-10 09:15:44

經驗的設計人員來說,在完成元器件的預布局后,會對 PCB 的布線瓶頸處進行重點分析 結 完成元器件的預布局后的布線瓶頸處進行重點分析 頸處進行重點分析。結 完成元器件的預布局后工具分析電路板的布線密度

2018-09-13 16:08:17

如何消除噪聲干擾,提高測量的精準度?

2021-05-10 06:29:35

噪聲源:馬達馬達啟動或停止的瞬間,電路板與PC之間的USB信號收到干擾,導致USB設備連接斷開。

2013-02-23 18:15:49

電氣噪聲環境中運行。電氣噪聲通常通過工廠自動化設備中的中央直流(DC)電源背板傳輸。隔離變壓器可以去除不必要的噪聲,但是如何在直流電源上使用變壓器呢?使用反激式電源轉換器。隔離式電源可以通過消除接地

2022-11-15 07:11:51

[]鍵,編輯菜單。手動調節,如圖10所示的董事會。 6.PROTEL的DXP手動修改布線根據抗干擾線路調整電路板布線原則,不僅僅是要求布敦,考慮到許多因素,特別是所依據的原則,使布線干擾。例如,串擾

2013-10-09 11:01:33

工程課程一般不會教授如何實現良好的電路板布局布線。高頻RF類課程會研究走線阻抗的重要性,但需要自行構建系統電源的工程師,通常不會將電源視為高頻系統,而忽視了電路板布局布線的重要性。 了解本文所述電路板布局布線準則背后的理由并嚴格遵守,將能夠把開關模式電源的任何PCB相關問題降到最小。 ...

2021-11-15 08:27:59

的工廠和車間里會有各種各樣的干擾源:發動機、電動機、熒光燈、無線電設備、發電機等。每種干擾源都會輻射出能被線路、電路板和測量模塊接受的電磁噪聲。即使采取最好的屏蔽和接地措施,這些干擾也會在信號測量中以

2011-09-02 12:38:13

輸出的濾波,對于PCB漏電,可在信號輸入引線與電源走線間加地線防護。

噪聲可能通過PCB走線之間的分布電容直接耦合到放大器輸入端,造成干擾。在PCB布線時,要注意電源線與弱信號線不要貼近平行走線,線

2023-11-21 06:27:27

與電源走線間加地線防護。噪聲可能通過PCB走線之間的分布電容直接耦合到放大器輸入端,造成干擾。在PCB布線時,要注意電源線與弱信號線不要貼近平行走線,線凈距大于線寬的3倍(3W原則),并在電源線或

2018-12-29 10:10:32

地之間的雜散電容形成環路,次級模擬電路中流過的共模電流流過不平衡的阻抗轉換成差模,對放大電路造成干擾(如圖6)。共模方式引入的干擾一般為開關噪聲中的高頻分量(數MHz以上)。措施主要有如下三點:提供一條

2017-10-19 23:34:27

抗干擾設計的基本任務是系統或裝置既不因外界電磁干擾影響而誤動作或喪失功能,也不向外界發送過大的噪聲干擾,以免影響其他系統或裝置正常工作。因此提高系統的抗干擾能力也是該系統設計的一個重要環節。 電路

2023-05-15 14:46:29

射頻(RF)電路板分區設計中PCB布局布線技巧

2012-08-16 16:51:47

考慮如何減小射頻電路中各部分之間的相互干擾、如何減小電路本身對其他電路的干擾以及電路本身的抗干擾能力。 根據經驗,射頻電路效果的好壞不僅取決于射頻電路板本身的性能指標,很大部分還取決于與CPU處理板間

2018-11-23 11:03:18

電流流過地線時,就會在地線上產生電壓,然后產生地線環路電流,構成地線的環路干擾。當多個電路共用一段地線時,就會構成公共阻抗耦合,然后產生所謂的地線噪聲。

因此,在對射頻電路板的地線進行布線時應該

2023-06-08 14:48:14

阻抗。當有電流流過地線時,就會在地線上產生電壓,然后產生地線環路電流,構成地線的環路煩擾。當多個電路共用一段地線時,就會構成公共阻抗耦合,然后產生所謂的地線噪聲。

因此,在對射頻電路板的地線進行布線

2023-05-13 14:23:43

/O口與噪聲源之 間應加隔離(增加π形濾波電路)。(3)注意晶振布線。晶振與單片機引腳盡量靠近,用地線把時鐘區隔離起來,晶振外殼接地并固定。此措施可解決許多疑難問題。(4)電路板合理分區,如強、弱信號

2018-08-29 10:53:56

的尺寸與器件的布置印制電路板大小要適中,過大時印制線條長,阻抗增加,不僅抗噪聲能力下降,成本也高;過小,則散熱不好,同時易受臨近線條干擾。在器件布置方面與其它邏輯電路一樣,應把相互有關的器件盡量放得

2015-02-09 15:37:15

完成的高頻電路板,該實用新型中的高頻電路板結構簡單,成本低,易于制造。PCB設計高頻電路板布線技巧一、高速電子器件管腳間的引線彎折越少越好高頻電路布線的引線最好采用全直線,需要轉折,可用45度折線或者

2018-11-18 22:14:48

布局后,會對PCB的布線瓶頸處進行重點分析。結合其他EDA工具分析電路板的布線密度;再綜合有特殊布線要求的信號線如差分線、敏感信號線等的數量和種類來確定信號層的層數;然后根據電源的種類、隔離和抗干擾

2018-08-24 06:48:42

的優越性23�多層板設計靈活�很容易在不同層數任何需要的地方保留銅箔�這些銅箔既可消除各關鍵電路之間的電耦合�使噪聲干擾或信號串擾減到最低�也可用來屏蔽內層與外層的某些關鍵電路的干擾4還可以利用大面積銅箔來

2008-08-15 01:14:56

和模擬電路在同一塊板卡上共享相同的元件時,電路的布局及布線必須講究方法。在混合信號PCB設計中,對電源走線有特別的要求并且要求模擬噪聲和數字電路噪聲相互隔離以避免噪聲耦合,這樣一來布局和布線的復雜性

2018-08-27 16:13:53

的噪聲。電源在向系統提供能源的同時,也將其噪聲加到所供電的系統中,系統中的復位、中斷以及其它一些控制信號最易受外界噪聲的干擾,所以,應該適當增加電容來濾掉這些來自電源的噪聲。 5)注意電路板與元器件

2012-10-24 14:35:15

濾波器。同樣,電源耦合測量和電源旁路濾波也可應用到射頻(RF)或圖像采集系統。在射頻系統中,發射端噪聲往往會降低接收端性能;在圖像采集系統中,CMOS攝像頭傳感器采用模擬電源供電,它對數字噪聲非常敏感。設計時應采用旁路濾波,以消除發射電路或攝像頭相關的數字電路所產生的噪聲。

2019-02-22 08:30:00

的耦合嗎?還有,是不是電源噪聲會對控制電壓線有干擾從而造成頻率抖動呢??我全都不是很確定,所以來這里求證,順便還望高人能夠補充,減小電源噪聲影響的措施有哪些呢?看到論文上說全差分可以減小電源噪聲

2021-06-24 06:11:40

所產生的干擾狀況稱為系統間的EMC 情況。大多數的設備中都有類似天線的特性的零件如電纜線、電路板布線、內部配線、機械結構等這些零件透過電路相耦合的電場、磁場或電磁場而將能量轉移。實際情況下,設備間

2019-05-16 09:48:42

。由于電源層遍及電路板的全面積,因此直流電阻非常小,可以有效地降低噪聲。 2.同類型信號線的分布 在設計PCB板時,對于處理器的輸入/輸出信號中的數據線、地址線等相同類型的線應該成組、平行分布,并

2018-09-05 16:38:26

、導線間耦合和電路結構的影響。在研制設計電路時,希望設計的印制電路板盡可能不易受外界干擾的影響,而且也盡可能小地干擾影響別的電子系統。設計印制板首要的任務是對電路進行分析,確定關鍵電路。這就是要識別

2020-11-23 12:17:20

如題高頻電路 印制電路板設計 在實際布線中需要注意些什么? 怎樣避免線路之間的干擾?

2013-02-27 11:17:20

呈現的阻抗,而阻抗指的是交流狀態下導線對電流的阻抗,這個阻抗主要是由導線的電感引起的。任何導線都有電感,當頻率較高時,導線的阻抗遠大于直流電阻,表1 給出的數據說明了這個問題。在實際電路中,造成電磁干擾

2015-01-14 13:58:40

耦合到各敏感源器件,同時電流環還會耦合進外部產生的各類干擾,影響正常的工作系統。減小差模干擾的主要方法是布線時盡量減短走線長度, 減小信號環路面積。 2.2 PCB電路板上干擾源產生方式 高速

2018-09-12 15:01:56

不論是PCB噴碼機、FPC噴碼機、電路板噴碼機,我們都曾經聽過很多,特別是電路板行業內的廠家、制造商企業,很多都開端應用油墨打碼或激光打標來替代人工,儉省人力本錢和進步效率,今天潛利就和大家分享一下

2023-08-17 14:35:11

消除噪聲干擾的PCB板設計原則

印刷電路板圖是一臺機器的框架藍本,決定著機器是否能安全可靠的工作。每一種儀器的

2009-04-07 22:18:01 1057

1057 信號。在電路板中,要求印刷電路板的(PCB)布線應盡量減少不同部件之間的耦合干擾。只有這樣,才能保證儀器的可靠性。

2019-09-18 11:04:17 11839

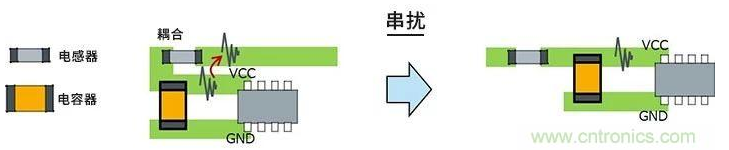

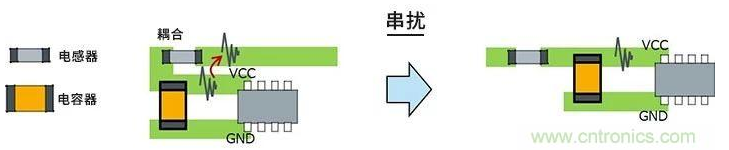

11839 串擾是因電路板布線間的雜散電容和互感,噪聲與相鄰的其他電路板布線耦合。下面是LC濾波器的圖形布局和部件配置帶來的串擾及其對策示例。

2020-02-17 16:48:26 2429

2429

電路板廠印制板進行布線設計的順序可能不同,在電路板廠布線設計師準備進行設計布線之前,他的電路設計規則中應該明確規定。

2020-06-04 17:58:37 1498

1498 在印制電路板設計階段對電磁兼容考慮將減少電路在樣機中發生電磁干擾。問題的種類包括公共阻抗耦合、串擾、高頻載流導線產生的輻射和通過由互連布線和印制線形成的回路拾取噪聲等。

2023-04-07 09:15:06 305

305 問題。那么,電路板損壞是什么造成的呢?以下將從不同方面詳細介紹。 1. 靜電干擾 靜電干擾是指在電路板表面或接觸點上產生的靜電電荷引起的電路干擾現象。如果在靜電能量較大的情況下,靜電放電會對接收器件產生極短的過電壓,

2023-08-29 16:58:50 3778

3778 RC電路能消除干擾嗎? RC電路是一種常見的電路元件組合,由電阻(R)和電容(C)組成。它在電子工程中被廣泛使用,是研究電子噪聲、濾波和干擾的主要技術之一。在電子線路中,干擾是一大問題,因為它可

2023-09-12 14:47:26 768

768 差模干擾(差模信號)是一種在差分信號傳輸系統中出現的干擾模式,這種干擾模式主要是由于電路板上兩條差分信號線的長度、寬度和間距等參數不一致所導致的。如果不采取有效的措施進行抑制和消除,差模干擾會對

2023-10-11 13:44:13 1067

1067

電子發燒友App

電子發燒友App

評論