信號完整性(SI)問題正成為數字硬件設計人員越來越關注的問題。由于無線基站、無線網絡控制器、有線網絡基礎架構及軍用航空電子系統中數據速率帶寬增加,電路板的設計變得日益復雜。

目前,芯片間高速串行鏈接已經獲得廣泛應用,以提高整體吞吐性能。處理器、FPGA及數字信號處理器可相互傳輸大量數據。此外,該數據可能必須從電路板發出,通過背板傳輸至交換卡,而交換卡可將數據發送至機箱內的其他卡或“系統”內的其他地方。支持RapidIO的交換可實現這些不同組件之間的互連,并廣泛用于滿足這些應用的實時帶寬需求。

本文主要探討涉及高速接口設計(RapidIO交換的主要功能支持這些高速接口設計)的信號完整性難題以及其他相關事項,優化RapidIO交換的功能旨在實現高速設計中較高的信號完整性。

高速接口設計難題

信號質量對于系統的各個方面均非常重要。對于串行RapidIO而言,信號質量通過接收眼圖的大小進行量化。接收眼圖是一個無限延續的軌跡,其中,波形會隨上一個軌跡不斷重復。眼圖開得越大,信號質量就越好。

信號質量可能受多方面的影響:信號通道中出現噪聲或其他雜亂信號、信號通道布線差、外部源的傳導或輻射、系統本身產生的噪聲。上述所有因素結合在一起會導致接收眼圖縮小。除電路板級問題外,信號完整性亦可能受到連接的源(傳輸端)及目的地(接收端)的影響。因此,應在整體系統級的信號完整性中考慮源及目的地的IC特點。

電路板級設計的考慮因素

就電路板設計而言,應考慮的常見因素包括:

1. 電路板的電源輸入、本地調節器的輸出及分配

2. 時鐘生成及分配

3. 退耦

4. PCB基礎材料

5. 芯片間連接

6. 電路板間連接及背板連接

7. 電路板層疊及阻抗控制

8. 機架間連接器、電纜及接頭

工作頻率高于300MHz時,適用于較低頻率電路板設計的大部分設計最佳慣例均需修改。必須考慮當波長與電路板尺寸可比時出現的因素。這不僅適用于基本頻率的波長,也適用于構成完整波形的傅立葉(頻域)分量。

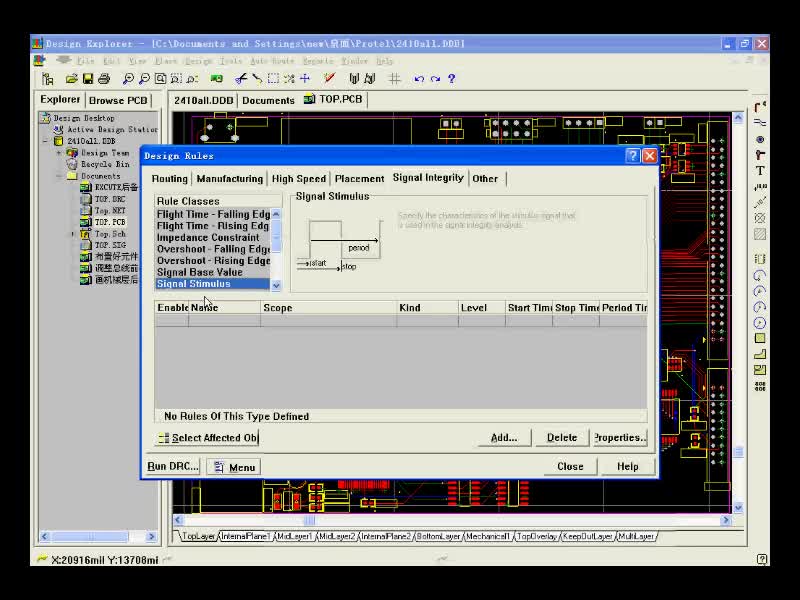

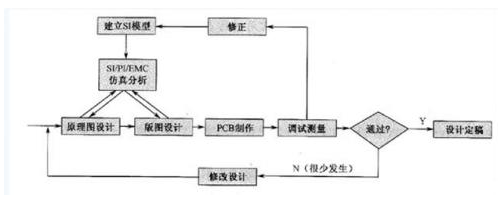

FR4材料仍可成功用作電路板的基礎材料,但在較高頻率下,不僅需要考慮材料的介電常數,還需要考慮損耗系數。過孔的設計也變得非常重要,因為未使用的管長部分(在較低頻率下其影響可以忽略)的阻抗會與較厚電路板及背板的阻抗不匹配。最好完成設計后仿真,以引起對信號完整性不太理想的布線的注意,并指出串擾區域。

電路板上信號完整性方面的特定難題是由于高速處理器總線及高速內存接口的存在、時鐘生成及時鐘噪音以及各種電路板噪音源而引起,通常包括:單端并聯總線、電源分配、阻抗匹配、接地彈跳、串音及時鐘生成。

串行RapidIO交換機

串行RapidIO互連可用于處理以上所討論的一些信號完整性難題。RapidIO是芯片間、電路板間及機箱間互連的一個成熟、開放標準,由嵌入式計算領域領導廠商設計,可滿足在無線基礎架構、網絡、存儲、科學、軍事及工業類市場中設備對可靠性、成本效益、性能及可擴展性的要求。

RapidIO是一個專為滿足當前及未來嵌入式應用需求而設計的點到點數據包交換互連協議。RapidIO物理層1x/4x鏈接串行規范可滿足使用電子串行連接的設備的物理層媒介要求。該規范定義了使用單向差分信號的設備之間的全雙工串行物理層接口(鏈接)。此外,對于需要更高鏈接性能的應用,它還允許將四個串行鏈接組合在一起。它還定義了用于鏈接管理及通過鏈接傳輸數據包的協議。

RapidIO系統的架構由端點元件及連接端點的交換結構組成。設想端點作為郵件系統中的出發點,交換機作為截取包裹并將包裹發送至目的地的郵局。RapidIO互連架構根據規范被劃分為層狀架構,包括邏輯層、公共傳輸層及物理層。RapidIO協議的物理層由芯片串行器-解串器(SerDes)處理。SerDes的特性對硬件設計人員在設計電路板時所面臨的信號完整性問題有一定的影響。交換機設計的許多其他方面也將影響信號完整性。

RapidIO 交換的特性簡化電路板設計并實現較高的信號完整性

時鐘生成

就啟動器而言,sRIO交換機必須具有實現低抖動的無噪時鐘信號。低抖動信號基本上具備低相位噪音的特性。若增加輸入時鐘信號以實現較高頻率的輸出信號,則必須優化芯片電路,以產生最小的相位噪音。Tundra的Tsi57x串行RapdIO交換機通過采用集成低噪音放大PLL的125MHz及155MHz時鐘產生高達3.125Ghz的輸出信號。許多產品采用獨立電路實現上述功能,因而無法像Tundra交換芯片一樣實現低抖動。輸出信號的清晰度也不如使用Tundra交換芯片時,使得電路板設計難以容忍上文論述的其他板級信號完整性問題。

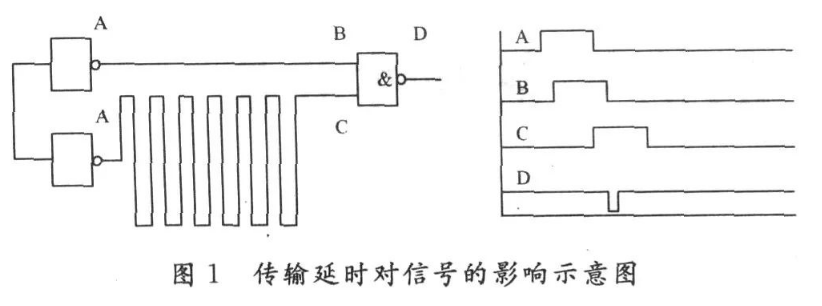

在高速電路板設計中,由于信號經過電路板由芯片傳輸至芯片或通過背板傳輸,因而需要考慮信號的衰減。簡而言之,實際信號在到達端點時強度會減小,并可能出現相移。通常,在所有媒介中,高頻率諧波較低頻率諧波衰減的比例更大。僅增強整體信號并不夠,因為它會擴大噪音層,并且沒有解決相移問題。串行RapidIO交換及端點(像GbE及10GbE等所有其他高速設計一樣)利用技術避免該問題并保持原始信號的完整性。

若要了解傳輸預加重及接收器均衡的影響,可以回顧眼圖,其目標是實現“開眼”。若未運用這些技術,眼圖會開始“閉合”。

傳輸預加重技術可將高頻加入傳輸信號,以解決信號衰減及端點間相移的問題。因此,與簡單地放大所有頻率(該方法亦會增加交換芯片的整體功耗)不同,傳輸預加重可通過傳輸功能有效增強輸出波形,增加輸出波形的高頻量,而同時使用虛擬組件對其進行相移,解決因傳輸媒介引致的相移。該方法對于保持信號的完整性及保持眼圖相當有效。

盡管傳輸預加重通常在許多高速IC中應用,以優化整體系統級的信號完整性,但“傳輸端”的傳輸預加重應與“接收端”的接收器均衡一并使用。接收器均衡運用增強器傳輸功能,補償因電路板及背板引起的高頻傳輸損耗及相移。由于這些傳輸損耗在信號到達目的地IC(在本文中,指串行RapidIO交換)前發生,因此通常在信號發送至系統中的下一個傳輸部分(另一交換)或端點前,交換機必須采取措施補償這些損耗。接收器均衡的功效與傳輸預加重類似,可改善整體信噪比。注意:連接至交換芯片的各鏈接可能具有不同的特性。

同樣,各鏈接的接收器均衡需要將各有不同,且需編程方可使用。所有Tundra RapidIO Tsi57x交換均具有該特性,而就信號完整性而言,該特征將大幅簡化系統級的設計。

同步與異步交換設計

串行RapidIO標準支持三種不同的鏈接速率:1.25G波特、2.5G波特及3.125G波特。交換可分為兩類:同步及異步。

同步交換指所有端口必須以相同速度運轉的交換。

異步交換指各端口可按特定鏈接的通信量需求所需的頻率運轉的交換。

在大部分應用中,最佳解決方案是異步交換,它不僅具有能以較低的系統整體功耗滿足通信量需求的優點,而且就信號完整性而言,它受串音的影響更小。

封裝及互連

信號完整性問題可能在很大程度上受封裝及基礎材料設計的影響。例如,高性能倒裝芯片及打線接合封裝可改善功率傳送并減少回程損耗。就RapidIO交換機而言,改善阻抗匹配以維持100歐姆差分阻抗及較低的變差相當重要。倒裝芯片封裝可有助于改善上述情況。

高效球狀映射

硅片供應商可能會選擇球狀映射簡化從芯片至球柵的信號傳輸,但其作用并非僅限于此。在理想情況下,設計球狀映射時會考慮整體系統級的實現。例如,在設計球狀映射時,須謹記將外圍IC鏈接至交換芯片。應對有關設計進行優化以最大程度減少層數及所需面積,這樣可改善最終設計的信號完整性。配有相當密集的球狀映射的IC在電路板上需要許多層,才能將信號從IC中發送出去,從而導致高成本的系統級設計。另一個問題是信號通道間的串音,該問題在上文討論同步及異步RapidIO交換的區別時已提及。與信號通道間串擾及高效球狀映射緊密相連的一個問題是電源與接地引腳之間的間隔。若將太多串行RapidIO端口插入小型封裝,可能會由于串擾而導致信號完整性問題,從而導致在信號從交換機傳輸到端點時出現“閉眼”。

設計慣例技巧

現在,我們回顧一下信號完整性的另一方面,即電路板級的設計問題。設計人員可以采取許多設計指引來控制噪聲產生的影響。通常,好的設計慣例可以幫助電路板設計人員控制電路板級通信產生的信號噪音,包括限制外部噪音源以及解決設備本身的噪音。

首先,所有設計均應采用正確的走線寬度、間隔及拓撲,以確保每個走線的阻抗與其傳輸器件匹配。阻抗不匹配可能會影響前緣與后緣的質量、穩定延遲時間、串擾以及EMI。

必須確保同步信號組之間有足夠的通道間隔,必須限制通道長度并將差分對信號之間的偏移降至最低。布線時應最大限度地減少布線層轉換次數,從而限制寄生效應。不必要的電感及雜散電容中的過孔成本非常高,應盡量減少。除BGA襯墊外,通常每個通道最多允許有兩個過孔。

對信號完整性徹底驗證至關緊要。利用估計寄生效應,設計前分析可提供了解設計性能所需的數據,但準確的后設計寄生效應可提供發現潛在信號完整性問題所需的詳情。采用該方法,可創建電路網表以進行模擬并記錄結果。

若盡可能縮短通道及信號通道,通過接地層或彼此物理隔離的方式進行屏蔽,并注意避免阻抗不匹配或任何導致共振的配置,即可獲得良好的信號完整性。

選擇串行RapidIO交換芯片,實現較高的信號完整性

設計人員如何選擇串行RapidIO交換?正如良好的設計慣例可以幫助電路板設計人員控制電路板級通信產生的信號噪音一樣,硬件設計人員需積極考慮時鐘生成的特性、傳輸預加重及接收器均衡、優化封裝技術、有效的球狀映射及異步設計的串行RapidIO交換機,方可確保系統級設計具有較高的信號完整性。顯然,在選擇串行接口時,設計人員選擇的芯片不僅要具有合適的功能,還必須是專為解決高速信號難題而設計的交換芯片。

目前,Tundra Semiconductor Corporation可提供具有以上特性的三代串行RapidIO交換產品。Tsi 57x產品線包括Tsi574、Tsi576及Tsi578,各款的端口數各不相同,介于4至16個端口之間,運轉速度介于1.25G至3.125G之間。各端口支持x1及x4通道可選,每端口的功耗為120至200mW。Tsi57x產品線具有本文所述的所有信號完整性的特征,包括傳輸預加重及接收器均衡。該產品較前款Tsi56x產品線增加了一些新功能,包括多播功能、矩陣性能監控。另外,許多高級通信管理功能已經優化,可滿足無線基站、無線網絡控制器、有線網絡基礎架構及軍用航空電子系統等應用的高性能要求。

本文小結

通過上述分析可以發現,若熟知基本設計規則,在系統中應用高頻率互連(例如串行RapidIO)時可避免任何與信號完整性差相關的傳統問題,例如噪音、瞬間效應、串擾或抖動等等。

電子發燒友App

電子發燒友App

評論