隨著PCB設計的復雜程度和高速PCB設計需求的不斷增加,越來越多的PCB設計者、設計團隊選擇Cadence 的設計平臺和工具。但是,由于沒有Protel數據到Cadence數據直接轉換工具,長期以來如何將現有的基于Protel平臺的設計數據轉化到 Cadence平臺上來一直是處于平臺轉化期的設計者所面臨的難題。

在長期實際的基礎上,結合現有工具的特點,提供一種將Protel原理圖、PCB轉化到Cadence平臺上的方法。

1. 使用的工具

a) Protel DXP SP4

b) Cadence Design Systems, Inc. Capture CIS

c) Cadence Design Systems, Inc. Orcad Layout

d) Cadence Design Systems, Inc. Layout2allegro

e) Cadence Design Systems, Inc. Allegro

f) Cadence Design Systems, Inc. Specctra

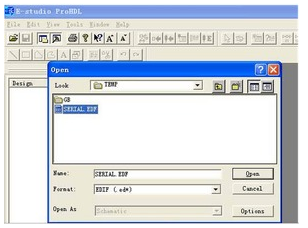

2. Protel 原理圖到Cadence Design Systems, Inc. Capture CIS

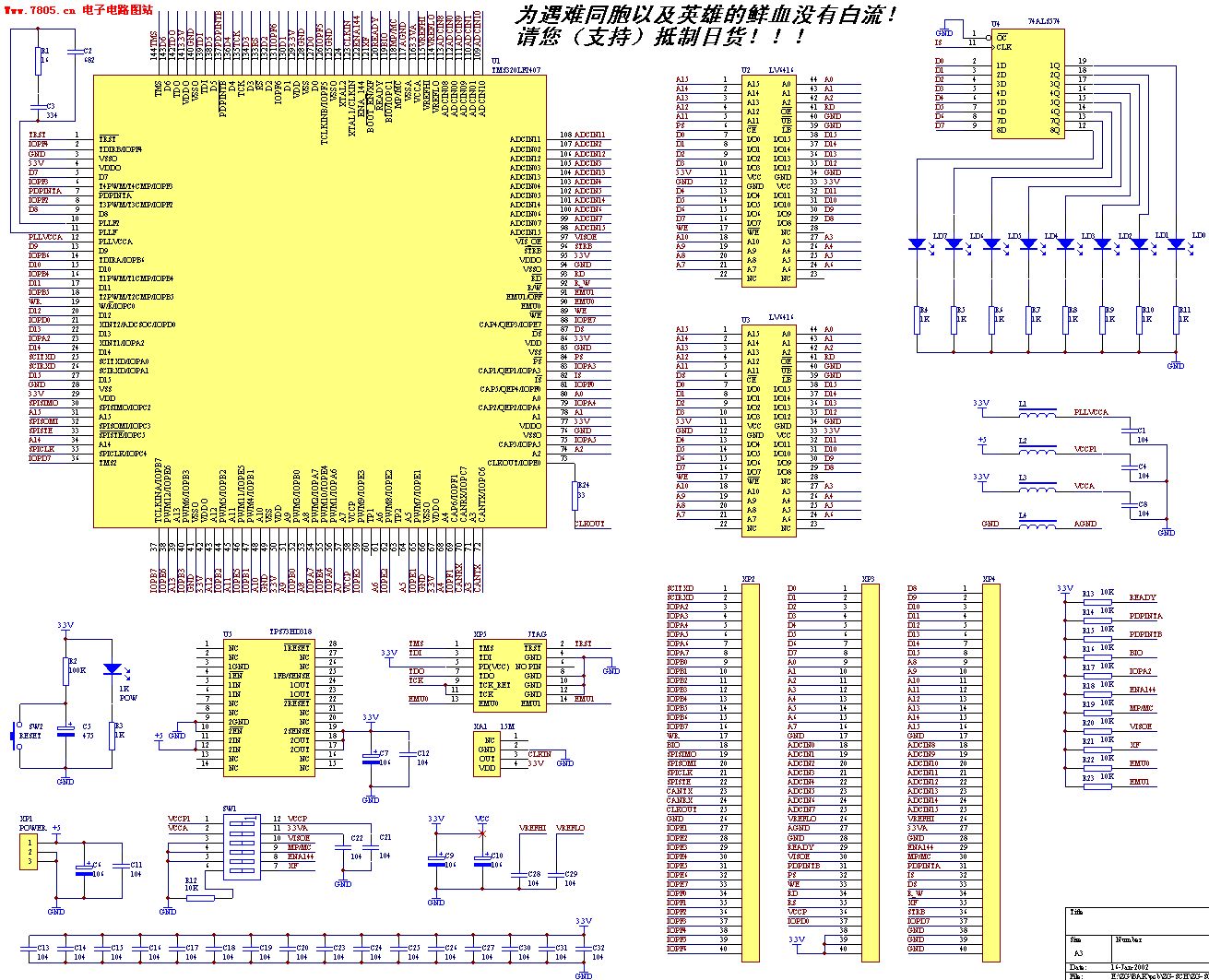

在Protel原理圖的轉化上我們可以利用Protel DXP SP2的新功能來實現。通過這一功能我們可以直接將Protel的原理圖轉化到Capture CIS中。

這里,我們僅提出幾點通過實踐總結出來的注意事項。

1) Protel DXP在輸出Capture DSN文件的時候,沒有輸出封裝信息,在Capture中我們會看到所以元件的PCB Footprint屬性都是空的。這就需要我們手工為元件添加封裝信息,這也是整個轉化過程中最耗時的工作。在添加封裝信息時要注意保持與Protel PCB設計中的封裝一致性,以及Cadence在封裝命名上的限制。例如一個電阻,在Protel中的封裝為AXIAL0.4,在后面介紹的封裝庫的轉化中,將被修改為AXIAL04,這是由于Cadence不允許封裝名中出現“。”;再比如DB9接插件的封裝在Protel中為DB9RA/F,將會被改為DB9RAF。因此我們在Capture中給元件添加封裝信息時,要考慮到這些命名的改變。

2) 一些器件的隱藏管腳或管腳號在轉化過程中會丟失,需要在Capture中使用庫編輯的方法添加上來。通常易丟失管腳號的器件時電阻電容等離散器件。

3) 在層次化設計中,模塊之間連接的總線需要在Capture中命名。即使在Protel中已經在父設計中對這樣的總線命名了,還是要在Capture中重新來過,以確保連接。

4) 對于一個封裝中有多個部分的器件,要注意修改其位號。例如一個74ls00,在protel中使用其中的兩個門,位號為U8A,U8B。這樣的信息在轉化中會丟失,需要重新添加。

基本上注意到上述幾點,借助Protel DXP,我們就可以將Protel的原理圖轉化到Capture中。進一步推廣,這也為現有的Protel原理圖符號庫轉化到Capture提供了一個途徑。

3. Protel 封裝庫的轉化

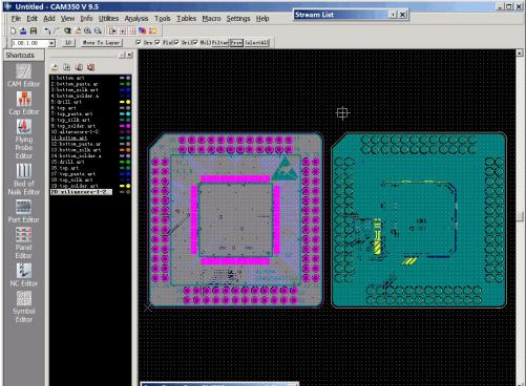

長期使用Protel作PCB設計,我們總會積累一個龐大的經過實踐檢驗的Protel封裝庫,當設計平臺轉換時,如何保留這個封裝庫總是令人頭痛。這里,我們將使用Orcad Layout,和免費的Cadence工具Layout2allegro來完成這項工作。

a) 在Protel中將PCB封裝放置到一張空的PCB中,并將這個PCB文件用Protel PCB 2.8 ASCII的格式輸出出來;

b) 使用Orcad Layout導入這個Protel PCB 2.8 ASCII文件;

c) 使用Layout2allegro將生成的Layout MAX文件轉化為Allegro的BRD文件;

d) 接下來,我們使用Allegro的Export功能將封裝庫,焊盤庫輸出出來,就完成了Protel封裝庫到Allegro轉化。

4. Protel PCB到Allegro的轉化

有了前面兩步的基礎,我們就可以進行Protel PCB到Allegro的轉化了。這個轉化過程更確切的說是一個設計重現過程,我們將在Allegro中重現Protel PCB的布局和布線。

1) 將第二步Capture生成的Allegro格式的網表傳遞到Allegro BRD中,作為我們重現工作的起點;

2) 首先,我們要重現器件布局。在Protel中輸出Place & Pick文件,這個文件中包含了完整的器件位置,旋轉角度和放置層的信息。我們通過簡單的手工修改,就可以將它轉化為Allegro的Placement 文件。在Allegro中導入這個Placement文件,我們就可以得到布局了。

3) 布線信息的恢復,要使用Specctra作為橋梁。首先,從Protel中輸出包含布線信息的Specctra DSN文件。對于這個DSN文件我們要注意以下2點:

a) Protel中的層命名與Allegro中有所區別,要注意使用文本編輯器作適當的修改,例如Protel中頂層底層分別為Toplayer和Bottomlayer,而在Allegro中這兩層曾稱為TOP和BOTTOM;

b) 注意在Specctra中查看過孔的定義,并添加到Allegro的規則中。

在allegro中定義過孔

從Specctra中輸出布線信息,可以使用session, wires, 和route文件,建議使用route文件,然后將布線信息導入到我們以及重現布局的Allegro PCB中,就完成了我們從Protel PCB到Allegro BRD的轉化工作。

責任編輯;zl

電子發燒友App

電子發燒友App

評論