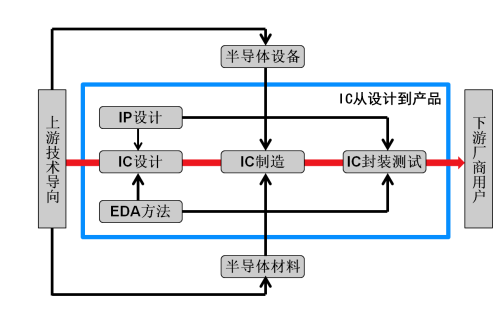

在當今技術突飛猛進的年代,人們對半導體與集成電路產業分工、歷史進程以及未來發展的關注越來越多,對美歐、日韓等國和中國臺灣地區在集成電路的技術發展和貢獻,對集成電路產業鏈中的設計、制造、封測、設備和材料的分類及其相互關系(見圖1)有了較好認識。

?

圖1 半導體與集成電路產業的相互關系示意圖

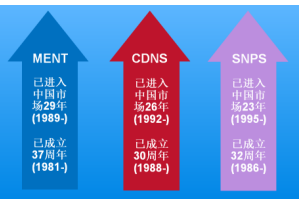

集成電路設計離不開電子設計自動化(Electronic Design Automation, EDA)技術。最早的EDA 公司Calma于1965年出現,隨后EDA相關公司此起彼落,其間經過若干次并購與重組,于90年代成立,至今形成了三家EDA主要廠商,見圖2。Mentor公司成立于1981年,最早于1989年進入中國市場。ECAD公司成立于1982年、SDA公司成立于1983年,其后兩家公司合并于1988年,成立了Cadence公司,于1992年進入中國市場。Synopsys公司成立于1986年,于1995年進入中國市場。

?

圖2 國際三大EDA廠商成立時間與進入中國市場時間

在集成電路設計與制造的同一時期,從20世紀70年中期開始至90年代,從EDA技術出現發展到多家EDA公司,芯片設計自動化方法以“點工具(point tools)”為主,逐漸有了EDA設計流程,EDA公司成為集成電路產業的重要成員。以1995年發布的Pentium Pro CPU為例,這個階段的集成電路設計大約有1.2~2.5萬個的邏輯門(5~10萬個晶體管),同期的EDA方法也比較簡單,大致有:前端設計,包括系統設計與RTL編碼、驗證;后端設計,包括布局、布線、標準單元庫版圖設計;物理驗證,包括設計規則檢查(Design Rules Check, DRC)、版圖與電路檢查 (Layot versus Schematic, LVS)等;封裝與PCB設計例如BGA等。

集成電路產業鏈的上游通常以芯片設計和IP設計為主。大約在1995~2005年期間,規模較大的歐美日集成電路公司通常屬于整機器件制造商(Integrated Device Manufacturer, IDM),以產品市場為目標,除了自己設計與制造之外,還建立了各自的CAD部門,并擁有自家的一整套設計流程。例如Intel, AMD, NEC, Toshiba, National, Fujitsu, ST等。隨著系統芯片(System-on-Chip, SoC)年代的到來,芯片中集成更多存貯器、IP和COT(Custom-Owned Tooling)模塊時,設計變得更為復雜,時序常常不能收斂。這時,IDM公司和更多新成立的無芯片制造廠商(Fabless)設計公司加入到集成電路行業大軍,人們需要更加完整的EDA方案。

2.集成電路技術進步與EDA技術平臺

從1958年Jack Kilby發明集成電路(Integrated Circuit, IC)技術、Intel 1970年發布第一款10um工藝1-kbit存貯器(DRAM IC 1003)、1971年發布第一款4-bit CPU 4004 (10um pMOS工藝)以來,存儲器與CPU設計發展已經經歷了60年的漫長歷史。以Intel為例,2010年以來,是沿180nm, 130nm, 90nm, 65nm, 45nm, 32nm, 22nm, 14nm, 10nm工藝路線發展的,見圖3。以TSMC為例,該公司成立于1987年,其工藝路線從3μm工藝開始,本世紀初左右芯片制造工藝進入180nm,2006年前后進入65nm工藝,2012年進入28nm工藝,2018年10nm芯片開始量產,見圖3。需要注意的是,近來人們對單位面積上集成的晶體管數進行計算和比較,發現Intel公司的10nm集成度相當于TSMC和三星公司的7nm的集成度。

?

圖3 Intel和TSMC的集成電路工藝節點發展示意圖

在集成電路設計發展的50年過程中,集成電路主角CPU和存貯器產品的設計水平彰顯了技術進步,而工藝生產中光刻技術則反映了芯片的制造能力。其中,集成電路產業鏈中的EDA技術與方法極為重要,它常常推動集成電路設計與制造,通過先進的設計方法,與設計技術和工藝制造緊密配合,有時甚至還會走在IC設計公司的前面,在技術和方法上是一位創新能手和技術先鋒。如今,EDA的作用與地位越來越得到產業界的肯定。近年來,芯片設計的性能、功耗和面積 (Performance, Power, Area, PPA) 參數不斷得到優化和提升。新的三維存貯器技術更加成熟,例如,三維與非閃存(3D NAND Flash)技術中的64/72層 3D NAND Flash的量產。芯片制造工藝中光刻技術不斷進步與發展,例如,使用i193納米的浸入式光刻技術將工藝節點延展到20nm, 極紫外(Extreme UV, EUV)光刻技術將進入5nm工藝以下的實用階段。還有,各種新工藝方法的建立與創新,例如,兩次或多次曝光技術(Double Pattern Technology, DPT, 或Multiple Pattern Technology, MPT)等通過光刻與刻蝕交替(Litho-Eching,LELELE)的方法將20納米延展到10nm以下;先進封裝技術的成功,例如,將3D IC/TSV(Through-Silicon Via)與2.5D IC相結合的SiP封裝,用于高帶寬存貯器(High-Bandwidth Memory,HBM)等,處處離不開EDA技術和方法。

這一時期的EDA廠商對芯片設計方法和芯片設計創新技術有了更多的研發投入。尤其是針對完整設計流程,建立了更為科學的方法。包括系統架構設計、IP設計及其協議(protocol)、芯片代碼設計與驗證、極為復雜的數字電路的設計與集成、混合信號與射頻電路的設計與仿真。從系統芯片集成到封裝測試的完整技術方法和設計流程,EDA技術在產業鏈中與設計公司的技術并駕齊驅,建立了很多新方法。比如在80年代RTL綜合方法;90年代時序驅動設計(Timing-Driven Design, TDD)和形式驗證(Formal Verification, Logic Equivalence Checking, LEC)方法;20世紀末層次化(hierarchical)設計方法;21世紀初硬件加速仿真(hardware emulation)方法和高級綜合 (High-Level Synthesis, HLS) 方法等。

以2005年發布的Itanium CPU為例,這個階段的集成電路設計含有1億個(1x108)邏輯門,或者說4億個(4x108)晶體管。再以2015年IBM的z13存貯控制器芯片設計為例,這個階段的集成電路設計含有15億個(1.5x109)邏輯門, 或者說60億個 (6x109) 晶體管。這一時期的EDA方法開始從設計流程發展為設計平臺,見圖4。大致為:系統設計與驗證平臺(圖4中橙色),包括系統設計、RTL編碼與驗證,硬件仿真(Emulation);數字集成電路設計與實現平臺(圖4中梅紅色),包括時序約束驅動設計(Timing-Driven Design)、綜合布局布線(Synthesis Place & Route)、時鐘樹綜合(Clock-Tree Synthesis)、低功耗設計等;定制集成電路設計平臺(圖4中淺綠色),包括標準單元庫、模擬和射頻電路的版圖設計;標準單元時序庫產生、工藝設計包或錦囊(Process Design Kit, PDK)和物理驗證等;封裝和PCB設計平臺(圖4中深藍色),包括倒裝芯片(Flip-Chip)封裝和系統封裝(System in Package, SiP)技術與PCB設計等。圖4中每一個平臺都包含了多個設計流程(圖中未展示),其中,數字電路設計平臺涉及面最廣、實現起來最為復雜。

?

圖4 EDA設計平臺示意圖

3.集成電路設計與EDA的年會DAC

五十多年來全球EDA的產業發展,EDA與IC設計公司的技術交流,設計方法與設計流程的開發與改進,EDA產品的展覽與發布,往往是通過“設計自動化大會”(Design Automation Conference, DAC)來進行的。DAC第一次于1964年舉行,以EDA技術和展覽為主題,截至2018年6月,從來不間斷地舉行了55次會議。DAC 2018主題演講(Keynote Speech)以物聯網(IoT)和機器學習話題開場。

DAC近幾年的議題主要包括:1)電子系統和電子設計自動化;2)電路與系統的EDA設計方法;3)嵌入式軟件與系統協同設計,如何滿足速度、效率、可靠性、保密性與安全等;4)用于汽車電子系統的物聯網設計及其對EDA方法和工具的總體要求,從而實現降低功耗、完全性、易于組裝等;5)IP的開發、驗證、集成和管理;6)近年來新添加的人工智能中機器學習所涉及的算法與硬件中的設計自動化;7)電子世界的系統安全,包括軟件和硬件的組成、各種平臺和供應鏈的安全,如何用于金融、健康保健、交通運輸以及能源。

DAC 2018引人注目的一個發言是美國國防先期研究計劃局(Defense Advanced Research Projects Agency, DARPA) Andreas Olofsson先生,他披露了DARPA將投入1億美元的“電子復興計劃” (Electronics Resurgence Initiative, ERI)并于7月下旬召開“電子復興計劃”專題峰會。這一計劃包括兩個EDA項目,分別為“電子設備智能設計”(Intelligent Design of Electronic Assets,IDEA)和創建稱作“高端開源硬件”(Posh Open Source Hardware,POSH)的硅模塊庫。Olofsson先生曾經先后在TI公司、ADI等公司工作20年,專門從事低功耗處理器和混合信號電路的設計與測試。

Marie Pistilli 和Pasquale (Pat) Pistilli 最早并一直組織DAC會議。 其中,Pat因此于2010年獲得了EDA產業的最高榮譽獎:Phil Kaufman 獎。為了表彰Marie,人們于2016年設立了以她名字命名的“Marie R. Pistilli婦女工程成就獎”。與DAC相關的另外兩個會議也很重要,即“亞洲與南太平洋設計自動化會議“(Asia and South Pacific Design Automation Conference, ASP-DAC,始于1995年) 、在法國和德國交替舉行的“歐洲設計自動化與測試會議”(Design Automation and Test in Europe, DATE,始于1998年)。回顧歷屆會議,2005年DAC會議最大規模時曾經吸引了5500人參加;而同期與DAC緊密相關以純技術為主不含商業展覽的“國際計算機輔助設計大會”(International Conference on Computer-Aided Design, ICCAD)參會人數僅僅為其十分之一。

國際會議ICCAD始于1981年,屬于沒有商業展覽的純技術會議,今年11月將舉行第37屆年會。我國半導體行業協會集成電路設計年會(China Semiconductor Industry Association – Integrated Circuit Computer-Aided Design, CSIA-ICCAD) 始于1994年,至2017年也連續舉行了23次會議,去年參會者達到1000多人,三家EDA廠商是CSIA-ICCAD會議的積極參與者,也同時贊助國際工程師設計會議(DesignCon,第23屆年會將于今年7月舉行)和國際設計與驗證會議(DVCon)等。

4.Phil Kaufman 獎 --“EDA產業的諾貝爾獎”

Phil Kaufman Award 開始于1994年,又稱為EDA產業的諾貝爾獎(“The Nobel Prize of the EDA Industry”), 該獎項由 ESD-Alliance 和 “IEEE Council on EDA”共同贊助,授予對電子系統作出杰出貢獻的設計師或工程師,并每年在硅谷舉行晚宴招待會。Phil Kaufman在1988年擔任Quickturn設計系統公司CEO,他本人的最大貢獻是開發了硬件仿真(hardware emulation)的驗證手段與設備。自1994年首屆頒獎以來,該項活動從未間斷,僅僅2012年因與DAC 的50周年慶祝時間上沖突,從而與2013年合并,截至2017年,共向23位個人頒發了23次獎項

?

表1 Phil Kaufman獎(也稱為“EDA產業的諾貝爾獎”)得主及其關鍵貢獻

細心的讀者從表1不難看出,獲獎者的技術貢獻都與EDA方法的各項技術或者活動有關,從系統算法和硬件語言,到電路設計與仿真等,都已經集成于EDA平臺的各種技術中。得獎人員除了三大EDA公司的著名首領之外,其余的學術人員則以加州大學伯克利校區(University of California, Berkeley, UCB)的博士和專家居多。這也是為什么人們常說,“圣荷西(San Jose)是美國的硅谷,加州大學伯克利校區是EDA的發源地”。

5.集成電路設計與EDA產業的未來

縱觀集成電路產業的發展過程,產業鏈(圖1)中的各個部分在不同時期都會遇到困難。目前,用于人工智能的機器學習芯片廣受關注和考驗。人們不僅要考核這類芯片是否具有低功耗和高新能的特點,還要對其算力(即每瓦的性能,例如,MOPS/mW)進行評估。有實驗顯示,Nvidia公司的GPU算力是CPU的3倍,谷歌的TPU算力是CPU的83倍。由于這些處理器和FPGA技術在機器學習流行之前就已經存在,因此,現有的各類CPU、GPU以及TPU的處理器架構都不是最優化的、算力最佳的設計。

2017年圖靈獎獲得者加州大學的David Patterson和斯坦福大學的John Hennessy 在最近的幾個重大會議、包括在DAC 2018的演講中指出,CPU的架構設計歷史已經經歷了半個世紀,以CISC與RISC為主發展至今,到了后PC時代,RISC成為主流并擁有99%的市場,而未來新一代架構的發展需求充滿了黃金機遇。他們提出了未來系統架構的新方向為區域特定架構(Domain-Specific Architectures, DSAs),并建議采用區域特定語言(Domain-Specific Languages, DSLs)作為軟件和硬件協同開發的方案。

由于IBM當年需要采購大量基于x86的CPU產品, 2001年Intel將x86授權于AMD公司共同開發生產,從而推動了CPU的產品市場。NVIDIA和AMD公司等開發出GPU,和以CPU和GPU為主的異構系統架構(Heterogeneous System Architecture, HSA),對今天的以人工智能芯片的架構設計是有了很大的啟示。2018年以后將進入7nm~1nm的工藝時代,人工智能中機器學習的發展及其對芯片技術的需求,對系統芯片的架構發展帶來了新機會,也給未來應用帶來了美好的期望。當前AI芯片技術包括了智能語音、智能家居、智慧安防、智能車載等。在汽車電子和汽車無人駕駛等高可靠性需求的領域,在集成電路設計技術急劇發展的年代,EDA公司的產品和平臺設計方案又增添了什么?西門子旗下的Mentor公司突出提出了板級和芯片設計方案,包括從系統設計到汽車電子的EDA設計技術;Cadence公司強調集成電路的集成與驗證技術,從芯片封裝、板級到系統的驗證方法;Synopsys公司提出了以關注軟件的安全和質量、多種IP設計文案(portfolio)和方案,解決未來硬件設計師和軟件設計師的技術需求。

人們曾經多次推測EDA公司技術發展似乎走到了盡頭,遭遇了極大的瓶頸。然而近幾年,根據筆者的個人觀察,結合芯片制造和CPU架構設計發展趨勢,EDA公司除了緊密跟隨集成電路產業發展需求,同時也在以下幾個方面走在了產業的前面,在IP設計中的開發、驗證與集成;在汽車電子中的先進駕駛輔助系統(Advanced Driver-Assistance Systems, ADAS)方面的可靠性的技術開發;人工智能芯片技術的開發與支持(軟硬件的協同設計、軟硬件的架構設計)。目前SoC的UVM驗證方法得到更多重視和應用;由于有更多混合信號設計加入,先進的混合信號驗證方法將會得到重視和應用。在航空航天設計方面,芯片的可靠性設計方法在美國得到系統的研究,由于其機密性,公開報道很少。人們發現,從SoC設計到SiP封裝,技術變得越來越復雜,成本也變得越來越高。DARPA在DAC 2018的發言,將引領并開發電子復興計劃ERI,間接地說明了未來的先進低功耗處理器和混合信號電路的設計與測試以及保障質量的重要性。根據相關資料,DARPA的ERI所列出的“電子設備智能設計”和“高端開源硬件”兩個EDA項目將和美國17個州的22個小組合作,包括70多名專業人員和100名研究生參與。其中,學院的研究投入占57%,工業界投入占43%。

當前,人工智能通過機器學習,大數據經過云計算技術發展,使得人們將軟件和硬件設計結合起來。面對基于RISC架構的設計不能應對復雜的計算時,David Patterson和John Hennessy建議將軟件和硬件設計結合起來。當人們對集成電路的設計和封裝技術的復雜度和高成本不能容忍時,DARPA提出了將系統軟件設計和EDA硬件設計結合起來。早在十年前,系統設計公司和EDA設計公司也提出了軟件與硬件協同設計的方案。今天,軟件設計與硬件設計結合的時代真的到來了!

參考文獻:

[1]EDA, https://en.wikipedia.org/wiki/Electronic_design_automation

[2]DAC, https://dac.com/

[3]Phil Kaufman Award for Distinguished Contributions to EDA. http://ieee-ceda.org/awards/phil-kaufman-award-distinguished-contributions-eda

[4]陳春章,何樂年,李志群,艾霞 等譯,《數字模擬混合信號集成電路設計方法學指導》, 北京:科學出版社,2015 (ISBN 978-7-03-041959-0)。

[5]Hu, D.Y. and Chen, C.-Z., 2014, (Invited) Reliability Aspects of Advanced IC Technologies with ESD & Anti-radiation Capabilities, ECS Transactions, 60(1) 1185-90, 2014. (Pres. on March 17, CSTIC 2014, Shanghai.)

[6]Chen, C.-Z. and Hu, D.Y., 2017, Geometry Effect with Respect to ESD and Radiative Charged Particles in SoC. China Semicon. Tech. Int. Conf. (CSTIC, March 12-13, 2017, Shanghai.) IEEE Conf. Pub., http://ieeexplore.ieee.org/document/7919894/

本文作者陳春章博士是集成電路芯片設計與電子設計自動化(EDA)專家,英國 St Andrews 大學輻射物理學博士。出版專著:《混合信號設計方法學指導》(中文翻譯,科學出版社,2015年);《數字集成電路物理設計》(科學出版社,2008年);英文集成電路設計文章10多篇,英文輻射物理科學研究專業文章文摘30多篇。

電子發燒友App

電子發燒友App

評論