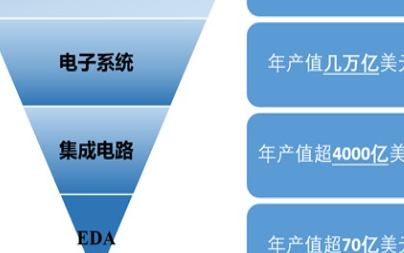

在全球半導(dǎo)體價(jià)值鏈上,EDA和IP可能只占1/30的營收份額,但對整個(gè)半導(dǎo)體行業(yè)的無形價(jià)值卻是無法估量的,從Arm和Synopsys在半導(dǎo)體行業(yè)的舉足輕重地位即可看出。EDA和IP的前沿技術(shù)研究和創(chuàng)新對半導(dǎo)體的長期增長有著巨大的影響力,我們在此總結(jié)出當(dāng)前EDA和IP市場出現(xiàn)的三大技術(shù)趨勢。

01?趨勢一:EDA Cloud和AI

相對于維護(hù)企業(yè)自己的服務(wù)器和數(shù)據(jù)中心,云計(jì)算服務(wù)具有固定投入低、可擴(kuò)展、彈性計(jì)算使用和無限制存儲容量等優(yōu)勢。然而,EDA行業(yè)在上云方面是相對落后的,主要原因在于IC設(shè)計(jì)公司和晶圓代工廠商擔(dān)心云平臺有可能危及自己的IP和設(shè)計(jì)保密信息。隨著云平臺服務(wù)商針對EDA云計(jì)算的專門安全防護(hù)讓EDA供應(yīng)商和IC設(shè)計(jì)公司更為放心,以及IC設(shè)計(jì)和驗(yàn)證的復(fù)雜度不斷提升,迫使EDA行業(yè)上云步驟加速。

此外,針對特定應(yīng)用場景(design-for-context)的IC設(shè)計(jì)和系統(tǒng)設(shè)計(jì)逐漸成為主流,這要求EDA工具更緊密地與IC設(shè)計(jì)廠商協(xié)作,唯有通過云端部署的高性能計(jì)算才能支持這種設(shè)計(jì)合作。

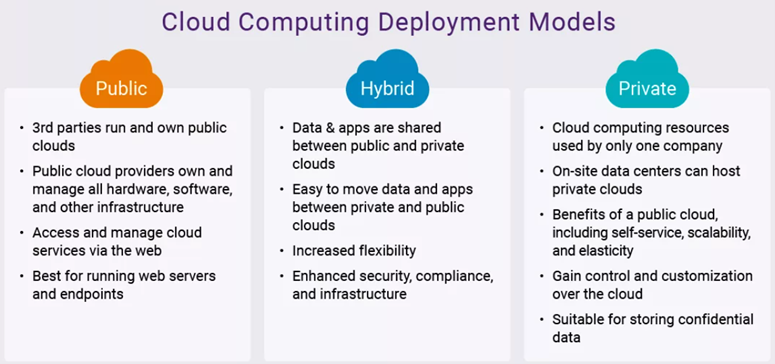

在云端部署云原生EDA工具和預(yù)先針對IC設(shè)計(jì)而優(yōu)化的硬件平臺,以及靈活的EDA使用授權(quán)模式,讓云端EDA成為很有吸引力的選擇。云計(jì)算部署模式有三種形式:公有云、私有云和混合云,各自的特點(diǎn)如下圖所示。

云服務(wù)的三種常見應(yīng)用方式包括:

基礎(chǔ)設(shè)施服務(wù)(IaaS):云平臺服務(wù)商提供和維護(hù)數(shù)據(jù)中心服務(wù)器等IT基礎(chǔ)設(shè)施,并作為一種服務(wù)提供給各種客戶使用;

平臺服務(wù)(PaaS):云平臺服務(wù)商提供一個(gè)計(jì)算平臺,讓用戶開發(fā)、運(yùn)行和管理自己的應(yīng)用,而不必自己部署和維護(hù)復(fù)雜的服務(wù)器網(wǎng)絡(luò);

軟件服務(wù)(SaaS):在云平臺上提供按需使用的軟件授權(quán)和交付模式,用戶不必安裝自己的硬件即可使用相應(yīng)的軟件,按使用量付費(fèi)即可。

云端EDA對IC設(shè)計(jì)和驗(yàn)證帶來的具體好處如下:

可伸縮性強(qiáng):云端EDA系統(tǒng)可以根據(jù)需求即時(shí)擴(kuò)容,比如驗(yàn)證需要算力峰值時(shí);

網(wǎng)絡(luò)分割:大型IC設(shè)計(jì)公司的設(shè)計(jì)中心往往部署在全球多個(gè)地方,法律或合同條款可能要求特定IP限定在指定地域內(nèi)。云端網(wǎng)絡(luò)可以按照規(guī)則劃分以避免潛在的合規(guī)風(fēng)險(xiǎn);

冗余備份:云平臺服務(wù)商的冗余服務(wù)器部署在全球多個(gè)數(shù)據(jù)中心,一個(gè)地方發(fā)生的系統(tǒng)災(zāi)難不會導(dǎo)致IC設(shè)計(jì)數(shù)據(jù)丟失;

避免單點(diǎn)故障:傳統(tǒng)EDA系統(tǒng)網(wǎng)絡(luò)一般有多個(gè)故障點(diǎn),通過一個(gè)節(jié)點(diǎn)進(jìn)行控制管理。如果這個(gè)節(jié)點(diǎn)出現(xiàn)故障,整個(gè)EDA系統(tǒng)網(wǎng)絡(luò)就會癱瘓,EDA授權(quán)、配置和版本管理服務(wù)器也不能幸免。云端網(wǎng)絡(luò)基于微服務(wù)模式,不會因?yàn)閱吸c(diǎn)故障和影響整個(gè)EDA系統(tǒng);

投入成本低且易于使用

IC設(shè)計(jì)流程的效率更高:云計(jì)算平臺的網(wǎng)絡(luò)延遲更低,分布在多個(gè)地方的IC設(shè)計(jì)團(tuán)隊(duì)之間的項(xiàng)目協(xié)作更為流暢。

EDA三巨頭在EDA上云方面都很積極,分別與亞馬遜AWS、圍繞Azure和谷歌云服務(wù)合作,將自己的IC設(shè)計(jì)和驗(yàn)證工具搬到云端,以爭搶EDA下一波市場高地。例如,新思科技的云服務(wù)采用FlexEDA模式,可以為用戶提供不受限制、按需使用的EDA軟件授權(quán)。用戶可以選擇其SaaS模式,也可以選擇BYOC模式,讓新思幫助部署自己的云計(jì)算網(wǎng)絡(luò)。

Cadence云服務(wù)包括三個(gè)部分,分別是:

CloudBurst平臺:為用戶提供IC設(shè)計(jì)、驗(yàn)證和實(shí)施的云環(huán)境,包括授權(quán)軟件和支持、EDA優(yōu)化的云計(jì)算設(shè)施、服務(wù)和支持等;

Palladium云驗(yàn)證:托管在由Cadence管理的數(shù)據(jù)中心,為用戶提供按需使用的驗(yàn)證服務(wù),讓客戶輕松增加所需的峰值容量;

Cloud Passport:將客戶私有工具連接到云端,為客戶提供自主管理的混合工具。

西門子EDA的Calibre云服務(wù)提供與傳統(tǒng)簽核驗(yàn)證一樣的性能和結(jié)果,同時(shí)讓用戶根據(jù)自己的需要調(diào)整EDA資源使用情況。其好處包括:優(yōu)化的Calibre引擎和經(jīng)過代工廠商確認(rèn)的規(guī)則檢查匯總;采用分層歸檔方式,降低數(shù)據(jù)量及縮短最終簽核運(yùn)行時(shí)間;Calibre HDB分層數(shù)據(jù)庫模式等。

國內(nèi)云端EDA服務(wù)商也開始活躍起來,值得關(guān)注的兩家公司包括:

楷領(lǐng)凌云電子設(shè)計(jì)云平臺:為用戶提供一站式開箱即用的云上IC設(shè)計(jì)環(huán)境,包含完整的EDA和云IT資源,其中EDA工具由美國EDA全方案和國產(chǎn)EDA產(chǎn)品組合而成,可彈性授權(quán)使用主流EDA工具,以及專業(yè)的自動化與定制化芯片設(shè)計(jì)流程服務(wù)。該平臺可適用于各種規(guī)模的數(shù)字SoC、模擬芯片或數(shù)模混合IC產(chǎn)品設(shè)計(jì),如電源管理芯片、驅(qū)動芯片、CPU/DSP/GPU等各類計(jì)算型芯片、4G/5G基帶芯片、光通訊芯片、無線藍(lán)牙等射頻芯片、汽車電子控制和娛樂類芯片、MCU和工業(yè)控制芯片、加密解密等安全類芯片等。

英諾達(dá):提供基于EDA硬件仿真加速器的云平臺,底層采用Cadence的Palladium(帕拉丁)系統(tǒng),致力于解決復(fù)雜芯片的驗(yàn)證資源問題,縮短芯片開發(fā)周期。通過向廠商提供安全的EDA驗(yàn)證硬件云入口,客戶可以按需使用,既可以滿足峰值需求,也可以實(shí)現(xiàn)設(shè)計(jì)全過程的驗(yàn)證需求。

在利用AI/ML進(jìn)行IC設(shè)計(jì)的技術(shù)創(chuàng)新方面,新思科技和Cadence走在前列。新思科技發(fā)布的DSO.ai(Design Space Optimization AI)軟件,可以讓IC設(shè)計(jì)工程師更自主地確定在芯片上排列布局的最佳方式以減少面積和降低功耗,由此開始了EDA設(shè)計(jì)的AI化進(jìn)程。利用強(qiáng)化學(xué)習(xí)(reinforcement learning),DSO.ai 可以根據(jù)設(shè)計(jì)目標(biāo)來評估數(shù)十億個(gè)替代方案,并快速產(chǎn)生優(yōu)于優(yōu)秀工程師的設(shè)計(jì)方案。DSO.ai能夠解決的問題/方案包括:在芯片上排放各種組件的可能方案數(shù)量大約有10的9萬次方個(gè)(1090,000)。相比之下,谷歌AI在2016 年掌握的圍棋走法只有10的360次方個(gè)(10360 )。據(jù)稱DSO.ai的早期試驗(yàn)結(jié)果令人印象深刻,實(shí)現(xiàn)了18% 的工作頻率提高,而且功耗降低了 21%,同時(shí)將工程時(shí)間從六個(gè)月縮短到一個(gè)月。

Cadence推出的智能芯片探索器Cerebrus可通過強(qiáng)化學(xué)習(xí)來優(yōu)化物理設(shè)計(jì)流程,它在功能上與新思的DSO.ai 類似,專注于物理設(shè)計(jì)。Cadence Cerebrus的發(fā)布似乎進(jìn)一步驗(yàn)證了強(qiáng)化學(xué)習(xí)技術(shù)作為芯片設(shè)計(jì)方法論的下一個(gè)重大轉(zhuǎn)變。隨著設(shè)計(jì)師越來越習(xí)慣讓機(jī)器決定布局,以及競爭壓力的增加,AI將逐漸滲透到IC設(shè)計(jì)流程的各個(gè)部分。

Cerebrus建立在大規(guī)模計(jì)算和機(jī)器學(xué)習(xí)架構(gòu)之上,并充分利用了完整的 Cadence數(shù)字全流程解決方案。Cerebrus借助獨(dú)特的強(qiáng)化機(jī)器學(xué)習(xí)引擎來提供更好的設(shè)計(jì) PPA 結(jié)果(性能、功耗和面積)。通過使用完全自動化、機(jī)器學(xué)習(xí)驅(qū)動的 RTL-to-GDS 全流程優(yōu)化技術(shù),Cerebrus 可以比手動調(diào)整的流程更快地交付這些更好的 PPA 結(jié)果,從而極大提高工程設(shè)計(jì)團(tuán)隊(duì)的生產(chǎn)力。

02?趨勢二:Chiplet互聯(lián)與高速接口IP

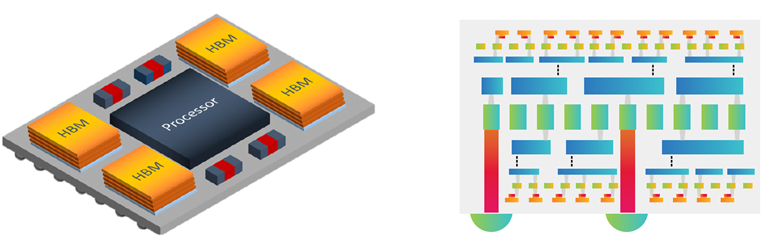

基于Chiplet架構(gòu),芯片設(shè)計(jì)師可將不同功能和工藝節(jié)點(diǎn)的芯片通過2D或2.5D/3D的封裝方式,異構(gòu)集成在一起。此外,Chiplet架構(gòu)還可以將數(shù)字、模擬或高頻工藝的不同裸片集成到一起,甚至在設(shè)計(jì)中加入高度密集的3D內(nèi)存陣列,比如高帶寬內(nèi)存(HBM)。這樣,IC設(shè)計(jì)公司就可以將來自不同IP供應(yīng)商的Chiplet像搭建LEGO積木一樣,拼裝出不同的芯片產(chǎn)品,從而以較低的成本開發(fā)出更強(qiáng)大的芯片。

Chiplet架構(gòu)和理念對IP開發(fā)商也很有吸引力,因?yàn)樗麄兛梢愿鶕?jù)自己的專長開發(fā)具有特定功能的標(biāo)準(zhǔn)化Chiplet,就像現(xiàn)在的IP一樣授權(quán)給多家IC設(shè)計(jì)公司,從而最大化其專利技術(shù)的價(jià)值。據(jù)Omdia預(yù)計(jì),Chiplet市場規(guī)模今年將達(dá)到40億美元,而到2030年有可能增至1000億美元。

問題是,這些Chiplet之間及其它類型的裸片之間如何實(shí)現(xiàn)高速數(shù)據(jù)傳輸?如果沒有業(yè)界統(tǒng)一的通用互聯(lián)標(biāo)準(zhǔn),Chiplet積木只是夢想罷了。

在眾多Chiplet互聯(lián)標(biāo)準(zhǔn)中,由Intel提出的通用Chiplet互聯(lián)標(biāo)準(zhǔn)(UCIe)在很短時(shí)間內(nèi)就引起了業(yè)界廣泛關(guān)注,目前來看最有希望成為業(yè)界統(tǒng)一的互聯(lián)標(biāo)準(zhǔn)。UCIe是唯一具有完整裸片間接口堆棧的標(biāo)準(zhǔn),其他標(biāo)準(zhǔn)都沒有為協(xié)議棧提供完整裸片間接口的全面規(guī)范,大多僅關(guān)注在特定層。此外,UCIe不但支持有機(jī)襯底或?qū)訅喊宓葌鹘y(tǒng)封裝,也可以支持2.5D和橋接等先進(jìn)封裝,如硅襯底、硅橋或再分配層(RDL)扇出等形式,預(yù)計(jì)未來還會支持3D封裝。

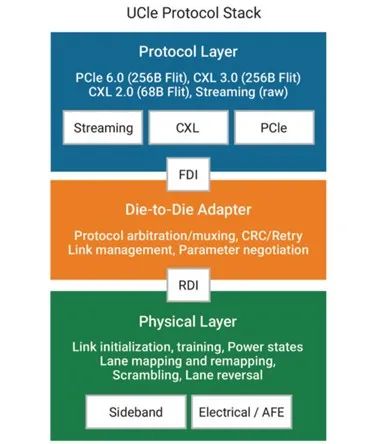

UCIe協(xié)議棧本身有三層:

最上端的協(xié)議層通過基于流量控制單元(FLIT)的協(xié)議實(shí)現(xiàn),確保最大效率和最低延遲,并支持多個(gè)主流協(xié)議,包括PCIe、Compute Express Link(CXL),以及用戶定義的流協(xié)議。

中間的D2D適配層用于對協(xié)議進(jìn)行仲裁與協(xié)商,以及通過裸片間適配器進(jìn)行連接管理。基于循環(huán)冗余檢查(CRC)和重試機(jī)制,該層還包括可選的錯(cuò)誤糾正功能。

最下面的物理層(PHY)規(guī)定了與封裝介質(zhì)的電氣接口,是電氣/模擬前端(AFE)、發(fā)射器/接收器以及邊帶通道(Sideband)在兩個(gè)裸片之間進(jìn)行參數(shù)交換與協(xié)商的層級。邏輯PHY可實(shí)現(xiàn)連接初始化、訓(xùn)練和校準(zhǔn)算法,以及測試和修復(fù)功能。

UCIe協(xié)議棧示意圖

UCIe協(xié)議具有如下優(yōu)點(diǎn):

UCIe的Sideband、DDR、Forward Clock設(shè)計(jì)使得UCIe單個(gè)應(yīng)用場景下的模塊設(shè)計(jì)復(fù)雜度相對更低,模塊驗(yàn)證也更加容易;

UCIe傳輸時(shí)延和功耗更低、速率更高、BER更低,在功耗和性能的平衡方面做得比其他協(xié)議好;

由于和PCIe/CXL的無縫對接,可以利用PCIe現(xiàn)有的強(qiáng)大生態(tài),輕松地將板級互聯(lián)擴(kuò)展到封裝內(nèi)部;

UCIe不但支持PCIe向CXL的擴(kuò)展,還支持用戶自定義的Raw mode,一個(gè)D2D Adaptor 可持架接多個(gè)協(xié)議棧。

目前已經(jīng)有不少國內(nèi)廠商加入U(xiǎn)CIe聯(lián)盟,其中包括:阿里云、日月光、長電、華為、芯原、燦芯、芯耀輝、超摩科技、合見工軟、芯和半導(dǎo)體、長鑫、牛芯、芯云凌、芯瑞微、芯來科技和奎芯等。

此外,由中國計(jì)算機(jī)互連技術(shù)聯(lián)盟(CCITA)發(fā)起的Chiplet標(biāo)準(zhǔn)《小芯片接口總線技術(shù)要求》在中科院計(jì)算所、工信部電子四院和國內(nèi)多個(gè)芯片廠商合作推動下,也已經(jīng)發(fā)布。小芯片接口總線技術(shù)的體系架構(gòu)主要包括數(shù)據(jù)鏈路層(Data Link Layer,DLL)、物理適配層(Physical Adaptation Layer,PAL),以及物理層(Physical Layer,PHY)等。

此標(biāo)準(zhǔn)列出了并行總線等三種接口,提出了多種速率要求,總連接帶寬可以達(dá)到1.6Tbps,以靈活應(yīng)對不同的應(yīng)用場景以及不同能力的技術(shù)供應(yīng)商。通過對鏈路層、適配層、物理層的詳細(xì)定義,實(shí)現(xiàn)在小芯片之間的互連互通,并兼顧了 PCIe 等現(xiàn)有協(xié)議的支持,列出了對封裝方式的要求。小芯片設(shè)計(jì)不但可以使用國際先進(jìn)封裝方式,也可以充分利用國內(nèi)通用封裝技術(shù)。

無論IC設(shè)計(jì)公司、EDA和供應(yīng)商、晶圓制造和封裝測試廠商,紛紛擁抱Chiplet,原來采用BoW或其它互聯(lián)協(xié)議的設(shè)計(jì)也開始轉(zhuǎn)向UCIe。以EDA/IP供應(yīng)商為例,EDA巨頭都在積極與TSMC等晶圓代工廠商和封裝廠商合作開展Chiplet相關(guān)技術(shù)開發(fā);Synopsys和Cadence等接口IP供應(yīng)商也都將Chiplet作為實(shí)現(xiàn)業(yè)務(wù)快速增長的契機(jī)。

Chiplet作為一種新型IP形式,必將推動一波新的IP開發(fā)熱潮,造就一批IP新銳公司。其中有三家IP公司值得關(guān)注,分別是Eliyan、Alphawave和奎芯科技,詳情參見文章:Chiplet(芯粒)互聯(lián):從一團(tuán)亂麻(BoW)到統(tǒng)一互聯(lián)標(biāo)準(zhǔn)(UCIe)。

03?趨勢三:2.5D/3D-IC設(shè)計(jì)

過去50年來,封裝技術(shù)雖然沒有像IC設(shè)計(jì)和晶圓制造發(fā)展得那么快,但也經(jīng)歷了幾次重大的技術(shù)飛躍,比如70年代出現(xiàn)的多芯片模組(MCM)封裝;2000年出現(xiàn)的系統(tǒng)級封裝(SiP);2010年出現(xiàn)的硅Interposer(即2.5D封裝);以及2020年出現(xiàn)的3D-IC先進(jìn)封裝。系統(tǒng)級芯片(SoC)的設(shè)計(jì)成本高昂、晶圓工藝接近物理極限,以及市場對性能/功耗/面積(PPA)的嚴(yán)格要求迫使半導(dǎo)體行業(yè)尋求新的技術(shù)突破,其中融合Chiplet、異構(gòu)集成和先進(jìn)封裝的技術(shù)方向似乎帶來了超越摩爾定律的希望,同時(shí)也為封裝測試(OSAT)廠商在整個(gè)半導(dǎo)體產(chǎn)業(yè)鏈上創(chuàng)造了提升價(jià)值的機(jī)會。

左邊的硅Interposer(即2.5D封裝)和右邊的3D集成封裝。(來源:Cadence)

相對于傳統(tǒng)單個(gè)裸片SoC設(shè)計(jì),2.5D/3D-IC具有如下優(yōu)勢:

降低芯片設(shè)計(jì)成本:高性能復(fù)雜芯片內(nèi)部的處理器和邏輯單元可以采用先進(jìn)的晶圓工藝,而模擬和存儲器單元?jiǎng)t可以采用相對便宜的成熟工藝,從而降低整體設(shè)計(jì)成本,并縮短開發(fā)周期;

封裝內(nèi)的裸片、chiplet和其它單元之間的互聯(lián)可以實(shí)現(xiàn)很高的數(shù)據(jù)傳輸速度和帶寬,比如對高性能的存儲器和SerDes速率可以達(dá)到200Gbps;

裸片的3D堆疊可以減少I/O驅(qū)動和互聯(lián)、降低阻-感-容(RLC)、芯片尺寸和整體功耗;

更多采用可以IP復(fù)用的chiplet,讓模擬/RF單元使用較為成熟的工藝,并可以集成光電單元和MEMS器件。

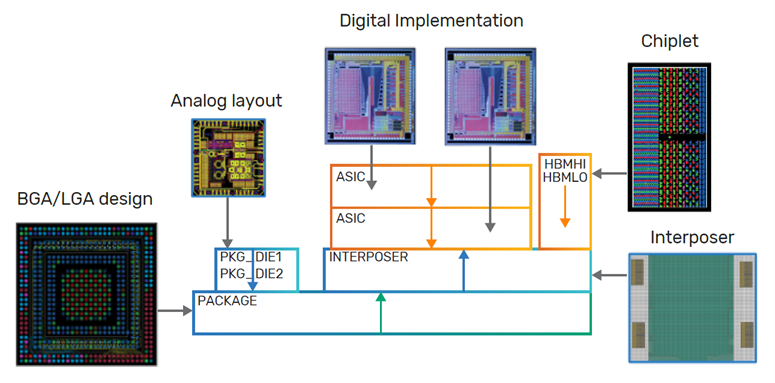

系統(tǒng)級3D設(shè)計(jì)涉及數(shù)字實(shí)現(xiàn)、模擬布局、Chiplet和Interposer的綜合規(guī)劃和優(yōu)化。(來源:Cadence)

要實(shí)現(xiàn)以上這些價(jià)值,不但需要晶圓制造廠商和封裝廠商的技術(shù)創(chuàng)新,EDA工具和設(shè)計(jì)流程也面臨極大的挑戰(zhàn)。具體表現(xiàn)在:

頂級/系統(tǒng)級異構(gòu)設(shè)計(jì)的規(guī)劃和優(yōu)化,需要從D2D到封裝甚至PCB的優(yōu)化網(wǎng)表,以及準(zhǔn)確的電磁和熱分析;

從裸片、chiplet、封裝和PCB等不同階段,都需要貫穿數(shù)字、模擬和RF域的協(xié)同設(shè)計(jì)和協(xié)調(diào)分析;

目前的EDA點(diǎn)工具都有各自的接口和模型,只能提供碎片化的2.5D/3D方案,但無法實(shí)現(xiàn)電源/信號/散熱/電磁干擾/時(shí)序等綜合性的自動化抽象、分析、驗(yàn)證和測試。

領(lǐng)先的晶圓代工廠商和封測廠商都在開發(fā)和推廣各自的2.5D/3D IC設(shè)計(jì)工藝,比如TSMC 的3DFabric(包括CoWoS和INFO);Intel的EMIB和Foveros;三星的I-Cube;日月光的FOCoS;Amkor的SWIFT;以及長電的多維扇出封裝集成(XDFOI)等。2.5D/3D IC設(shè)計(jì)要成為主流,讓Fabless、OEM廠商和互聯(lián)網(wǎng)巨頭在做復(fù)雜的芯片設(shè)計(jì)規(guī)劃時(shí)考慮采用,就需要產(chǎn)業(yè)鏈各個(gè)環(huán)節(jié)攜手打造3D-IC生態(tài),其中全流程的EDA設(shè)計(jì)工具是重要一環(huán)。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論