建立時間(setup time)和保持時間(hold time)是時序分析中最重要的概念之一,深入理解建立時間和保持時間是進行時序分析的基礎。

在介紹建立時間和保持時間之前,我們從CMOS電路開始。

1. CMOS晶體管簡介

金屬-氧化物-半導體(Metal-Oxide-Semiconductor)結構的晶體管簡稱MOS晶體管,有P型MOS管和N型MOS管之分。由MOS管構成的集成電路稱為MOS集成電路,而由PMOS管和NMOS管共同構成的互補型MOS集成電路即為 CMOS-IC( Complementary MOS Integrated Circuit)

MOS管就相當于一個開關,如下圖所示。

所以,NMOS需要輸入高電壓(邏輯1)才能導通,PMOS需要輸入低電壓(邏輯0)才能導通。可以認為NMOS是“正開關”,PMOS是“反開關”。

現在的工藝中,主要使用的就是CMOS工藝,就是把PMOS和NMOS這兩類晶體管構成一個單元,稱為CMOS單元或者反相器單元。

所以很多文章都在分析CMOS反相器,是因為CMOS反相器就是CMOS電路的基本單元,或者說可以看作最小單元。

所以從CMOS反相器開始。

1.1 CMOS 反相器

反相器就算輸入位1,輸出位0;輸入為0,輸出為1. 實際的反相器沒有這么理想。

CMOS 反相器電路如下:

當左邊vI=0V時,vGND=0V,VTN截止,∣vGSP∣=VDD ,VTP導通,vO≈VDD,門電路輸出輸出高電平;在這個過程中,從VDD到接地GND這一個供電回路都沒有導通,因此理論上不存在電流從VDD流到GND,因此功耗為0.

當左邊vI=VDD時,VGND=VDD ,VTN導通,NMOS打開,∣VGSP∣=0V,VTP截止,PMOS關閉,vO≈0V,門電路輸出低電平,但是從VDD到接地GND這一個供電回路也沒有導通,因此理論上也不存在電流從VDD流到GND,因此功耗也為0。

如果將0V定義為邏輯0,VDD定義為邏輯1,將實現邏輯“非”功能。

所以理論上,CMOS進行傳輸的時候是沒有功耗的,但是實際情況肯定不可能沒有功耗,但是功耗會很小。所以在低功耗如此重要的今天,為什么CMOS能稱為主流就不奇怪了。

2. CMOS邏輯電路

2.1 CMOS 門電路

CMOS反相器就是一個非門,由非門可以組成與非門和或非門。

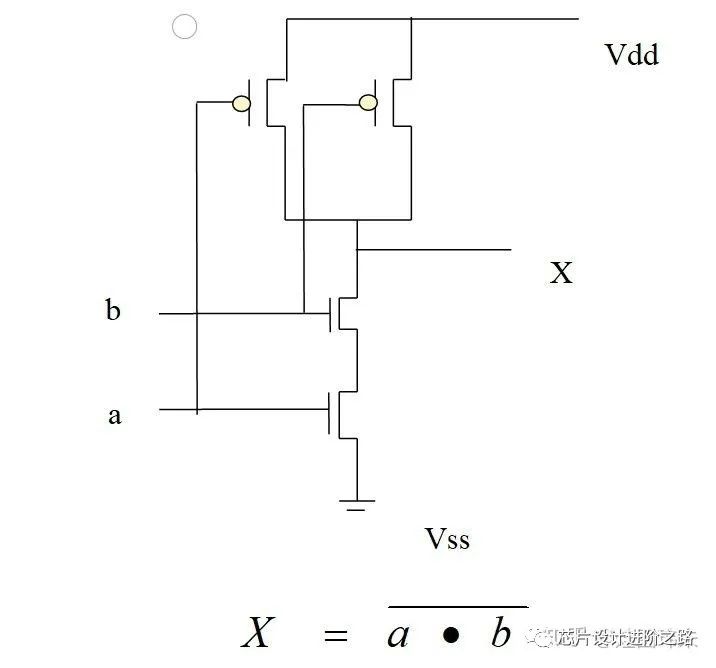

- CMOS與非門(NAND)

CMOS 與非門電路及行為如下面圖所示:

- a = 0, b=0時,上面并聯的PMOS導通,下面串聯的NMOS截止,輸出X=Vdd=1;

- a = 0, b=1時,上面并聯的PMOS導通,下面串聯的NMOS截止,輸出X=Vdd=1;

- a = 1, b=0時,上面并聯的PMOS導通,下面串聯的NMOS截止,輸出X=Vdd=1;

- a = 1, b=1時,上面并聯的PMOS截止,下面串聯的NMOS截止,輸出X=Vdd=0;

可見,這個電路實現了與非功能。

- CMOS或非門(NOR)

CMOS 或非門電路及行為如下面圖所示:

- a = 0, b=0時,上面串聯的PMOS導通,下面并聯的NMOS截止,輸出X=Vdd=1;

- a = 0, b=1時,上面串聯的PMOS截止,下面并聯的NMOS導通,輸出X=Vdd=0;

- a = 1, b=0時,上面串聯的PMOS截止,下面并聯的NMOS導通,輸出X=Vdd=0;

- a = 1, b=1時,上面串聯的PMOS截止,下面并聯的NMOS導通,輸出X=Vdd=0;

可見,這個電路實現了或非功能。

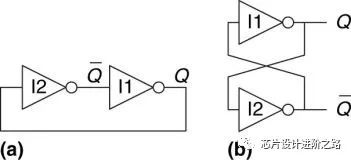

2.2 雙穩態器件

雙穩態器件是指穩定狀態有兩種,一種是0,一種是1的器件;雙穩態器件是存儲器件的基本模塊,雙穩器件的的一種電路結構是:交叉耦合反相器 結構,如下圖所示:

連個反相器連在一起,這就構成了一個雙穩態器件,為什么是雙穩態呢?我們現在就來分析一下:

由于沒有輸入,于是我們就假設I1的輸出先為1,即Q=1;那么I2的輸入為1,Q’就為0,于是反饋給Q的輸入,導致Q的輸出為1,也就是使得Q的狀態穩定為1,因此這個器件有一個穩定的狀態為1.如下圖所示:

我們再假設I1的輸出先為0,即Q=0;那么I2的輸入為0,Q’就為1,于是反饋給Q的輸入,導致Q的輸出為0,也就是使得Q的狀態穩定為0,因此這個器件還有一個穩定的狀態為0.如下圖所示:

由此可見,這種交叉耦合反相器的器件是雙穩態器件。但是需要注意的是,電路有可能存在第三種狀態,也就是前面文章介紹過的亞穩態。

為什么介紹雙穩態器件呢?那是因為鎖存器、寄存器都是雙穩態器件,它們都有兩個穩定狀態1和0。正是因為它們有兩個穩定的狀態,因此才可以拿它們來存儲數據,也就是說雙穩態電路(比如交叉耦合反相器、鎖存器和寄存器)可以存儲數據。

下面我們來看一下鎖存器和觸發器。

2.3 鎖存器(latch)

很顯然,上面的那種交叉耦合反相器沒有輸入,是存儲不了輸入的數據的了,因此就需要有輸入的類似“交叉耦合反相器”結構的雙穩態電路,這就是鎖存器。

鎖存器:不需要觸發信號,由輸入信號直接完成置0或置1操作。

最常見最基本的鎖存器是SR鎖存器,常用的鎖存器是D鎖存器。這里只介紹RS觸發器和D觸發器。

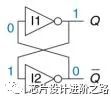

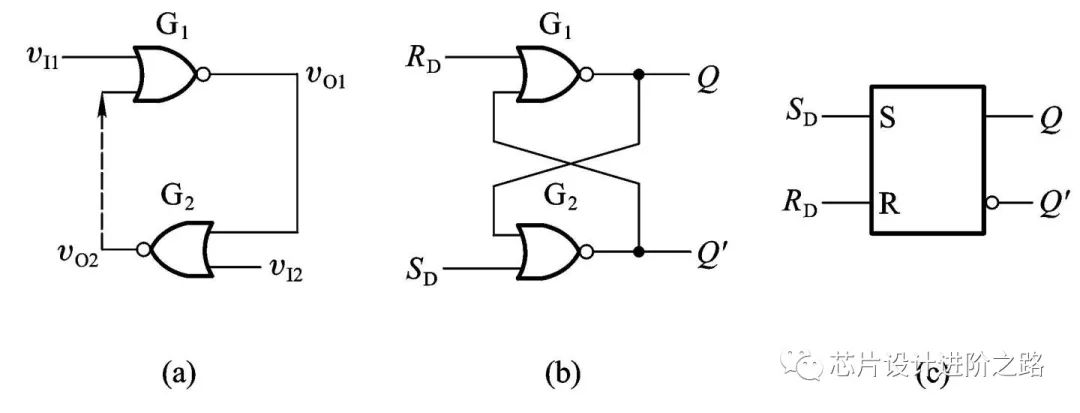

2.3.1 SR鎖存器

SR(Set-Reset)鎖存器,也叫基本RS觸發器是各種觸發器構成的基本部件,也是最簡單的一種觸發器。SR鎖存器電路結構和符號如下圖所示:

這里用的或非門搭建的SR鎖存器,同樣也可以用與非門搭建SR鎖存器,只需要把或非門換成與非門就可以了。

工作原理:

S端是置位端,S=1的時候把輸出Q置為1;

R端是復位端,R=1的時候把輸出Q復位成0;

當S=0, R=0的時候,輸出Q的值就保持前一個狀態的值,也就是把原理的狀態鎖存了。

當S=1, R=1的時候,根據與非門的特性,Q=0, Q=0, 這樣Q=Q;不符合輸出Q`=~Q的邏輯。所以S=1, R=1是不允許的狀態。這也是SR鎖存器的一個限制。

工程中,為了解除這個限制,一般都是把一個信號A接到S端同時把A通過一個反相器(非門)輸入到R端,這樣S,R就不可能同時為1了。

雖然SR鎖存器電路簡單,但是在應用中有兩個缺點:

- S,R不能同時為1;不夠方便;

- 鎖存的時間點不清楚,任何時刻,輸入都能直接改變輸出的狀態。也就是不知道什么時候鎖存了什么數據,沒有一個參考的時刻來確切的知道電路的狀態。

下面我們分析一下SR鎖存器的傳輸延時:

假設SR鎖存器的初始狀態是Q=0, Q`=1,與非門的傳輸延時是tpd。輸入信號波形如下圖所示:

- S的下降沿到達后,經過G1的傳輸延遲時間tpd,Q端變為高電平;

- Q端高電平加到門G2的輸入端,再經過門G2的傳輸延遲時間tpd, 使Q`變為低電平;

- 當Q`的低電平反饋到G1的輸入端以后,即使S=0變成S=1,觸發器被置成q=1狀態也將保持下去。

可見,為保證觸發器可靠地翻轉,必須等到Q`=0的狀態反饋到G1的輸入端以后,S=0的信號才可以取消。

因此,S輸入的低電平信號寬度tw應滿足tw≥2tpd。

同理,如果從R端輸入置0信號,其寬度也必須大于、等于2tpd。

可見,如果S,R端輸入的信號寬度很小,比如毛刺,那么輸出是不會改變的。SR鎖存器的結構,在門控時鐘切換防毛刺中很有用,后面會寫一篇文章專門講一下這個電路。

2.3.2 D 鎖存器

為了解決SR鎖存器的缺點,改進的結構就是D鎖存器。

D鎖存器最大的特點是,引入了一個特殊信號——時鐘信號。

注意:時鐘信號首先是一個信號,它只是一個特殊的信號,由于它的特殊性和重要性,所以他才有了一個名字叫做時鐘信號, 同樣的還有復位信號。在分析時鐘的時候,請不要忘記,時鐘信號首先是一個信號。

引入時鐘信號的作用是,作為參考和同步。因為時鐘是一個特殊的,高低電平循環的信號,它的行為是確定的, 而且送給不同電路的時鐘信號是同一個。所以就能以它作為參考。

比如,引入時鐘信號后,D鎖存器就只能在時鐘有效的時候,S和R才能起作用,也就是給SR加了一個前提條件,這樣對照周期性的時鐘信號,就能明確知道鎖存的時間點了。

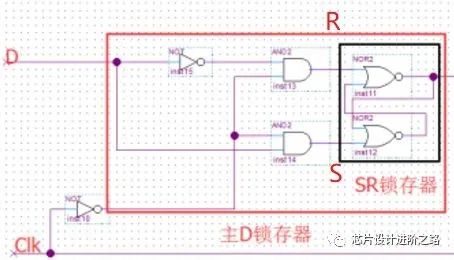

D鎖存器常見結構和電路符號圖如下所示:

可以看到,D鎖存器可以分為前級門電路(兩個與門和一個非門)和后級SR鎖存器組成。

下面我們就來分析一下它的功能:

輸入是Clk和D,也就是輸入有四種可能:

·當clk=0時,紅S紅R都為0,也就是SR鎖存器的輸入為00,根據SR鎖存器的功能,輸出Q和Q’將保持原來的狀態;因此clk=0時,不管D是什么,輸出Q和Q’都不隨D變化,只與原來的狀態有關,也就是保持。

·當clk=1時,R=(1·D’)=D’;S=(1·D)=D。

也就是說,當clk=1的時候,SR鎖存的輸入是互補的,不會出現S和R同時有效的情況。當D=1時,S=1,置位有效,輸出Q=1;當D=0時,R=1,復位有效,輸出Q=0;因此就可以知道,在clk=1時,輸出Q=D,也就是輸出等于輸入。

通過上面的分析,上面的D鎖存器結構功能為:在clk=1時,數據通過D鎖存器流到了Q;在Clk=0時,Q保持原來的值不變。這樣的鎖存器也稱為透明鎖存器或者電平敏感鎖存器。

注意:這里說的電平敏感是指時鐘電平為1的時候,輸入才能引起輸出變化。

2.4 觸發器(Flip-Flop)

雖然鎖存器結構簡單面積小,速度快,但是鎖存器是電平敏感的,在時鐘為高的時候,輸入信號的任何改變都會隨時引起輸出的改變,一個時鐘高電平期間可能會有多次改變。而且受布線延遲影響較大,很難保證輸出沒有毛刺產生。

為了改進這個缺點,就發明了邊沿觸發器,邊沿觸發器最大的特點是邊沿敏感的,也就是僅取決于CLK的下降沿(或上升沿)到來時的輸入信號狀態,與在此前、后輸入的狀態沒有關系。這樣就提高可靠性,增強抗干擾能力。

最常見最簡單的觸發器就是D觸發器。

2.4.1 D 觸發器

D觸發器的結構和電路符號圖如下所示:

D觸發器可以由兩個D鎖存器構成,驅動時鐘的相位相反,前面的D鎖存器稱為主鎖存器,后面的D鎖存器稱為從鎖存器,因此D觸發器也可以稱為主從觸發器。

下面我們分析一下D觸發的功能(注意主鎖存器的時鐘是clock取反):

假設要傳輸的數據D=D1:

在時鐘clk=0的時候,主鎖存打開進行傳輸數據,把輸入傳送到從到從鎖存器的輸入端,即Qm = D1。然后clk從0→1的時候,主鎖存器準備關閉,保持原來的值D1,與此同時從鎖存器準備打開,把Qm的值傳輸到輸出Qs,也就是Qs=Qm=D1。

在clk=1的時候,主鎖存器是關閉的,Qm保持D1不變,即Qm=D1;從鎖存器是打開的,Qs=Qm=D1。接著clk從1→0的時候,主鎖存器準備打開,準備傳輸數據;而從鎖存器準備關閉。在clk=0的時候,主鎖存打開進行傳輸數據,把輸入傳送到從到從鎖存器的輸入端,即Qm *= D2;與此同時,從鎖存器關閉,由于新的Qm即Qm*還沒有到達從鎖存器的D端,因此在從鎖存器關閉的時候,從鎖存器鎖存的是原來的值即D1,因此輸出Qs =D1。然后接下來上升沿就傳輸D2....

從上面的分析可以找到,D觸發器在時鐘上升沿的時候鎖存在時鐘上升沿采到的值,并且保持一個時鐘周期。這種在時鐘上升沿鎖存數據的觸發器稱為正邊沿觸發器,與此對應的還有負邊沿觸發的觸發器,這里就不進行介紹了。

由D觸發器延伸出去的知識點還有很多,比如寄存器:

寄存器(Register)由多個D觸發器構成(一個D觸發器可以看做1位的寄存器);寄存器可以看成是多位的DFF。

比如帶使能的觸發器:

再比如帶復位的觸發器:

3. 建立時間和保持時間

3.1 建立時間和保持時間的定義

下面我們通過分析D觸發器來理解建立時間和保持時間。

如果想深入理解一個概念,那么我們一定要知道這個概念的清晰的定義。

建立時間和保持時間都是針對觸發器的特性說的,比如對于一個D觸發器:

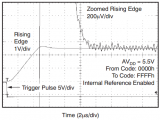

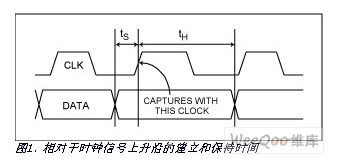

時序圖如下:

建立時間(Tsu:set up time):

是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間。如果建立時間不夠,數據將不能在這個時鐘上升沿被穩定的打入觸發器,Tsu就是指這個最小的穩定時間。

保持時間(Th:hold time):

是指在觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間。如果保持時間不夠,數據同樣不能被穩定的打入觸發器,Th就是指這個最小的保持時間。

建立時間和保持時間其實就是數據在時鐘上升沿前后的一個時間窗口內必須保持穩定,不然數據就不能正確的存到觸發器。

3.2 為什么需要建立時間和保持時間

那么為什么會有建立時間和保持時間的要求呢?

D觸發器的門級電路如下:

我們知道D觸發器是在(上升)邊沿進行鎖存數據的,也就是clk從在0→1的時候鎖存數據,那我們就看看這個上升沿的時候發生了什么:

假設原來的數據是1(也就是從鎖存器鎖存的數據是1),然后我們要鎖存的數據是0。

要讓D端的輸入0在Q端輸出,那么需要主鎖存器穩定的鎖定輸入的0,而從鎖存器則負責傳輸主鎖存器鎖存的數據。所以我們重點分析主鎖存器。

為了簡化分析假設反相器,與門,或非門這些門的延時都是tpd, 我們分析SR鎖存器的輸入端。假設輸入D從0->1相對于CLK上升沿的延時是tdd, 那么輸入端S的波形如下:

可以看到,CLK取反有tpd的延時,S端輸入相對于D端也有tpd的延時。這樣S=~Clk & D后第一個脈沖的寬度就是tw=tdd。

同樣分析R端也可以得到相同的結論。

也就是說,輸入數據D在時鐘上升沿到來之前穩定的時間就表現為SR鎖存器的S/R端信號的脈沖寬度。

參考2.3.1的分析,SR鎖存器對輸入信號的脈沖寬度是有要求的。

S輸入的低電平信號寬度tw應滿足tw≥2tpd

所以,我們可以得到tw=tdd≥2tpd.

也就是說,數據在時鐘上升沿到來之前,穩定時間必須要不小于2tpd(tpd為門電路延時), 才能被正確的采樣到。

這就是建立時間:Tsu ≥2tpd

同樣的分析,我們可以得到保持時間: Th≥2tpd

所以,我們的結論就是,由于門電路的延時和觸發器的電路結構,建立時間和保持時間是一定存在的,否則就不能滿足觸發器的功能要求。

4. 后記

建立時間和保持時間是時序分析最基礎的概念,很多工程師只知道這兩個概念的定義,但是未必知道需要建立時間和保持時間真正的原因。本文從CMOS門電路的結構和特性,逐步分析了為什么需要建立時間和保持時間的原因,為深入理解這兩個概念提供了幫助。

本文作者:烓圍瑋未。 主要從事ISP/MIPI/SOC/車規芯片設計

首發于知乎專欄:芯片設計進階之路

電子發燒友App

電子發燒友App

評論