一、芯片功耗概述

隨著移動(dòng)設(shè)備的興起和芯片工藝的提升,功耗成為近年來(lái)芯片設(shè)計(jì)越來(lái)越關(guān)注的話題。對(duì)功耗關(guān)注度的提升大致可以從兩方面進(jìn)行分析,用戶角度和芯片設(shè)計(jì)者角度。

從用戶角度來(lái)看 :

如今手機(jī)、PAD、TWS耳機(jī)等便攜式設(shè)備在生活中扮演著重要的角色,芯片功耗越大,對(duì)于同等的電池容量意味著使用時(shí)間越短;如果使用時(shí)間過(guò)短,對(duì)于現(xiàn)代人們的出行、支付、交流等方面帶來(lái)不便,會(huì)使我們?nèi)粘I畹陌踩薪档汀P酒脑礁撸謾C(jī)等便攜式設(shè)備消耗的能量越多,進(jìn)而產(chǎn)生的熱量也會(huì)越多。發(fā)熱越嚴(yán)重,熱噪聲越大,就會(huì)影響器件的正常工作,導(dǎo)致手機(jī)運(yùn)行速度變慢等問(wèn)題,會(huì)大大影響用戶。

從芯片設(shè)計(jì)者來(lái)看 :

隨著工藝的進(jìn)步,芯片內(nèi)部集成電路的密度越來(lái)越高,運(yùn)行速度越來(lái)越快,而片上的連線越來(lái)越細(xì),片上的供電網(wǎng)絡(luò)必須將電力以更少連線資源送至每個(gè)單元,這就要求芯片設(shè)計(jì)者在設(shè)計(jì)階段減少功耗的需求。另外如果不注意低功耗設(shè)計(jì),還會(huì)導(dǎo)致后期成本增加,例如,芯片低功耗設(shè)計(jì)不好,發(fā)熱量就可能增加,在封裝的時(shí)候,就需要考慮怎么給芯片進(jìn)行散熱,從而增加了封裝的散熱成本。成本的增加還會(huì)進(jìn)一步導(dǎo)致芯片的市場(chǎng)競(jìng)爭(zhēng)力降低,所以對(duì)芯片進(jìn)行低功耗設(shè)計(jì)是十分必要的。

二、功耗來(lái)源

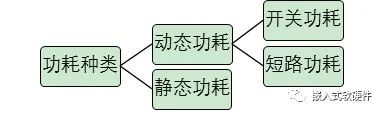

對(duì)芯片進(jìn)行低功耗設(shè)計(jì)時(shí)要首先搞清芯片功耗的來(lái)源,這樣才能有針對(duì)性的進(jìn)行控制。從功耗的種類來(lái)看,功耗主要來(lái)自三個(gè)地方,如下圖所示。

1. 開(kāi)關(guān)功耗

在數(shù)字CMOS電路中,對(duì)負(fù)載電容進(jìn)行充放電時(shí)消耗的功耗。比如對(duì)于下面的CMOS非門(mén)中:當(dāng)Vin = 0時(shí),上面的PMOS導(dǎo)通,下面的NMOS截止,VDD對(duì)負(fù)載電容Cload進(jìn)行充電,充電完成后,Vout的電平為高電平;當(dāng)Vin = 1時(shí),上面的PMOS截止,下面的NMOS導(dǎo)通,負(fù)載電容通過(guò)NMOS進(jìn)行放電,放電完成后,Vout的電平為低電平。這樣一開(kāi)一閉的變化,電源的充放電,就形成了開(kāi)關(guān)功耗

開(kāi)關(guān)功耗Pswitch的計(jì)算公式如下所示,其中VDD為供電電壓,Cload為后級(jí)電路等效的電容負(fù)載大小,Tr為輸入信號(hào)的翻轉(zhuǎn)率

2. 短路功耗

短路功耗也稱為內(nèi)部功耗,短路功耗是因?yàn)樵谳斎胄盘?hào)進(jìn)行翻轉(zhuǎn)時(shí),信號(hào)的翻轉(zhuǎn)不可能瞬時(shí)完成,因此PMOS和NMOS不可能總是一個(gè)截止另外一個(gè)導(dǎo)通,總有那么一段時(shí)間是使PMOS和NMOS同時(shí)導(dǎo)通,那么從電源VDD到地VSS之間就有了通路,就形成了短路電流。

短路功耗Pshort的計(jì)算公式如下所示,其中Vdd為供電電壓,Tr為翻轉(zhuǎn)率,Qx為一次翻轉(zhuǎn)過(guò)程中從電源流到地的電荷量。

3. 靜態(tài)功耗

在CMOS電路中,靜態(tài)功耗主要是漏電流引起的功耗,漏電流有下面幾個(gè)部分組成:

- PN結(jié)反向電流I1(PN-junctionReverse Current)

- 源極和漏極之間的亞閾值漏電流I2(Sub-threshold Current)

- 柵極漏電流,包括柵極和漏極之間的感應(yīng)漏電流I3(Gate Induced Drain Leakage)

- 柵極和襯底之間的隧道漏電流I4(Gate Tunneling)

靜態(tài)功耗的計(jì)算公式如下所示,其中Vdd為供電電壓,Ipeak為所有泄漏電流之和,除了式中列出的影響因素外,溫度對(duì)靜態(tài)功耗也有顯著影響,一般靜態(tài)功耗會(huì)隨著溫度的升高呈指數(shù)上升。

三、功耗控制方法

從第二節(jié)的描述中可以看出芯片的功耗的大小主要與供電電壓、運(yùn)行頻率和電路負(fù)載相關(guān),針對(duì)這些影響因素芯片設(shè)計(jì)者主要采用了如下辦法:

1. clock gating

在芯片中翻轉(zhuǎn)率最高的路徑就是clock path,clk path上的功耗消耗會(huì)占據(jù)到整個(gè)芯片功耗比例的40%甚至更多。clock經(jīng)pll 和預(yù)分頻器輸出后,后面會(huì)驅(qū)動(dòng)成千上萬(wàn)寄存器,并且為了增加clock的驅(qū)動(dòng)能力,在clock path上會(huì)插入許多buffer,而clock 每個(gè)cycle翻轉(zhuǎn)就會(huì)帶動(dòng)整條path上所有cell 翻轉(zhuǎn)。如果當(dāng)某一個(gè)subsys 或者module 不工作時(shí)clock仍在toggle,那么就會(huì)產(chǎn)生很大的功耗浪費(fèi)。如果能夠根據(jù)系統(tǒng)或者任務(wù)的需要對(duì)clock 做動(dòng)態(tài)的關(guān)斷就能極大地節(jié)省功耗消耗,這種對(duì)clock 進(jìn)行關(guān)斷的技術(shù)就是clock gating(時(shí)鐘門(mén)控)。如下圖,clock gating 技術(shù)主要就是在原來(lái)的clock path上加入enable 信號(hào),使clock 在滿足一定條件后才能往后傳輸。

根據(jù)clock gating 所加的層次,大體可以分為三個(gè)類型:

- 粗粒度門(mén)控:這種clock gating主要由架構(gòu)師決定,他們根據(jù)整個(gè)soc 的工作情況來(lái)決定在那些pll 或者預(yù)分頻器的輸出端添加門(mén)控邏輯。

- 中粒度門(mén)控:這種clock gating由模塊設(shè)計(jì)師決定,他們根據(jù)模塊的功能決定是否在模塊外部或者模塊內(nèi)部的子模塊處添加門(mén)控邏輯;

- 細(xì)粒度門(mén)控:這種主要是面向寄存器級(jí)別,可以使寄存器idle時(shí)將寄存器前端的clock 關(guān)掉。這種設(shè)計(jì)的優(yōu)勢(shì)是即使模塊正在工作,模塊內(nèi)部某些處于空閑狀態(tài)寄存器的clcok 也會(huì)被關(guān)掉,進(jìn)一步節(jié)省模塊內(nèi)部的功耗。這種gating對(duì)designer 的編碼有一定要求,當(dāng)designer 按照如下圖所示模式進(jìn)行硬件編碼時(shí),綜合工具會(huì)自動(dòng)在插入門(mén)控邏輯。

Clock gating 方式可以分為auto gating 和force gating,auto gating 為系統(tǒng)正常工作時(shí)的方式,門(mén)控單元根據(jù)自己所負(fù)責(zé)的cell/module/subsys的工作狀態(tài)動(dòng)態(tài)的關(guān)斷和打開(kāi)clock;force gating多用在調(diào)試階段或者作為備用方法,強(qiáng)制關(guān)掉或打開(kāi)某個(gè)clock觀察其運(yùn)行情況或者功耗變化。

2. DVFS

DVFS技術(shù)即dynamicvoltage dynamic frequency scaling,動(dòng)態(tài)電壓頻率技術(shù),是系統(tǒng)根據(jù)負(fù)載的變化來(lái)動(dòng)態(tài)地調(diào)整電壓和頻率的技術(shù)。如果一個(gè)電路能夠估算出它必須做多少工作才能完成當(dāng)前的任務(wù),那么理論上講就可以將時(shí)鐘頻率調(diào)低到剛好能適時(shí)完成該任務(wù)的水平。時(shí)鐘頻率和電壓緊密相關(guān),降低時(shí)鐘頻率意味著可以同時(shí)降低供電電壓。頻率和電壓同時(shí)降低,功耗就大大降低了。

DVFS 一般流程如下:

- 首先計(jì)算系統(tǒng)當(dāng)前的負(fù)載,這個(gè)負(fù)載可以軟件統(tǒng)計(jì)得出也可以由硬件計(jì)算;

- 根據(jù)負(fù)載計(jì)算當(dāng)前系統(tǒng)需要的頻率并進(jìn)行設(shè)置;

- 根據(jù)頻率選擇相應(yīng)的電壓進(jìn)行設(shè)置。

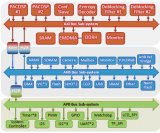

DVFS技術(shù)可以通過(guò)軟件和硬件的方式實(shí)現(xiàn),但電路中必須有電源管理模塊和時(shí)鐘管理模塊。真正硬件實(shí)現(xiàn)的dvfs 結(jié)構(gòu)比較復(fù)雜,包括dvfs trigger 模塊/dvfs map 模塊/votage compare 模塊/arbitration 模塊等。

3. multi voltage

由第二節(jié)的描述可知,動(dòng)態(tài)功耗和電壓的平方成正比,靜態(tài)功耗和電壓成正比,所以降低電壓對(duì)功耗的改善會(huì)很明顯。multi-voltage(多電壓域) 設(shè)計(jì)思想就是讓SOC內(nèi)的每個(gè)模塊/IP根據(jù)自己的需要,工作在不同電壓域,這樣可以減少所有模塊共電壓域造成的功耗浪費(fèi)。

信號(hào)在不同電壓域間進(jìn)行傳輸時(shí),可能會(huì)存在驅(qū)動(dòng)不足或者過(guò)驅(qū)動(dòng)等問(wèn)題。例如當(dāng)一個(gè)低電壓域的信號(hào)去驅(qū)動(dòng)高電壓域的cell時(shí),欠驅(qū)動(dòng)力的信號(hào)不僅增加了輸入端的上升時(shí)間和下降時(shí)間,增加短路電流的持續(xù)時(shí)間,還會(huì)使時(shí)序變差。為了解決這個(gè)問(wèn)題,需要在不同電壓域之間添加level-shifter(電平轉(zhuǎn)換器),它可以實(shí)現(xiàn)將某個(gè)電壓域的輸出電平轉(zhuǎn)換成另一個(gè)電壓域可以識(shí)別的邏輯電平。

多電壓設(shè)計(jì)技術(shù)可以分為三種方式:

- 各電壓區(qū)域有固定的電壓,這種方式不能夠根據(jù)自己的負(fù)載調(diào)節(jié)電壓,如圖(a)所示 ;

- 各電壓區(qū)域具有固定的多個(gè)電壓,可以根據(jù)負(fù)載調(diào)節(jié)電壓,但必須由軟件決定選擇哪一個(gè)電壓,如圖(b)所示;

- 自適應(yīng)的方式,各電壓域具有可變的,可以根據(jù)負(fù)載調(diào)節(jié)電壓,可以由軟件或者硬件決定選擇哪一個(gè)電壓,如圖(c)所示。

4. power gating

當(dāng)芯片內(nèi)部的模塊/IP不工作時(shí),即使我們把輸入端的時(shí)鐘和數(shù)據(jù)全部隔離,仍然會(huì)有部分漏電存在。工藝提升使芯片內(nèi)部集成的晶體管數(shù)量越來(lái)越多,漏電功耗在芯片整體功耗的比重也越來(lái)越大,讓設(shè)計(jì)師不得不關(guān)注這部分漏電。power gating(電源門(mén)控)技術(shù)是指將芯片中某個(gè)區(qū)域的供電電源關(guān)掉,斷電后,芯片進(jìn)入深度睡眠模式,其漏電功率很小,只剩power switch 的功耗。

實(shí)現(xiàn)這種技術(shù)需要isolation cell(電源隔離單元) 和retention cell(保持寄存器)的支持。isolation cell主要使模塊的輸入/輸出在電源關(guān)掉時(shí)信號(hào)保持為常數(shù),從而避免信號(hào)懸空或者胡亂toggle;retention cell可以在關(guān)掉電源時(shí)將寄存器的狀態(tài)保留下來(lái),為subsys或module 的喚醒保留必要的初始數(shù)據(jù)。

powergating有兩種方式:auto shutdown 和force shutdown。Auto shutdown 是系統(tǒng)正常工作使用的方式,芯片ALL ON 區(qū)域的PMU 單元會(huì)監(jiān)測(cè)個(gè)subsys內(nèi)各module的運(yùn)行情況,當(dāng)各module 處于idle 狀態(tài)時(shí),subsys就可以進(jìn)入深睡狀態(tài);一旦監(jiān)測(cè)到subsys內(nèi)module的工作請(qǐng)求,subsys 就會(huì)自動(dòng)退出睡眠狀態(tài)。Force shutdown 一般用在調(diào)試階段,也作為auto shutdown 模式失效時(shí)的備用方法。

5. 多閾值電壓設(shè)計(jì)

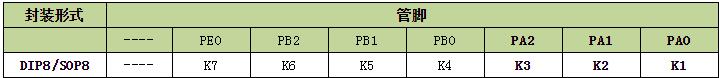

如第4小節(jié)所述,工藝的進(jìn)步雖然使芯片的晶體管(門(mén))數(shù)增多、供電電壓變低、尺寸減小,但卻使靜態(tài)功耗的比重越來(lái)越大。據(jù)統(tǒng)計(jì)在90nm或以下的工藝,靜態(tài)功耗要占整個(gè)設(shè)計(jì)功耗的20%以上,這就需要對(duì)功耗作更深層次的優(yōu)化。工藝庫(kù)中存在著不同的cell類型,cell 類型的速度、電壓和漏電可以用下表表示:閾值電壓越高,cell速度越慢,功耗越小;反之閾值電壓越低,cell速度越快,功耗越高。

多閾值電壓設(shè)計(jì)的策略是:對(duì)于性能要求高的模塊,或者頻率比較高的部分,采用閾值電壓比較低的cell,以減少單元門(mén)的延遲;對(duì)于性能要求較低的模塊,或者頻率較低的部分,多采用閾值電壓比較高的cell,讓功耗更低。通過(guò)這種方法,可以實(shí)現(xiàn)在同一塊芯片上,根據(jù)性能和功耗的不同要求而調(diào)整cell的使用,從而避免在不太重要的功能上浪費(fèi)過(guò)多的功耗。

6. 低功耗的布局規(guī)劃

這一部分工作中沒(méi)有參與過(guò),只簡(jiǎn)單介紹一下為了實(shí)現(xiàn)低功耗,布局布線的規(guī)則:

- 對(duì)于設(shè)計(jì)中翻轉(zhuǎn)活動(dòng)很頻繁的節(jié)點(diǎn),采用低電容的金屬層進(jìn)行布線;

- 使高翻轉(zhuǎn)率的節(jié)點(diǎn)盡可能地短;

- 對(duì)于高負(fù)載的節(jié)點(diǎn)與總線,采用低電容的金屬層;

- 對(duì)于特別寬的器件,采用特殊的版圖技術(shù),以得到更小的漏極結(jié)電容;

- 在有些布局布線工具中,可以將功耗作為優(yōu)化目標(biāo)來(lái)生成時(shí)鐘。

四、功耗驗(yàn)證方式

為了驗(yàn)證功耗的大小,在芯片tapeout之前與tapoout 之后有不同的驗(yàn)證工具。在tapeout 之前使用工具進(jìn)行仿真驗(yàn)證;tapeout之后使用精密電流源精密電流源進(jìn)行實(shí)測(cè)分析。

1. 前仿真

一般使用Spypower,如下圖所示。但是spypower里面自帶綜合工具,不需要輸入netlist文件,可以在設(shè)計(jì)前期應(yīng)用于功耗分析。

由于spypower是利用自身的綜合引擎進(jìn)行自綜合,所得功耗數(shù)據(jù)與PTPX相比,誤差較大,一般是利用spypower看不同版本間相對(duì)數(shù)據(jù)的變化。Spypower雖然在功耗準(zhǔn)確度方面較差,但它提供了豐富的功耗優(yōu)化數(shù)據(jù)可以用于功耗優(yōu)化,如下圖所示。Cgr可以用于觀察添加時(shí)鐘門(mén)控寄存器的比例;cge 可以用觀察時(shí)鐘門(mén)控的效率;rodf和rode可以用于觀察寄存器輸出端與時(shí)鐘輸入端的比值,進(jìn)一步檢驗(yàn)插入的clock gate 是否合適。

當(dāng)然,前仿真還有power artist工具,功能類似,本文暫不展開(kāi)。

2. 后仿真

后仿真一般使用較多時(shí)PTPX,PTPX 是芯片設(shè)計(jì)公司普遍使用的功耗仿真工具,不僅仿真精度高,而且產(chǎn)生的功耗數(shù)據(jù)豐富,便于進(jìn)行功耗分析。使用PTPX 工具不僅可以產(chǎn)生一段波形的平均功耗,還可以產(chǎn)生每一時(shí)刻的瞬時(shí)功耗;不僅可以產(chǎn)生基于block的功耗,還可以報(bào)告出block內(nèi)部 每一個(gè)層次的功耗,甚至是每個(gè)cell的功耗;不僅可以產(chǎn)生整體的功耗,還可以按照memory、clock、pad等分類產(chǎn)生功耗。

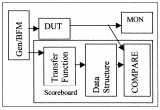

PTPX工作流程如下圖所示,用戶提供lib、netlist、activity和parasitic文件,然后PTPX工具按照一定的算法對(duì)各種數(shù)據(jù)進(jìn)行統(tǒng)計(jì)和計(jì)算,最后產(chǎn)生功耗報(bào)告。各種文件的作用如下所述:

- tech library:工藝庫(kù)文件,里面包含著各種cell在不同狀態(tài)下的功耗信息。

- netlist:門(mén)級(jí)網(wǎng)表電路,通過(guò)綜合得到,里面包含著芯片中使用的cell 類型。

- parasitic:包含設(shè)計(jì)中連線等寄生參數(shù),比如寄生電容、寄生電阻,這個(gè)一般是后端RC寄生參數(shù)工具提供。

- switch activity:包含設(shè)計(jì)中每個(gè)節(jié)點(diǎn)的開(kāi)關(guān)行為情況,比如說(shuō)節(jié)點(diǎn)的翻轉(zhuǎn)率或者可以計(jì)算出節(jié)點(diǎn)翻轉(zhuǎn)率的文件,可以為saif、vcd和fadb文件。

雖然不同的功耗類型,PTPX的計(jì)算公式不同,但都是通過(guò)從netlist文件中確定使用的cell 類型,從activity 文件中確定cell的狀態(tài),從parasitic文件中確定對(duì)應(yīng)狀態(tài)的負(fù)載大小,然后再去lib 文件中查找cell在當(dāng)前狀態(tài)下的功耗,最后將所有cell的功耗相加。

拿leakage的計(jì)算舉例說(shuō)明,cell的leakage 在工藝庫(kù)中描述如下,其中Leakage_power_unit標(biāo)示leakage power的單位;cell_leakage_power標(biāo)示固定的leakage power值,如果library里沒(méi)有該變量的定義,或者該變量是個(gè)負(fù)值,工具會(huì)用default_cell_leakage_power的值,如果default_cell_leakage_power也沒(méi)有指定,則用default_leakage_power_density的值乘以該cell的面積來(lái)計(jì)算得出一個(gè)leakage值,如果這三個(gè)變量都沒(méi)有定義,則leakage的值為0;

leakage_power()這一部分就是用來(lái)定義跟輸入狀態(tài)相關(guān)的leakage power,其中"when"用于定義輸入的狀態(tài),如果某種狀態(tài)沒(méi)有定義,則用cell_leakage_power定義的值來(lái)計(jì)算leakage;power_level用于多電壓cell中指定是跟哪個(gè)電壓相關(guān)的leakage power。

單個(gè)cell leakage power計(jì)算公式如下,其中K表示cell 包含的state數(shù)量;Pstate_leakage表示cell在當(dāng)前state的功耗大小;probability表示每種狀態(tài)的占比。PTPX工具就是按照如下公式逐個(gè)統(tǒng)計(jì)cell的功耗,最后相加。

3. 精密電流源

芯片tapout之后,功耗測(cè)試主要依靠精密電流源進(jìn)行,將精密電流的輸出端連接芯片的供電端,就可以得到芯片工作時(shí)的電流。精密電流源具有如下特點(diǎn):

- 精度高,擁有三種測(cè)量范圍

- 可編程接口,方便自動(dòng)化測(cè)試

- 可以顯示電流圖,方便進(jìn)行功耗分析

- 具有trigger 功能,能夠抓住具有明顯特征的波峰

- 擁有多個(gè)輸出通道,可以測(cè)量多個(gè)powerrail

4. 其他IC設(shè)計(jì)相關(guān)工具和方法

UTF(Unified Power Format),其作用是把功耗設(shè)計(jì)意圖(powerintent)傳遞給EDA工具,從而幫助實(shí)現(xiàn)物理設(shè)計(jì)。這就類似于綜合時(shí)的約束,是把跟時(shí)序相關(guān)的設(shè)計(jì)意圖傳達(dá)給EDA。說(shuō)簡(jiǎn)單一些,UPF就是一些tcl命令,系統(tǒng)架構(gòu)師通過(guò)這些命令的組合,把真實(shí)的低功耗設(shè)計(jì)意圖傳遞給工具。

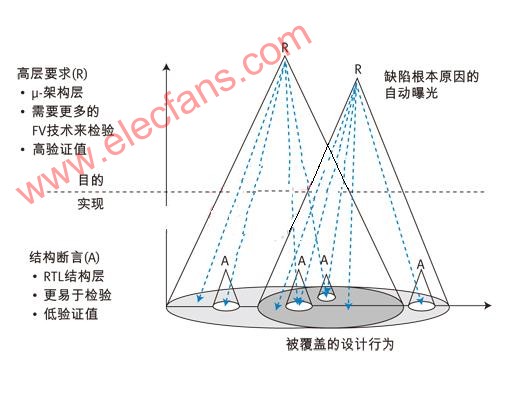

CLP(Conformal Low Power),低功耗檢查是低功耗設(shè)計(jì)必不可少的一個(gè)環(huán)節(jié),此處所謂的低功耗設(shè)計(jì)指:多電壓域設(shè)計(jì),實(shí)現(xiàn)過(guò)程中在原有功能邏輯基礎(chǔ)上插入低功耗單元,如:isolation cell, level shifter cell, retention register, power switch等。

此外,還有RTL級(jí)功耗優(yōu)化平臺(tái)PowerPro。

五、功耗評(píng)估內(nèi)容

利用上節(jié)所述的功耗驗(yàn)證工具,一般會(huì)進(jìn)行如下功耗評(píng)估:

1. 場(chǎng)景功耗分析

場(chǎng)景功耗分析一般是為大系統(tǒng)軟件服務(wù),為大系統(tǒng)軟件提供場(chǎng)景的功耗target和golden 配置。場(chǎng)景功耗分析之前首先要定義功耗需求,進(jìn)行競(jìng)品分析,確定功耗目標(biāo),分解功耗場(chǎng)景,然后才利用工具進(jìn)行場(chǎng)景功耗分析。

場(chǎng)景功耗分析的流程一般為:

- 定義場(chǎng)景,包括場(chǎng)景數(shù)據(jù)流、場(chǎng)景代碼流、場(chǎng)景各power domain狀態(tài)等;

- 根據(jù)場(chǎng)景定義進(jìn)行coding;

- 將編好的代碼在仿真器上運(yùn)行,并抓取activity文件;

- 利用PTPX工具對(duì)activity文件進(jìn)行功耗分析;

- 確定功耗達(dá)標(biāo)后,導(dǎo)出寄存器信息。

2. leakage分析

leakage 分析可以為產(chǎn)線提供交付標(biāo)準(zhǔn),也可以優(yōu)化deep sleep 場(chǎng)景功耗。

Leakage 分析使用ptpx 工具完成,網(wǎng)表ready 之后就可以進(jìn)行,無(wú)需波形。

Leakage 分析時(shí)不僅會(huì)分析power on 時(shí)的leakage,也會(huì)分析shutdown 時(shí)的leakage;分析多個(gè)corner leakage,如tt、ffg等;分析多個(gè)lib 下的功耗,不僅包括電壓的變化還有溫度的變化。

3. cgr/cge分析

cgr/cge分析主要針對(duì)designer的clock gating內(nèi)容,用于指導(dǎo)RTL designer 優(yōu)化設(shè)計(jì),改善clock gating 效率。

Cgr/cge分析主要使用spypower 工具完成,分析cgr時(shí)只需要rtl code即可;分析cge時(shí)需要activity 文件。利用spypower工具,可以列出register name、driving clock name、signal width、clock gating type等信息,這些信息可以使designer方便定位問(wèn)題,快速解決。

4. maxpower 和IR-drop

Maxpower和IR-drop都為pmic 設(shè)計(jì)人員服務(wù),maxpower 分析使pmic 輸出電壓能夠滿足最大功耗的要求并留出足夠的margin;IR-drop 分析使pmic 能夠應(yīng)對(duì)電源噪聲問(wèn)題,確保系統(tǒng)可以穩(wěn)定工作。

Maxpower由ptpx完成,maxpower pattern 要使系統(tǒng)clock 和負(fù)載最大,測(cè)量極端情況的功耗;IR-drop 分析涉及多個(gè)部門(mén),多種工具,引入IR-drop分析可以盡早發(fā)現(xiàn)功耗策略中的不足,提前想法解決。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論