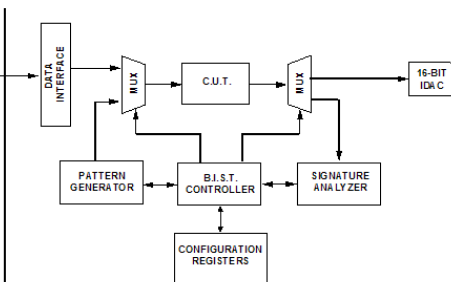

利用FPGA可重復編程的特性,通過脫機配置,建立BIST邏輯,即使由于線路被操作系統的重新配置而令BIST結構消失,可測性也可實現。本文給出一種基于BIST利用ORCA(Optimized

2018-11-28 09:02:00 4021

4021

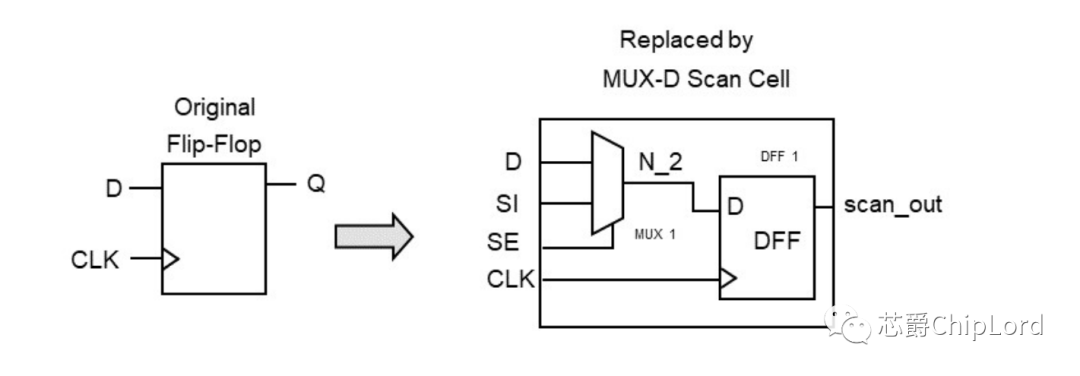

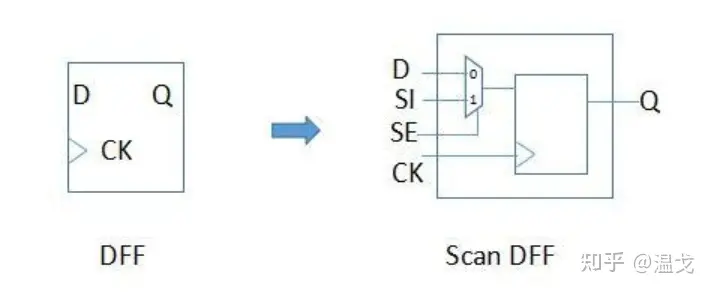

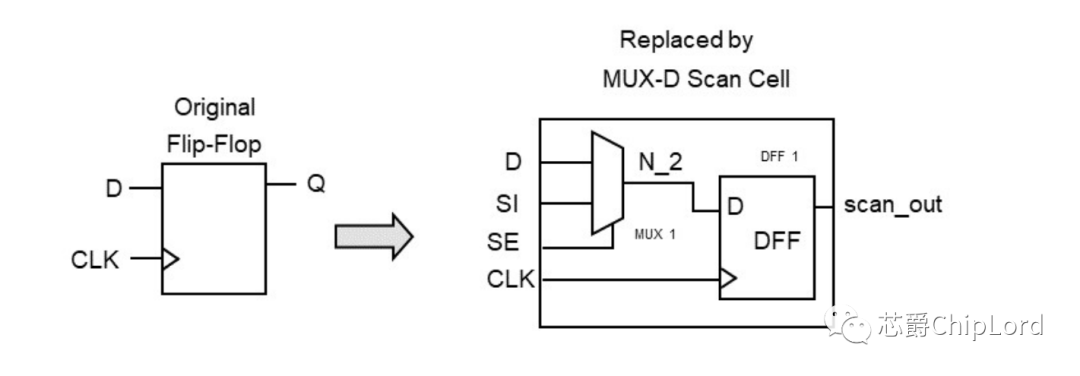

如下圖所示:左邊是普通寄存器,右邊是可掃描寄存器,D端前面加一個二選一的MUX,選擇端是scan_enable,為1時選擇SI端,為0時選擇D端。

2023-09-15 10:10:37 1762

1762

。為什么還會有2.4GHz的本振信號呢?是我理解錯了,還是我測試錯了?我測試的頻譜圖如附件所示。一張是使能BIST的,一張是不使能BIST的。附件Screen_0061.png83.6 KBScreen_0062.png82.9 KB

2018-08-01 09:10:10

BOARD EVALUATION SCAN90004

2023-03-30 11:45:02

SCAN921025 - 30-80 MHz 10 Bit Bus LVDS Serializer and Deserializer with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921025H - High Temperature 20-80 MHz 10 Bit Bus LVDS SerDes with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921226 - 30-80 MHz 10 Bit Bus LVDS Serializer and Deserializer with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921226HSM - High Temperature 20-80 MHz 10 Bit Bus LVDS SerDes with IEEE 1149.1 (JTAG) and at-speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN921260 X6 1:10 Deserializer with IEEE 1149.1 (JTAG) and at-speed BIST datasheet (Rev. F)

2022-11-04 17:22:44

SCAN921821 Dual 18-Bit Serializer w/Pre-emph, IEEE 1149.1 JTAG & At-Speed BIST datasheet (Rev. C)

2022-11-04 17:22:44

SCAN926260 - Six 1 to 10 Bus LVDS Deserializers with IEEE 1149.1 and At-Speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN926260 Six 1-10 Bus LVDS Deserializers w/IEEE 1149.1 & At-Speed BIST datasheet (Rev. H)

2022-11-04 17:22:44

SCAN926260TUF - Six 1 to 10 Bus LVDS Deserializers with IEEE 1149.1 and At-Speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN926260TUFX - Six 1 to 10 Bus LVDS Deserializers with IEEE 1149.1 and At-Speed BIST - National Semiconductor

2022-11-04 17:22:44

SCAN928028 8 Channel 10:1 Serializer with IEEE 1149.1 and At-Speed BIST datasheet (Rev. F)

2022-11-04 17:22:44

AD9361 BIST功能驗證相關事項想請問各位大拿,AD9361 BIST功能驗證是用于驗證收發通道的鏈路部分,而數據接口部分是不是驗證不到?當前調試過程中出現的問題是:配置模式FDD 1R1T

2021-09-14 22:29:00

ad9361初始化完成后使用bist模式測試ad9361的收發鏈路功能是否正確。配置寄存器0x3F4的值為0x5B時即連接到RX Dataport端口時,使用vivado下的ILA抓取輸入端rx波形

2019-11-17 23:03:17

模塊。測試中,使能ENSM進入FDD狀態,切換BIST灌入Tx Chain (etc. SPIWrite 03F453),FPGA內部抓取接收信號,可以看到IQ正弦波,但是質量很差,類似噪聲。后面我調節

2019-01-08 11:09:07

M0 在使用時有兩個scan IO 接口,分別為.SE.RSTBYPASS這兩個IO在芯片scan mode下需要做特別處理嗎?我們能否把它當成普通的數字IP直接進行top級的scan 呢?謝謝!如果進行top級的scan,能否把這里的SE置0, RSTBYPASS也置0?

2022-08-22 15:20:07

雖然可測性設計(DFT)與內置自檢(BIST)技術已在SoC(系統級芯片)設計中受到廣泛關注,但仍然只是被看作“后端”的事。實際上,這些技術在器件整個設計周期中都非常重要,可以保證產品測試錯誤覆蓋率

2011-12-15 09:53:14

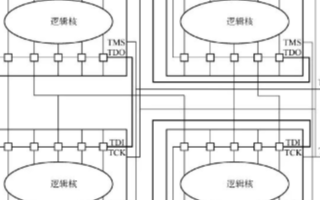

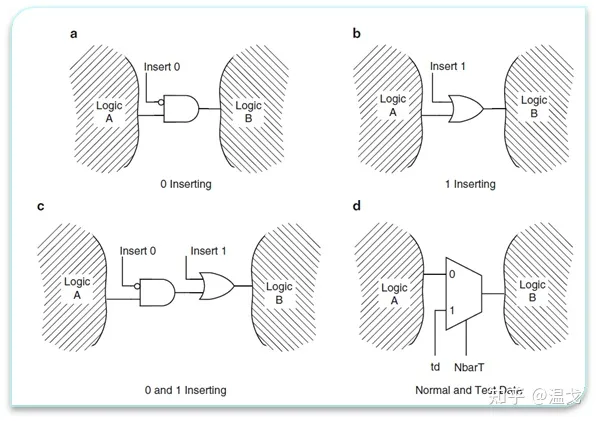

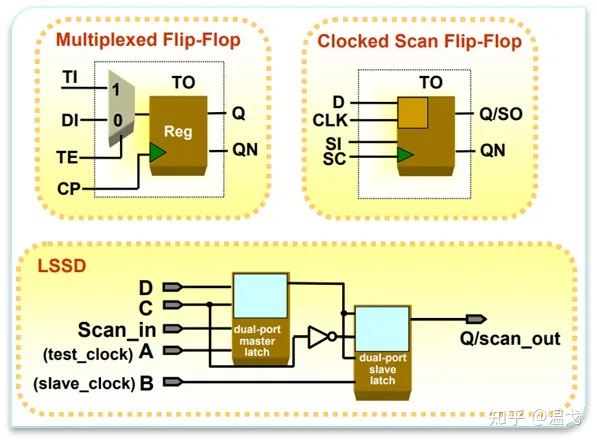

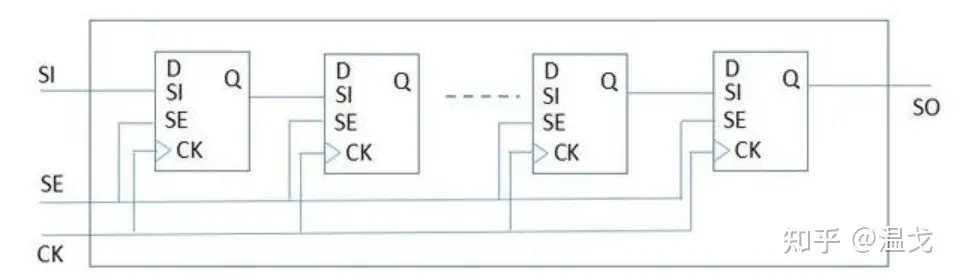

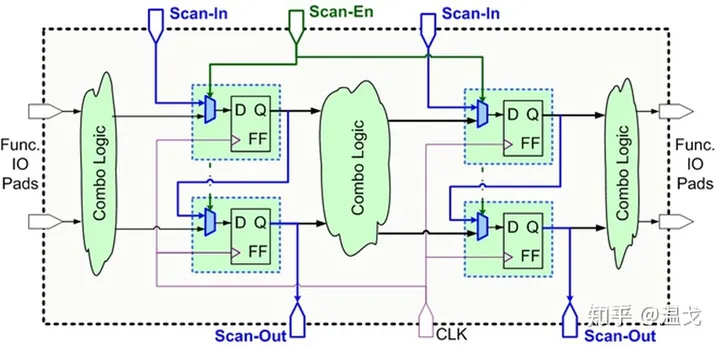

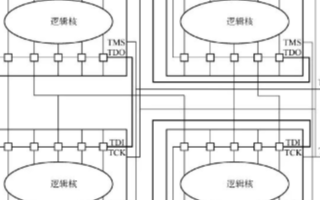

邊界掃描測試 為了對電路板級的邏輯和連接進行測試,工業界和學術界提出了一種邊界掃描的設計,邊界掃描主要是指對芯片管腳與核心邏輯之間的連接進行掃描。掃描路徑設計(Scan Design) 掃描路徑

2011-12-15 09:35:34

嗨,我試圖在ISE / SDK 14.6下編譯BIST的13.4版本,但是我遇到了一些與丟失文件和目錄有關的錯誤。我想知道其他人是否已經移植了BIST源代碼。至少我想知道你將如何繼續這項任務。所以,如果你有任何想法,我想聽聽他們。問候,KT

2020-03-17 10:22:01

你好,我沒有意識到有一種方法可以運行工廠加載到QSIP中的測試。一位同事在上面加載了一個XmWorks文件,現在我無法使用以前的BIST。有沒有辦法重置為默認值或您是否會發送新的下載?謝謝,克里斯

2019-09-12 10:46:39

我們現在正在評估 S32K BIST 功能,當 sw 調用 apiBist_Run() 以啟動 bist 時,但 mcu 重置。它發生在 Bist

2023-04-14 07:09:06

/ src / subdir.mk似乎是原因。在“C_SRCS + =”部分中:“../src/pcap.c \ / C:/zc706_bist/zc706_bist

2020-04-08 09:52:55

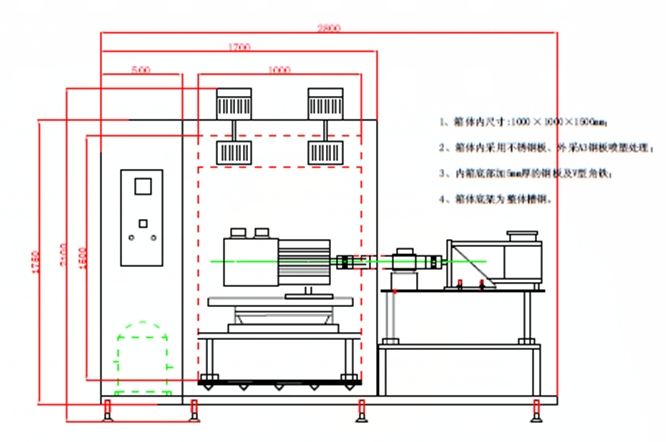

封裝功能測試,覆蓋1-1200管腳的各種封裝形式BGA、QFP、PGA、PLCC、TSSOP、DIP等。 IC功能測試服務:利用BOUNDARY SCAN(邊界掃描)測試設備提供各種常用芯片的直流功能

2009-07-21 11:40:36

s32g274a的板子支持BIST嗎?如果板子支持,如何在 s32g274a 上使用在線 BIST?

2023-04-20 07:15:26

嗨,我正在使用帶有DTM固件的BlueNRG-2芯片。它通過SPI連接到主處理器STM32。該藍牙設備在外圍設備中起作用(某些傳感器)。 廣告工作正常:作為主設備的另一個設備接收ADV_IND

2018-09-26 17:50:33

你好任何人都可以解釋為什么四種 DDR 驗證 BIST 測試類型無法執行并且顏色編碼指示“…………測試腳本中的錯誤”?我能夠成功執行 DDR 驗證階段和其他四種 DDR 驗證測試類型(DMA 測試

2023-04-06 08:54:58

問題如題:在SimpleBLEObserver和 SimpleBLECentral的范例工程中,都沒有找到設置LE_Scan_Window和LE_Scan_Interval這兩個參數的語句,是有缺

2020-03-17 09:11:19

在BIST測試中,其他測試通過了閃存測試,失敗的信息是 - 初始化時失敗 - 閃存測試失敗(1)可以任何人告訴我為什么,謝謝!

2020-05-05 08:42:01

你好我正在嘗試在SP605評估板上運行BIST。我沒有改變緊湊型閃存內容。我按照“Xilinx Spartan-6 FPGA SP605評估套件UG525入門指南”中的說明進行了跳線設置。但是當我按

2019-07-22 13:25:24

幾個月的研究,我們沒有設法取悅他,他告訴我們只是對故障覆蓋做一些測試。這是我們需要采用BIST設計并在VHDL(我們認為)中實現并測試它的文檔。這是文件。歡迎任何想法或幫助/解決!BIST.doc 1848 KB

2020-04-23 09:55:03

大家好,我只是想運行Digilent Xilinx Spartan-6(Atlys_Demo_BIST)附帶的初始測試程序。所以我連接電源和HDMI插頭(HDMI當然)并啟動電路板,沒有任何反應

2019-07-24 14:24:18

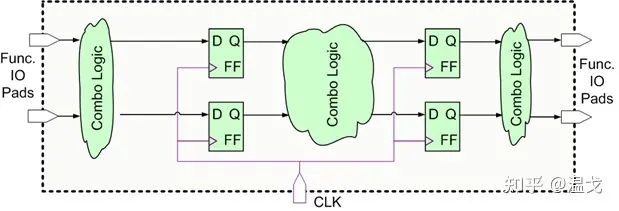

前面一期的公眾號文章“讓你徹底理解DFT”幫助大家理解了DFT所解決的問題。一句話來概括之就是:借助特定的輔助性設計,產生高效率的結構性測試向量以檢測生產制造過程中引入芯片中的各種物理缺陷。Scan

2016-06-14 14:20:20

設計,例如壓縮/解壓、無線模塊、網絡模塊等。而一塊SoC芯片的功能可能是多個獨立模塊的總和。另外,芯片的制造需要經歷化學、冶金、光學等工藝過程,在這些過程中可能引入物理缺陷導致其不能正常工作。因此對芯片的測試

2019-09-20 07:09:28

怎么實現基于LFSR優化的BIST低功耗設計?

2021-05-13 06:21:01

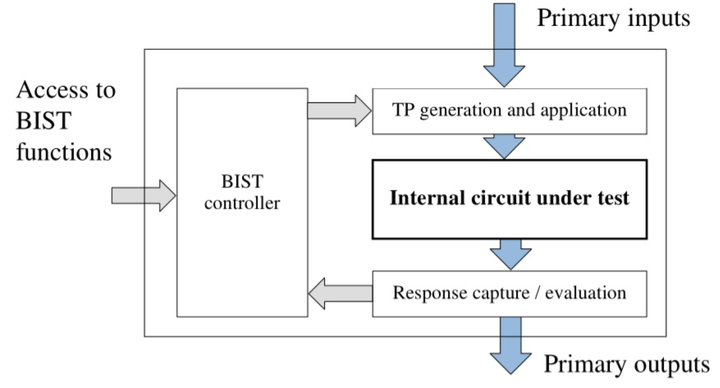

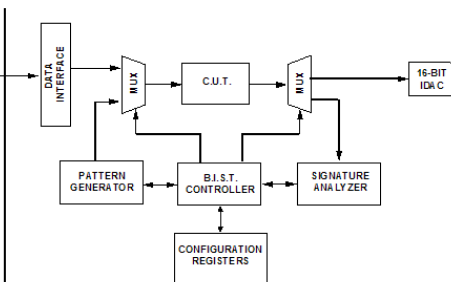

引言大多數IC設計工程師都了解數字BIST的工作原理。它用一個LFSR(線性反饋移位寄存器)生成偽隨機的位模式,并通過臨時配置成串行移位寄存器的觸發器,將這個位模式加到待測電路上。數字BIST亦用

2019-07-19 06:18:30

你好,我無法在我的Ubuntu 14.04 [.2] 64位桌面上運行BIST程序(如xtp242中所指定)。以下是我所做的一些事情: - 從Xilinx購買了Xilinx Zynq-7000

2019-10-08 10:58:00

通過FPGA進行并口的時序控制,寄存器已經成功讀寫,官方文檔上BIST相關寄存器 BIST Control設置使能,并將計時器賦值,輸入和通道寄存器也設置,直接讀取BIST I/Q Path

2018-08-18 07:04:30

請教一下各位,剛剛開始搞ad9361,ad9361 bist測試rx port只需要配置0x3f4寄存器就可以嗎?還需要配置其他寄存器嗎?如何配置?0x3f4配置為0x5b,如何測試rx port是否正常?現在通過示波器抓rx port data上沒有任何波形。

2018-08-16 06:58:45

您好,我正在使用 S32K344 評估 S32K BIST 功能。調用Bist_Run(BIST_SAFETYBOOT_CFG)時遇到hard fault,如圖。它發生

2023-04-20 06:44:58

The SCAN921260 integrates six deserializer devices into asingle chip. The SCAN921260 can

2009-10-13 10:01:52 24

24 The SCAN921821 is a dual channel 18-bit serializer featuringsignal conditioning, boundary SCAN

2009-10-13 10:03:30 10

10 The SCAN926260 integrates six 10-bit deserializer devicesinto a single chip. The SCAN926260 can

2009-10-13 10:05:04 8

8 The SCAN928028 integrates eight serializer devices into asingle chip. The SCAN928028 can

2009-10-13 10:07:10 19

19 The SCAN25100 is a 2457.6, 1228.8, and 614.4 Mbps serializer/deseralizer (SerDes) for high-speed

2009-10-14 08:40:07 17

17 The SCAN12100 is a 1228.8 and 614.4 Mbps serializer/deseralizer(SerDes) for high-speed

2009-10-14 08:44:37 17

17 摘要:針對某SOC中嵌入的8KSRAM模塊,討論了基于MarchC-算法的BIST電路的設計。根據SRAM的故障模型和測試算法的故障覆蓋率,研究了測試算法的選擇、數據背景的產生,并完成了基于Ma

2010-04-26 15:18:30 29

29 介紹了用于IP核測試的內建自測試方法(BIST)和面向測試的IP核設計方法,指出基于IP核的系統芯片(SOC) 的測試、驗證以及相關性測試具有較大難度,傳統的測試和驗證方法均難以滿足

2010-12-13 17:09:11 10

10 在BIST(內建自測試)過程中,線性反饋移位寄存器作為測試矢量生成器,為保障故障覆蓋率,會產生很長的測試矢量,從而消耗了大量功耗。在分析BIST結構和功耗模型的基礎上,針

2010-12-23 15:35:11 0

0 黑盒測試與白盒測試區別

黑盒測試 黑盒測試也稱功能測試或數據驅動測試,它是在已知產品所應具有的功能,通

2008-10-22 12:40:02 8981

8981 基于BIST的編譯碼器IP核測

隨著半導體工藝的發展,片上系統SOC已成為當今一種主流技術。基于IP復用的SOC設計是通過用戶自定義邏輯(UDL)和連線將IP核整合

2008-12-27 09:25:39 794

794

低功耗的BIST偽隨

2011-01-10 10:47:06 34

34 通常我們在設計芯片的同時,可以根據芯片本身的特征,額外地把可測性電路設計(Design For Testability)在芯片里。談到可測性的電路設計,內建自測試(BIST)和基于掃描Scan—Based)的電路設計

2011-06-10 10:13:45 2119

2119

數字BIST的工作原理:用一個LFSR(線性反饋移位寄存器)生成偽隨機的位模式,并通過臨時配置成串行移位寄存器的觸發器,將這個位模式加到待測電路上。

2011-11-23 15:24:27 2428

2428

衡量電機發熱程度是用“溫升”而不是用“溫度”。電機測試中涉及到溫度的測試主要時溫升測試及環境溫度測試,兩者是既有區別又有聯系的關系。

2016-06-03 09:23:35 3768

3768

基于功能復用的抗老化BIST設計_梁華國

2017-01-07 16:00:43 0

0 低成本BIST映射電路的設計與優化_張玲

2017-01-07 21:39:44 2

2

3 使用Testcompress 實現EDT壓縮scan chain

4 使用Testcompress 產生測試DC/ACpattern,同時產生測試驗證的Testbench

2017-10-26 16:01:36 34653

34653

隨著FPGA在現代電子系統中應用的不斷增多.FPGA的測試技術也得到非常快的發展。其中,內建白測試(BIST)的方法已經成為一種主流的解決方案。BIST方法一般來說可以分為兩大類,一類是離線BIST

2017-11-08 14:21:46 1

1 本文開始介紹了什么是耐壓測試和介紹進行耐壓測試的原因以及直流與交流耐壓測試的比較,其次介紹了絕緣測試的特性,最后介紹了絕緣和耐壓的區別以及區分了耐壓測試與絕緣測試的區別。

2018-04-03 09:30:10 103243

103243 電子發燒友網為你提供TI(ti)SCAN921821相關產品參數、數據手冊,更有SCAN921821的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SCAN921821真值表,SCAN921821管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發燒友網為你提供TI(ti)SCAN921260相關產品參數、數據手冊,更有SCAN921260的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SCAN921260真值表,SCAN921260管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發燒友網為你提供TI(ti)SCAN921025H相關產品參數、數據手冊,更有SCAN921025H的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SCAN921025H真值表,SCAN921025H管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發燒友網為你提供TI(ti)SCAN926260相關產品參數、數據手冊,更有SCAN926260的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SCAN926260真值表,SCAN926260管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發燒友網為你提供TI(ti)SCAN928028相關產品參數、數據手冊,更有SCAN928028的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SCAN928028真值表,SCAN928028管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發燒友網為你提供TI(ti)SCAN921226H相關產品參數、數據手冊,更有SCAN921226H的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SCAN921226H真值表,SCAN921226H管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

電子發燒友網為你提供TI(ti)SCAN921224相關產品參數、數據手冊,更有SCAN921224的引腳圖、接線圖、封裝手冊、中文資料、英文資料,SCAN921224真值表,SCAN921224管腳等資料,希望可以幫助到廣大的電子工程師們。

2018-10-16 11:16:58

內置自測(BIST),曾經保留用于復雜的數字芯片,現在可以在許多具有相對少量數字內容的設備中找到。

2019-04-12 14:14:28 2466

2466

到巨大的數字系統級芯片設計中。雖然片上內置自測(BIST)與環回操作相結合是昂貴的自動測試設備(ATE)的廣泛采用的替代方案,但其高速模擬部分的故障覆蓋率較差,嚴重影響整體產品現在,一種稱為無矢量測試的方法正在出現,它提供了兩種方法中的最佳方法:片上I/O BIST的成本效益與基于ATE的信號完

2023-11-10 16:57:23 270

270 邊界掃描測試(Boundary scan)是為了解決印制電路板(PCB)上芯片與芯片之間的互連測試而提出的一種解決方案。它與內部掃描有明顯的區別,前者是在電路的輸入/輸出端口增加掃描單元,并將這些

2020-04-13 17:31:16 10213

10213

α測試和β測試的區別

2020-06-29 11:22:49 25177

25177 靜態測試,動態測試的區別:程序是否運行。

2020-08-19 17:13:58 8475

8475 文主要探討了用全掃描結構(FULL SCAN METHOD)來實現數字電路可測性設計(DESIGN FOR TEST)的原理與方法。其中涉及到掃描結構(SCAN)的算法依據、電路的基本結構、測試矢量

2021-03-26 14:48:18 22

22 arp-scan.zip

2022-05-05 09:51:25 5

5 LBIST (Logic build-in-self test), 邏輯內建自測試。和MBIST同理,在關鍵邏輯上加上自測試電路,看看邏輯cell有沒有工作正常。BIST總歸會在芯片里加入自測試邏輯,都是成本。

2022-08-29 15:33:30 2169

2169 的BIST簽名檢查敏感,后者可以檢測單個比特錯誤。同樣的數字接口檢查可以在生產測試車間執行,也可以在現場的系統級自檢中執行。

2023-02-01 15:36:14 997

997 接著上文,MCU芯片設計了mbist、scan chain之后,功能仿真失敗?

2023-02-20 09:35:15 955

955 [摘要] T-Scan系統能精確記錄咬合接觸的時間、 力量、 面積和動態分析咬合接觸情況, 自問世以來通過產品的

不斷更新與發展, 使其更好地運用于口腔臨床和科研工作中。 本文就 T-Scan 系統的特點和臨床應用作一綜述。

[關鍵詞] T-Scan 系統; 咬合接觸; 咬合分析; 臨床應用

2022-04-01 15:59:51 1925

1925

AI芯片和SoC芯片都是常見的芯片類型,但它們之間有些區別。本文將介紹AI芯片和SoC芯片的區別。

2023-08-07 17:38:19 2103

2103 模擬到數字的信號不可控,需要和數字registered outputs mux一下提高test coverage。關鍵詞是registered output! 這個技巧俗稱scan loopback。

2023-12-08 11:24:40 533

533

FPGA芯片和普通芯片在多個方面存在顯著的區別。

2024-03-14 17:27:34 223

223

正在加载...

電子發燒友App

電子發燒友App

評論