基于有限狀態(tài)機(jī)和查找表的RICE解碼結(jié)構(gòu)

大小:1.23 MB 人氣: 2017-11-20 需要積分:0

推薦 + 挑錯(cuò) + 收藏(0) + 用戶評(píng)論(0)

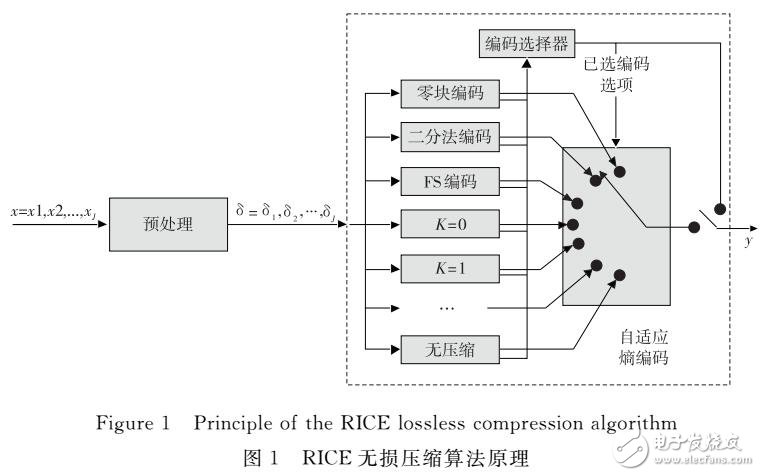

RICE算法在無(wú)損壓縮系統(tǒng)有著廣泛的應(yīng)用。由于RICE算法采用了變長(zhǎng)的自適應(yīng)熵編碼,因此在解碼時(shí)需要對(duì)壓縮流進(jìn)行逐位判斷和解析,這給高速解壓縮的實(shí)現(xiàn)帶來(lái)了困難。現(xiàn)有的RICE解碼實(shí)現(xiàn)在解碼速度和通用性上都不理想。針對(duì)RICE算法中自適應(yīng)熵編碼的特點(diǎn),設(shè)計(jì)了一種基于有限狀態(tài)機(jī)和查找表的并行RICE解碼結(jié)構(gòu),可在FPGA上完成8比特寬度的并行解碼,解碼速度最高可達(dá)176 MB/s;同時(shí),該解碼結(jié)構(gòu)適用于編碼參數(shù)足變化的情況,具有很強(qiáng)的通用性。

非常好我支持^.^

(0) 0%

不好我反對(duì)

(0) 0%

下載地址

基于有限狀態(tài)機(jī)和查找表的RICE解碼結(jié)構(gòu)下載

相關(guān)電子資料下載

- 玩轉(zhuǎn)Spring狀態(tài)機(jī) 609

- 時(shí)序邏輯電路的分類及各種電路特點(diǎn)是什么? 843

- C語(yǔ)言實(shí)現(xiàn)狀態(tài)機(jī)設(shè)計(jì)的技巧與策略 481

- 基于FPGA BRAM的多端口地址查找表與FPGA BRAM的資源分析 742

- 在Verilog中實(shí)現(xiàn)Moore型和Mealy型狀態(tài)機(jī)的方法簡(jiǎn)析 639

- 如何采用“狀態(tài)機(jī)”解析UART數(shù)據(jù)幀 339

- 芯片項(xiàng)目之BUSMATRIX總線矩陣生成工具應(yīng)用 1067

- 以太網(wǎng)自協(xié)商機(jī)制-雙絞線自協(xié)商案例設(shè)計(jì)(二) 692

- DCM模塊喚醒網(wǎng)絡(luò)主動(dòng)與被動(dòng)喚醒機(jī)制探討 334

- 探索LabVIEW編程接口冪等性原理與實(shí)踐 343