一種高速流水線乘法器結構

大小:0.62 MB 人氣: 2018-03-15 需要積分:0

標簽:乘法器(36712)

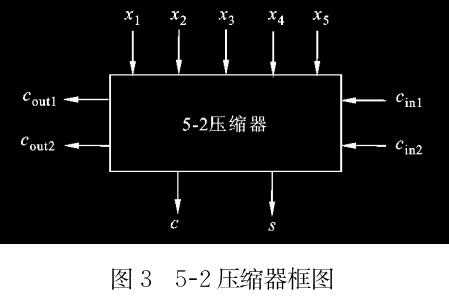

設計了一種新穎的32×32位高速流水線乘法器結構.該結構所采用的新型Radix-16 Booth算法吸取了冗余Booth編碼與改進Booth編碼的優點,能簡單、快速地產生復雜倍數.設計完成的乘法器只產生9個部分積,有效降低了部分積壓縮陣列的規模與延時.通過對5級流水線關鍵路徑中壓縮陣列和64位超前進位(CLA)加法器的優化設計,減少了乘法器的延時和面積.經現場可編程邏輯器件仿真驗證表明,與采用Radix-8 Booth算法的乘法器相比,該乘法器速度提高了11%,硬件資源減少了3%.

非常好我支持^.^

(0) 0%

不好我反對

(0) 0%

下載地址

一種高速流水線乘法器結構下載

相關電子資料下載

- 優秀的Verilog/FPGA開源項目-浮點運算器(FPU)介紹 885

- Alpha半透明圖形疊加算法Matlab+Verilog的設計實現 358

- 一款以32位ARMCortexTM-M0處理器內核為基礎的高性價比安全MCU 350

- 萊迪思在硬件產品層面推出了“Nexus+Avant” 307

- 優化單片機程序代碼的策略與方法 242

- 基于FPGA的高效乘法器 407

- Arm Helium技術誕生的由來 為何不直接采用Neon? 1128

- verilog運算符的優先級 1198

- 如何利用xilinx器件中LUT的結構特征設計乘法器呢? 704

- 布斯算法(Booth Algorithm)乘法器的Verilog實現 1308