EEPROM(Electrically Erasable Programmable read only memory)即電可擦可編程只讀存儲(chǔ)器,是一種掉電后數(shù)據(jù)不丟失(不揮發(fā))存儲(chǔ)芯片。

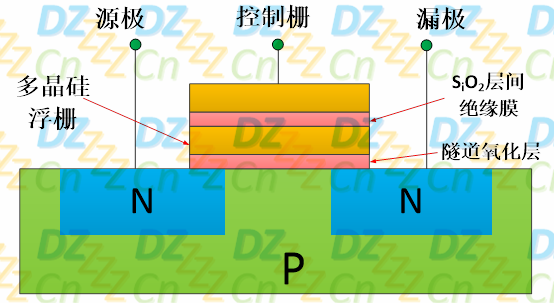

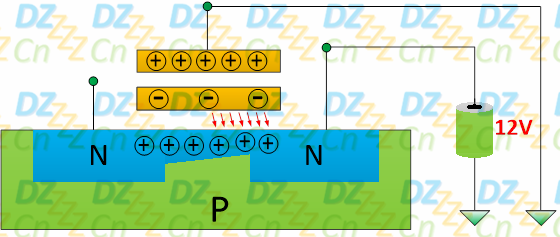

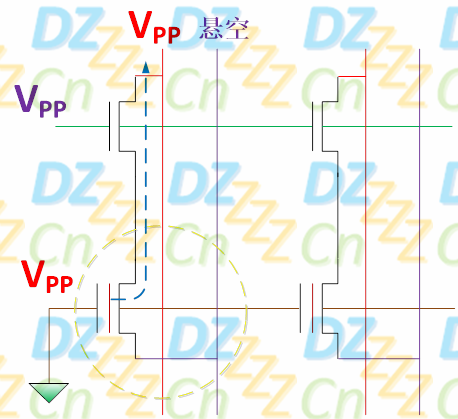

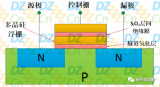

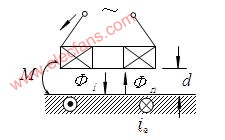

EERPOM的基本結(jié)構(gòu)有幾種,這里講解比較常用的FLOTOX管結(jié)構(gòu),如下圖所示:

FLOTOX(Floating Gate Tunneling Oxide)MOS管即浮柵隧道氧化層晶體管,它是在標(biāo)準(zhǔn)CMOS工藝的基礎(chǔ)上衍生的技術(shù)。

如上圖所示,在傳統(tǒng)的MOS管控制柵下插入一層多晶硅浮柵,浮柵周?chē)难趸瘜优c絕緣層將其與各電極相互隔離,這些氧化物的電阻非常高,而且電子從浮柵的導(dǎo)帶向周?chē)趸飳?dǎo)帶的移動(dòng)需要克服較高的勢(shì)疊,因此,浮柵中的電子泄漏速度很慢,在非熱平衡的亞穩(wěn)態(tài)下可保持?jǐn)?shù)十年。

浮柵延長(zhǎng)區(qū)的下方有個(gè)薄氧區(qū)小窗口,在外加強(qiáng)電場(chǎng)的作用下漏極與浮柵之間可以進(jìn)行雙向電子流動(dòng),繼而達(dá)到對(duì)存儲(chǔ)單元的“擦除”與“寫(xiě)入”操作。

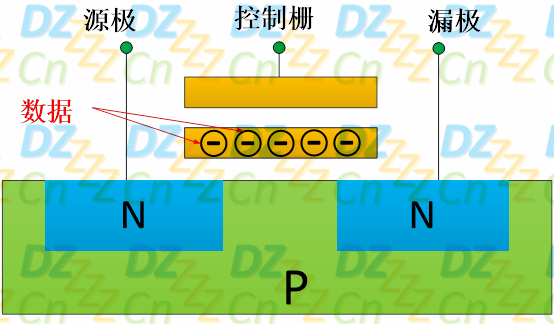

為強(qiáng)調(diào)浮柵周?chē)趸锏慕^緣效果,我們把絕緣層去掉,如下圖所示,其中的“電子”就是我們需要存儲(chǔ)的數(shù)據(jù):

其原理圖符號(hào)如下所示:

我們通常利用F-N隧道效應(yīng)(Fowler-Nordheim tunneling)對(duì)EEPROM存儲(chǔ)單元進(jìn)行“擦除”或“寫(xiě)入”操作,簡(jiǎn)單地說(shuō),即FLOTOX管的控制柵極與漏極在強(qiáng)電場(chǎng)的作用下(正向或負(fù)向),浮柵中的電子獲得足夠的能量后,穿過(guò)二氧化硅層的禁帶到達(dá)導(dǎo)帶,這樣電子可自由向襯底移動(dòng)(具體細(xì)節(jié)可自行參考相關(guān)資料,此處不贅述)。

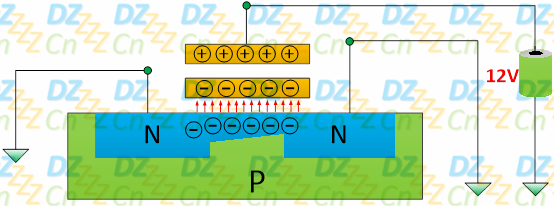

對(duì)EEPROM存儲(chǔ)單元進(jìn)行“擦除”操作,就是將電子注入到浮柵中的過(guò)程(不要將此處的“擦除”操作與FLASH存儲(chǔ)單元中的“擦除”操作弄反了,具體參考FLASH對(duì)應(yīng)文章),如下圖所示:

如上圖所示,將FLOTOX管的源極與漏極接地,而控制柵極接高壓(不小于12V),浮柵與漏極之間形成正向強(qiáng)電場(chǎng),電子從漏極通過(guò)隧道氧化層進(jìn)入浮柵。

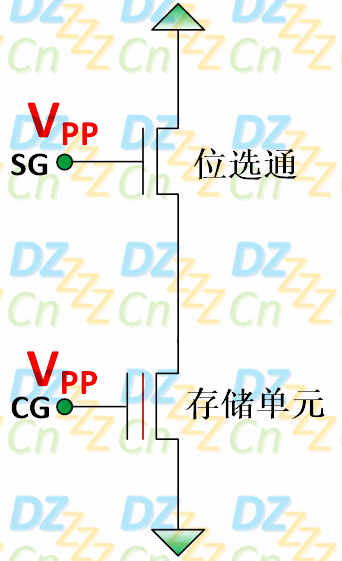

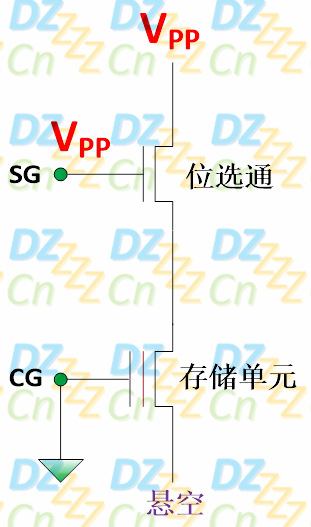

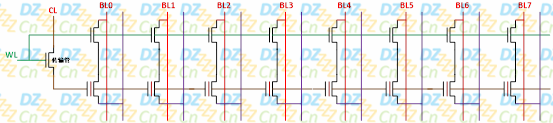

為防止存儲(chǔ)單元“擦除”(或“寫(xiě)入”操作)對(duì)其它單元產(chǎn)生影響,每個(gè)FLOTOX管均與一個(gè)選通管配對(duì)(按照制造工藝可分為N管與P管,這里我們以N管為例進(jìn)行講解,P管是類(lèi)似的),前者就是存儲(chǔ)電子的單元,而后者用來(lái)選擇相應(yīng)的存儲(chǔ)單元的控制位,這種結(jié)構(gòu)導(dǎo)致單位存儲(chǔ)面積比較大,因此,EEPROM存儲(chǔ)芯片的容量通常都不會(huì)很大。

一個(gè)bit位的存儲(chǔ)單元電路狀態(tài)如下圖所示:

其中,SG表示選通管的選通柵(Select Gate),CG表示FLOTOX管的控制柵(Control Gate),VPP表示外接高壓,此處以12V為例

對(duì)EEPROM存儲(chǔ)單元進(jìn)行“寫(xiě)入”操作,就是將浮柵中電子釋放的過(guò)程(不要把“寫(xiě)入”與“擦除”操作弄反了),如下圖所示:

如上圖所示,將FLOTOX管的源極懸空,漏極接高壓(不小于12V),而控制柵極接地,則浮柵與漏極之間形成負(fù)向強(qiáng)電場(chǎng),電子從浮柵通過(guò)隧道氧化層回到漏極放電。

配合對(duì)應(yīng)的選通管,則一個(gè)bit位的存儲(chǔ)單元電路狀態(tài)如下圖所示:

?

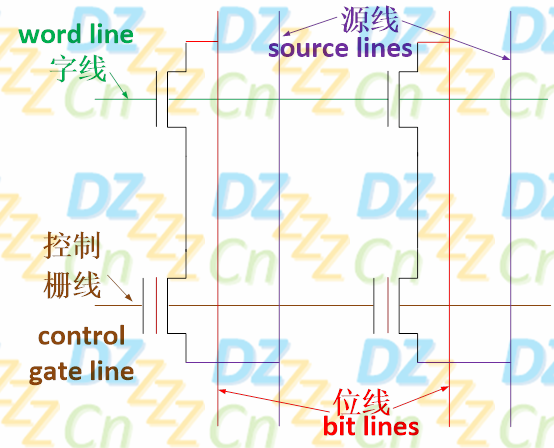

多個(gè)bit位組成的存儲(chǔ)單元陣列如下圖所示:

當(dāng)進(jìn)行存儲(chǔ)單元的“擦除”操作時(shí),源線(Sources Lines,SL)與位線(Bit Lines,BL)均為低電平,而控制柵線(CL)為高電平(不小于12V),當(dāng)對(duì)應(yīng)存儲(chǔ)單元的選通管打開(kāi)時(shí)(Word Line,WL=VPP),如下圖所示:

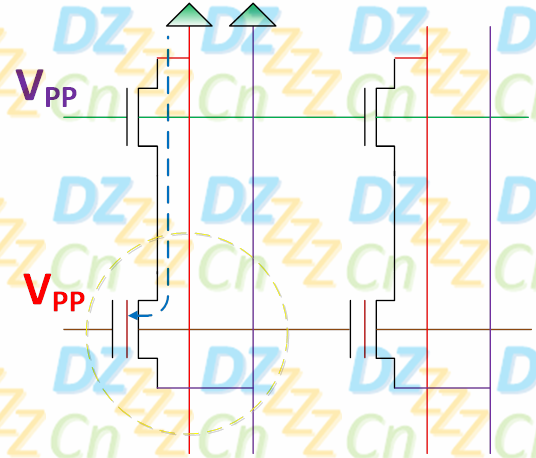

當(dāng)進(jìn)行存儲(chǔ)單元的“寫(xiě)”操作時(shí),位線為高電平(不小于12V),而源線懸空且比Program Gate Line為低電平,當(dāng)對(duì)應(yīng)存儲(chǔ)單元的選通管打開(kāi)時(shí)(SG=VPP),如下圖所示:

每8個(gè)存儲(chǔ)單元配置一個(gè)高壓傳輸管,則一個(gè)字節(jié)的存儲(chǔ)陣列如下圖所示:

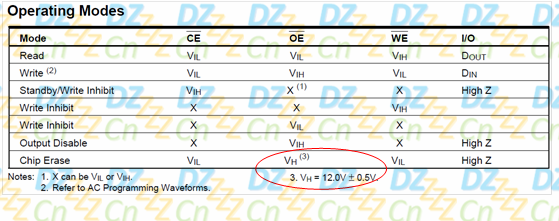

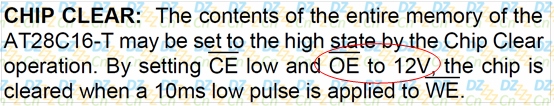

很明顯,EEPROM的“擦除”與“寫(xiě)入”操作均需要高壓(強(qiáng)電場(chǎng))進(jìn)行浮柵電子的注入或釋放,而一般的EEPROM芯片為5V供電,那么這些高壓從何而來(lái)?對(duì)于并行EEPROM芯片,有專(zhuān)用的引腳可作為擦除功能的高壓供電端,下圖來(lái)自ATMEL并行EEPROM型號(hào)AT28C16數(shù)據(jù)手冊(cè):

可以看到,在進(jìn)行“擦除”操作時(shí),需要在OE(Output Enable)引腳接入12V的高壓。

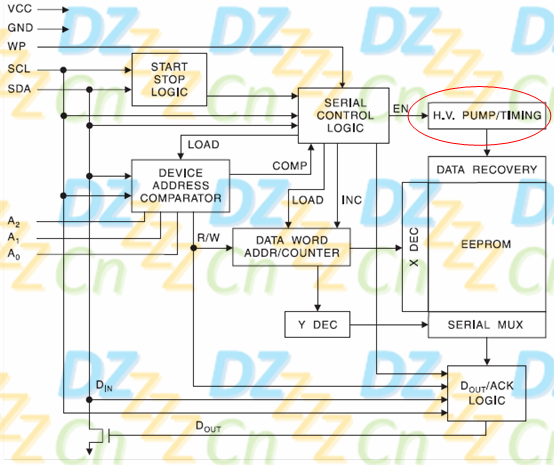

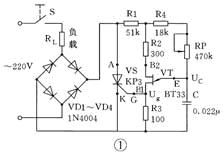

但是串行EEPROM就沒(méi)這么幸運(yùn)了,比如我們最常用的AT24CXX系列EEPROM芯片,通常是3.3V或5V供電的,而且對(duì)外的接口通常是I2C串行總線那樣的兩根線,那高壓從何而來(lái)?有人想到了升壓電路,沒(méi)錯(cuò),下圖來(lái)自ATMEL串行EEPROM型號(hào)AT24C02數(shù)據(jù)手冊(cè):

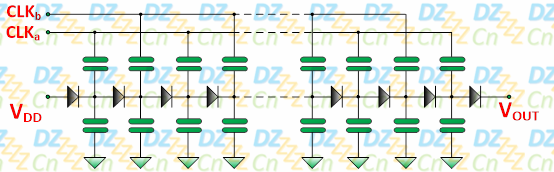

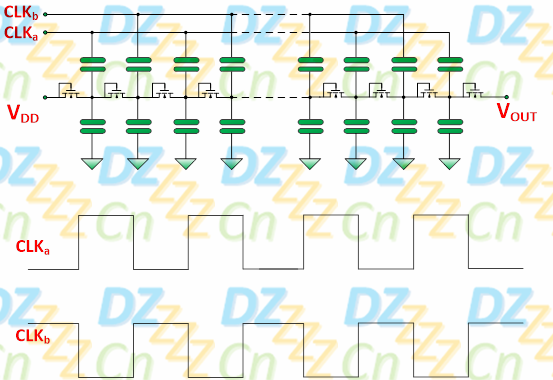

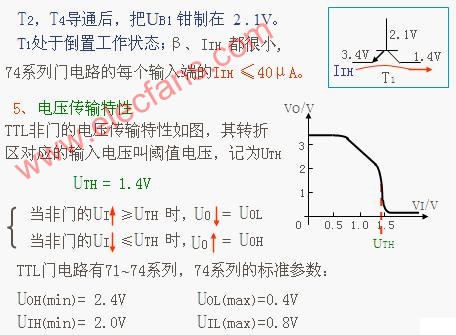

其中,H.V. PUMP(High Voltage Pump)就是高壓泵(升壓)電路,升壓電路有很多種,比如整流倍壓、變壓器升壓、BOOST升壓、電荷泵等,但是,在集成電路設(shè)計(jì)中無(wú)法做成大容量電容與電感,因此,只有電荷泵電路比較適合片內(nèi)升壓,它的基本電路如下圖所示:

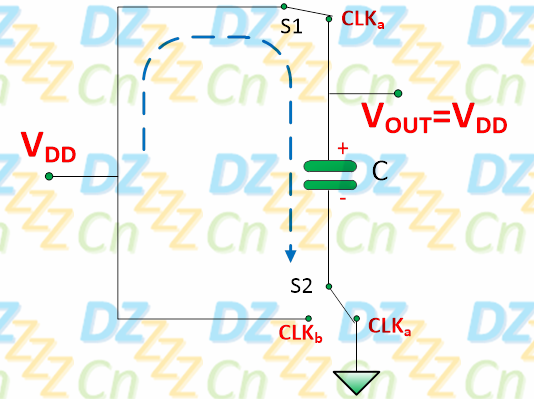

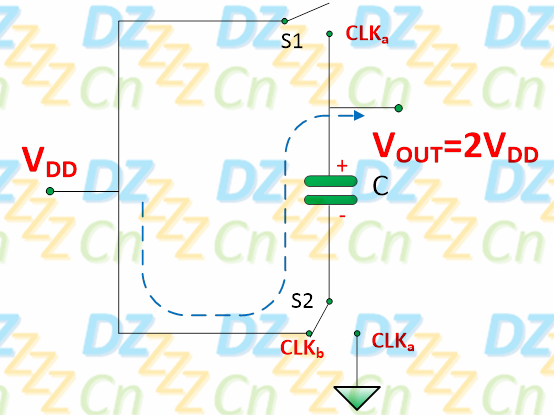

我們分析其中一級(jí)就明白其升壓原理了,如下圖所示(原理與“整流倍壓電路”類(lèi)似,可參考《整流電路》文章):

在時(shí)鐘周期CLKa期間,開(kāi)關(guān)S1閉合,S2與地相連接,此時(shí)電容充電至VDD。

在時(shí)鐘周期CLKb期間,開(kāi)關(guān)S1打開(kāi),S2與電源VDD連接,此時(shí)電源VDD與電容C的電壓串聯(lián)起來(lái)對(duì)外供電,此時(shí)VOUT=為時(shí)源VDD的兩倍,即2×VDD。

在集成電路設(shè)計(jì)中,可以使用NMOS或PMOS實(shí)現(xiàn)開(kāi)關(guān)功能,電容則可使用MOS電容(即柵極作為一個(gè)極,而源極與漏極連接作為另一個(gè)極板),而二極管則用MOS管代替,如下圖所示:

實(shí)際的電荷泵電路有很多種結(jié)構(gòu),如多相時(shí)鐘電荷泵、CTS電荷泵、柵交叉耦合襯底偏置電荷泵等等,讀者可自行參考相關(guān)文檔,此處不再贅述。

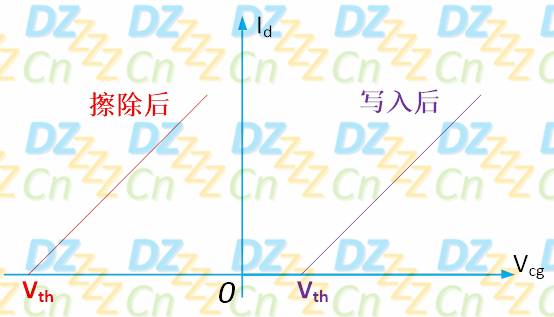

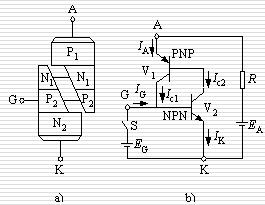

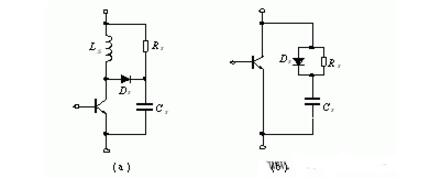

那怎么樣實(shí)現(xiàn)數(shù)據(jù)的“讀取”操作呢?當(dāng)浮柵中注入(充電狀態(tài))或釋放電子(放電狀態(tài))時(shí),存儲(chǔ)單元的閥值電壓會(huì)發(fā)生改變,如下圖所示:

在讀取存儲(chǔ)單元時(shí),我們可以在控制柵上加一個(gè)中間電平,其值介于兩個(gè)閥值Vth之間,這樣浮柵有電子的高開(kāi)啟管不能導(dǎo)通,而浮柵放電后的低開(kāi)啟管能正常導(dǎo)通,由此分辨出單元存儲(chǔ)的數(shù)據(jù)是“1”還是“0”。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論