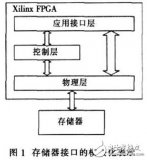

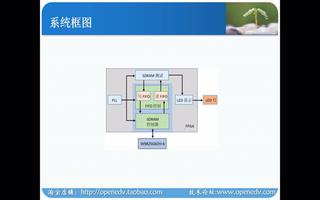

1. 背景 這篇文章主要介紹了DDR3IP核的寫實(shí)現(xiàn)。 2. 寫命令和數(shù)據(jù)總線介紹 DDR3 SDRAM控制器IP核主要預(yù)留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 5068

5068

2、512Mb-2Gb LP DDR2,以及?LP DDR4x、LP DDR3、LP DDR、SDRAM,適用于需配備4Gb 或以下容量DRAM 的應(yīng)用,?如人工智能加速器、物聯(lián)網(wǎng)、汽車、工業(yè)用、電信、

2022-04-20 16:04:03 2554

2554

DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數(shù)據(jù)率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器)通常被我們稱為DDR,其中的“同步

2023-03-07 11:29:43 3208

3208

DDR SDRAM參考設(shè)計(jì)VHDL版(有詳細(xì)的文檔,仿真綜合文件)File/Directory Description

2012-08-11 09:33:30

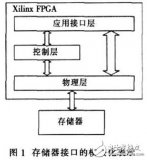

引言 很多嵌入式系統(tǒng),特別是應(yīng)用于圖像處理與高速數(shù)據(jù)采集等場(chǎng)合的嵌入式系統(tǒng),都需要高速緩存大量的數(shù)據(jù)。DDR(Double DataRate,雙數(shù)據(jù)速率)SDRAM由于其速度快、容量大,而且價(jià)格便宜

2018-12-18 10:17:15

DDR SDRAM內(nèi)存發(fā)展歷程

2021-01-06 06:04:22

DDR SDRAM訪問特性DDR控制器效率對(duì)比

2021-02-04 07:14:23

我手上有一張DDR200T的開發(fā)板,板載了一塊512M的SDRAM內(nèi)存,板子燒了一個(gè)UX600的demosoc,我是要在這個(gè)板子跑RT-Thread。

要是想使用這塊SDRAM應(yīng)該怎么做呢?應(yīng)該

2023-08-11 08:05:46

DDR4 SDRAM的尋址方式有哪些?

2021-10-27 06:50:24

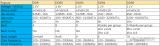

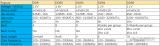

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

DDR_SDRAM控制器的VHDL代碼已經(jīng)測(cè)試

2016-08-24 16:49:35

使用公式分析和理論分析兩種方法,以實(shí)例證明公式的局限性和兩種方法的利弊。本文最后還基于這些實(shí)例分析,給出了SDRAM和DDR SDRAM等布線的一般性原則。

2021-05-19 06:52:58

SDRAM和DDR布線技巧ecos應(yīng)用是與硬件平臺(tái)無關(guān)的,雖然開發(fā)板沒有涉及到SDRAM和DDR,不過,在某些高端平臺(tái)上使用ecos可能會(huì)遇到內(nèi)存布線問題,為了完整敘述,這里一并給出說明。&

2010-03-18 15:33:07

SDRAM和DDR的具體區(qū)別是什么?

2021-06-18 07:58:51

;如果上一次執(zhí)行了寫操作,則此次執(zhí)行讀操作。如果不是同時(shí)出現(xiàn)讀寫請(qǐng)求,則是什么請(qǐng)求就執(zhí)行什么操作。2)采用全頁(yè)模式的讀寫操作,該模式在讀、寫完成時(shí),需要給出預(yù)充電命令才能結(jié)束。3)刷新請(qǐng)求始終優(yōu)于讀、寫請(qǐng)求。DDR的時(shí)序與SDRAM是相似的,學(xué)好SDRAM后,理解DDR2和DDR3就非常容易了。

2017-11-23 11:02:27

本篇文章英尚微電子存儲(chǔ)芯片供應(yīng)商主要詳細(xì)介紹下ARM里的ram和SDRAM有什么區(qū)別,首先介紹了ram及SDRAM做了詳細(xì)闡述,最后介紹了兩者的區(qū)別。

2021-04-02 06:46:51

SDRAM SLICE CARD

2023-03-30 12:05:53

XILINX 關(guān)于FPGA 對(duì)DDR SDRAM 的設(shè)計(jì)文檔

2012-08-17 09:20:26

在電腦上拆到2條rdram內(nèi)存條,這個(gè)和sdram內(nèi)存條有什么區(qū)別,可以兼容嗎

2023-10-08 09:01:45

嗨!我正在尋找Spartan-3A / 3ANFPGA入門KitBoard用戶指南(UG334)。具體來說第13章:DDR2 SDRAM和我不明白如何使用DDR2 SDRAM,因?yàn)槔邕@個(gè)內(nèi)存

2019-07-31 06:18:10

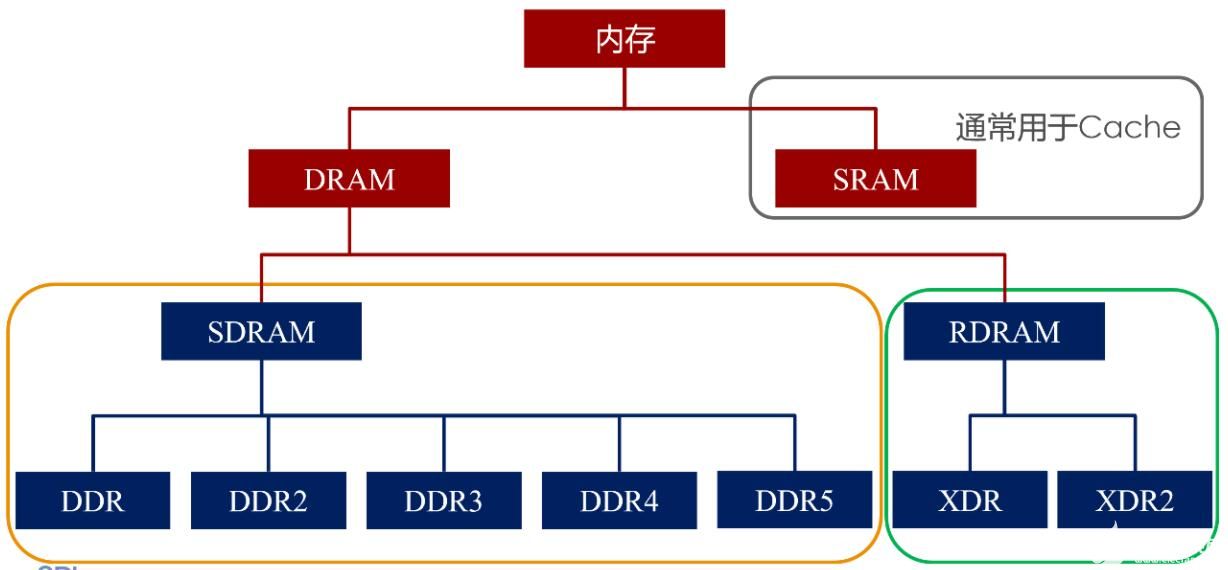

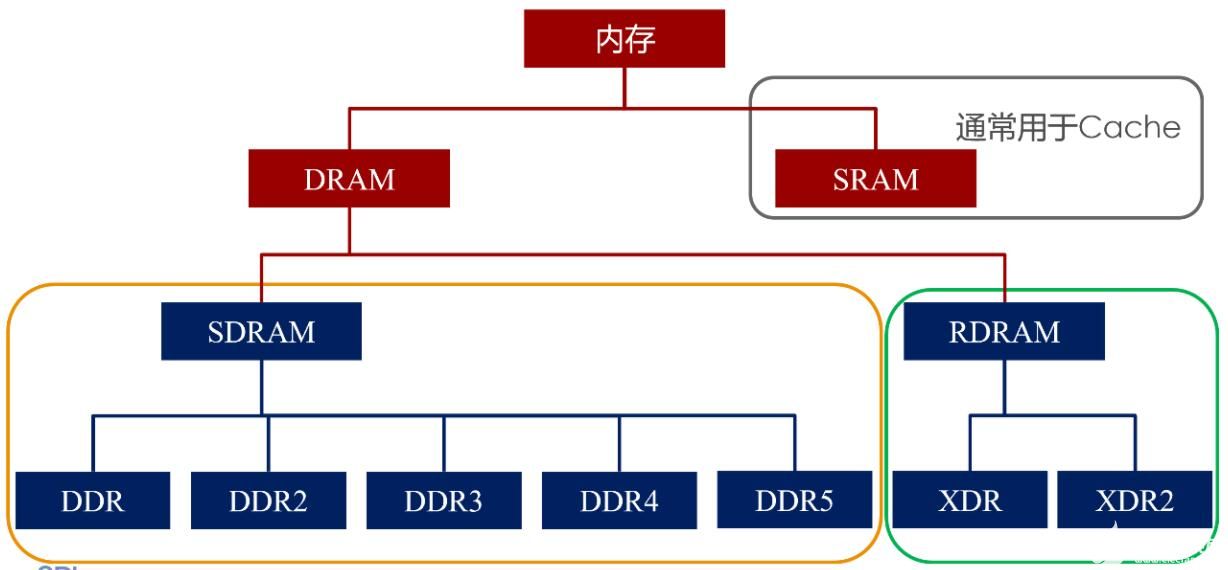

本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2021-04-20 06:30:52

/DDR/DDR2芯片的datasheet細(xì)細(xì)比對(duì),也許用這篇文比較也無法完全說明白他們的迥異,但是至少特權(quán)同學(xué)希望通過這篇文章能夠讓大家對(duì)他們之間的區(qū)別有一個(gè)大概的認(rèn)識(shí),尤其一樣對(duì)SDR SDRAM

2014-12-30 15:22:49

DDR SDRAM在嵌入式系統(tǒng)中有哪些應(yīng)用?DDR SDRAM的工作方式有哪幾種?怎樣去設(shè)計(jì)DDR SDRAM控制器?

2021-04-30 07:04:04

,F-RAM,MRAM(非易失性存儲(chǔ)器)256Kbit-16Mbit8.Mobile SDRAM/DDR(低功耗SDRAM/DDR)128Mbit-512Mbit9.DDR2/DDR3 SDRAM (動(dòng)態(tài)隨機(jī)

2013-08-30 10:31:33

DDR SDRAM is a 2n prefetch architecture with two data transfers perclock cycle. In the 2n prefetch

2009-03-28 14:43:47 56

56 files *top.v* is the source file for DDR SDRAM controller

2009-05-14 10:46:50 37

37 ref ddr sdram verilog源代碼

File/Directory Description

2009-06-14 08:48:01 82

82 =============================================doc DDR SDRAM reference design documentationmodel Contains the vhdl SDRAM model

2009-06-14 08:49:23 51

51 DDR2 SDRAM控制器的設(shè)計(jì)與實(shí)現(xiàn)

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設(shè)計(jì)方法!詳述了其基本結(jié)構(gòu)和設(shè)計(jì)思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

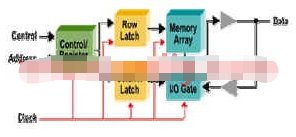

64 SDRAM的原理和時(shí)序

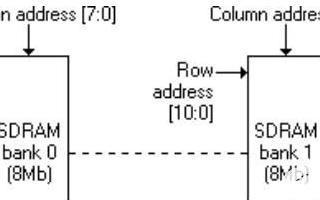

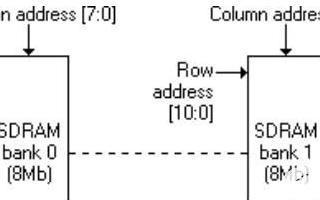

SDRAM內(nèi)存模組與基本結(jié)構(gòu) 我們平時(shí)看到的SDRAM都是以模組形式出現(xiàn),為什么要做成這種形式呢?這首先要接觸到兩個(gè)概念:物理Bank與芯片位寬

2010-03-11 14:43:26 167

167 SDRAM與DDR布線指南:ecos應(yīng)用是與硬件平臺(tái)無關(guān)的,雖然開發(fā)板沒有涉及到SDRAM和DDR,不過,在某些高端平臺(tái)上使用ecos可能會(huì)遇到內(nèi)存布線問題,為了完整敘述,這里一并給出說明。 很

2010-03-18 15:29:08 0

0 SDRAM設(shè)計(jì)詳細(xì)說明

完成SDRAM的上層驅(qū)動(dòng)設(shè)計(jì),對(duì)SDRAM讀寫、管理無誤,與其他模塊的接口正確。

口令:MMCTEAM

SDRAM的工作原理

2010-04-22 14:02:57 0

0 嵌入式測(cè)試和測(cè)量挑戰(zhàn)目錄引言3-4DRAM發(fā)展趨勢(shì) 3DRAM4-6SDRAM 6-9DDR SDRAM6DDR2 SDRAM 7DDR3 SDRAM 8DDR4 SDRAM 9GDDR 和LPDDR 9DIMMs 9-13DIMM 物理尺寸 9DIMM

2010-06-30 09:28:08 94

94 本文介紹了DDR3 SDRAM 的基本特點(diǎn)和主要操作時(shí)序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設(shè)計(jì)方法。詳述了控制器基本結(jié)構(gòu)和設(shè)計(jì)思想,分析了各模塊功能與設(shè)計(jì)注意事項(xiàng),并

2010-07-30 17:13:55 30

30 DDR2 SDRAM 和 FB-DIMM的電氣檢驗(yàn):

隨著DDR2 SDRAM時(shí)鐘頻率和信號(hào)邊沿速率不斷提高,檢查電路板結(jié)構(gòu)、電氣系統(tǒng)和信令正變得越來越重要。本應(yīng)用指南介紹了電路板、電源系統(tǒng)、

2010-08-06 08:29:01 39

39 不只計(jì)算機(jī)存儲(chǔ)器系統(tǒng)一直需要更大、更快、功率更低、物理尺寸更小的存儲(chǔ)器,嵌入式系統(tǒng)應(yīng)用也有類似的要求。本應(yīng)用指南介紹了邏輯分析儀在檢驗(yàn)DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 本文將介紹DDR SDRAM的一些概念和難點(diǎn),主要結(jié)合上一篇SDRAM的介紹加以對(duì)比。同時(shí)著重講解主流DDRII的技術(shù)。最后結(jié)合硬件設(shè)計(jì)提出一些參考。

DDR SDRAM全稱為Double Dat

2010-08-30 16:26:16 119

119 什么是DDR SDRAM內(nèi)存

DDR是一種繼SDRAM后產(chǎn)生的內(nèi)存技術(shù),DDR,英文原意為“DoubleDataRate”,顧名思義,就是雙數(shù)據(jù)傳輸模式。之所以稱其為“雙”,也

2009-12-17 11:15:53 1646

1646 什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設(shè)備工程聯(lián)合委員會(huì))進(jìn)行開發(fā)的新生代內(nèi)存技

2009-12-17 11:17:59 623

623 SDRAM內(nèi)存 SDRAM是Synchronous Dynamic Random Access Memor

2009-12-17 16:15:28 636

636 DDR SDRAM內(nèi)存

DDR SDRAM是Double Dat

2009-12-17 16:20:33 684

684 文中在介紹DDR2的工作原理的基礎(chǔ)上,給出了一個(gè)用VHDL語言設(shè)計(jì)的DDR2 SDRAM控制器的方法,并且提出了一種在高速圖像處理系統(tǒng)中DDR2 SDRAM的應(yīng)用方案,同時(shí)在Virtex-5系列的FPGA上得到了實(shí)現(xiàn)

2011-07-23 10:03:16 5102

5102 定義了時(shí)鐘單位階躍信號(hào)C(n) 提出了一種利用帶相對(duì)時(shí)鐘坐標(biāo)的邏輯方程表示邏輯信號(hào)的方法通過對(duì)所設(shè)計(jì)的DDR SDRAM控制器的讀寫時(shí)序的分析建立了控制器主要信號(hào)的時(shí)序表達(dá)式并利用

2011-09-26 15:34:12 39

39 雖然目前SDRAM內(nèi)存條價(jià)格已經(jīng)接底線,內(nèi)存開始向DDR和Rambus內(nèi)存過渡。但是由于DDR內(nèi)存是在SDRAM基礎(chǔ)上發(fā)展起來的,所以詳細(xì)了解SDRAM內(nèi)存的接口和主板設(shè)計(jì)方法對(duì)于設(shè)計(jì)基于DDR內(nèi)存的主

2012-01-05 16:21:11 247

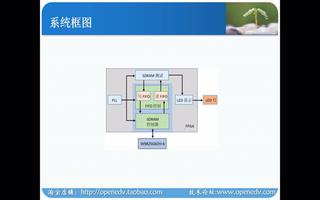

247 使用功能強(qiáng)大的FPGA來實(shí)現(xiàn)一種DDR2 SDRAM存儲(chǔ)器的用戶接口。該用戶接口是基于XILINX公司出產(chǎn)的DDR2 SDRAM的存儲(chǔ)控制器,由于該公司出產(chǎn)的這種存儲(chǔ)控制器具有很高的效率,使用也很廣泛,

2013-01-08 18:15:50 237

237 DDR SDRAM 全稱為Double Data Rate SDRAM,中文名為雙倍數(shù)據(jù)流SDRAM。DDRSDRAM 在原有的SDRAM 的基礎(chǔ)上改進(jìn)而來。也正因?yàn)槿绱耍?b class="flag-6" style="color: red">DDR 能夠憑借著轉(zhuǎn)產(chǎn)成本優(yōu)勢(shì)來打敗昔日的對(duì)手RDRAM,成為當(dāng)今的主流

2013-09-13 15:17:30 210

210 ddr2_sdram 操作時(shí)序,非常好的教程,可以充分了解DDR2

2015-10-28 11:07:39 19

19 DDR_SDRAM介紹和時(shí)序圖,DDR_SDRAM介紹和時(shí)序圖

2016-02-23 11:58:38 6

6 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設(shè)計(jì)VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 38

38 一種面向多核系統(tǒng)的DDR2SDRAM控制單元_章裕

2017-01-03 18:00:37 5

5 作者:Steve Leibson, 賽靈思戰(zhàn)略營(yíng)銷與業(yè)務(wù)規(guī)劃總監(jiān) Adrian Cosoroaba和Terry Magee在本月MemCon上給出了關(guān)于DDR4 SDRAM接口的詳細(xì)展示,該演示

2017-02-08 14:03:01 608

608 DDR2SDRAM控制器在機(jī)載顯控系統(tǒng)中的應(yīng)用_孫少偉

2017-03-19 11:26:54 1

1 DDR2_DDR3_SDRAM,PCB布線規(guī)則指導(dǎo)

2017-10-31 10:06:48 78

78 SRAM是靠雙穩(wěn)態(tài)觸發(fā)器來記憶信息的;SDRAM是靠MOS電路中的柵極電容來記憶信息的。由于電容上的電荷會(huì)泄漏,需要定時(shí)給與補(bǔ)充,所以動(dòng)態(tài)RAM需要設(shè)置刷新電路。但動(dòng)態(tài)RAM比靜態(tài)RAM集成度

2017-11-03 18:26:43 5231

5231 DDR3 SDRAM(Double Data Rate Three SDRAM):為雙信道三次同步動(dòng)態(tài)隨機(jī)存取內(nèi)存。

DDR4 SDRAM(Double Data Rate Fourth

2017-11-17 13:15:49 25152

25152 在高速信號(hào)處理系統(tǒng)中, 需要緩存高速、大量的數(shù)據(jù), 存儲(chǔ)器的選擇與應(yīng)用已成為系統(tǒng)實(shí)現(xiàn)的關(guān)鍵所在。DDR SDRAM是一種高速CMOS、動(dòng)態(tài)隨機(jī)訪問存儲(chǔ)器, 它采用雙倍數(shù)據(jù)速率結(jié)構(gòu)來完成高速操作

2018-07-20 18:38:00 12744

12744

DRAM (動(dòng)態(tài)隨機(jī)訪問存儲(chǔ)器)對(duì)設(shè)計(jì)人員特別具有吸引力,因?yàn)樗峁┝藦V泛的性能,用于各種計(jì)算機(jī)和嵌入式系統(tǒng)的存儲(chǔ)系統(tǒng)設(shè)計(jì)中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 91644

91644 DDR SDRAM全稱為Double Data Rate SDRAM,中文名為雙倍數(shù)據(jù)流SDRAM。DDR SDRAM在原有的SDRAM的基礎(chǔ)上改進(jìn)而來。也正因?yàn)槿绱耍?b class="flag-6" style="color: red">DDR能夠憑借著轉(zhuǎn)產(chǎn)成本優(yōu)勢(shì)

2018-03-16 14:24:01 32

32 本文主要介紹的是ARM里的RAM和SDRAM有什么區(qū)別,首先介紹了RAM的類別及特點(diǎn),其次對(duì)SDRAM做了詳細(xì)闡述,最后介紹了RAM和SDRAM的區(qū)別是什么。

2018-04-27 16:20:52 34171

34171 實(shí)現(xiàn)數(shù)據(jù)的高速大容量存儲(chǔ)是數(shù)據(jù)采集系統(tǒng)中的一項(xiàng)關(guān)鍵技術(shù)。本設(shè)計(jì)采用Altera 公司Cyclone系列的FPGA 完成了對(duì)DDR SDRAM 的控制,以狀態(tài)機(jī)來描述對(duì)DDR SDRAM 的各種時(shí)序

2019-08-14 08:00:00 3401

3401

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA讀寫SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文主要包括了:FPGA讀寫SDRAM的實(shí)例,SDRAM控制器核心介紹,系列SDRAM數(shù)據(jù)手冊(cè)

2018-12-25 08:00:00 56

56 的。 SDRAM,同步的DRAM,即數(shù)據(jù)的讀寫需要時(shí)鐘來同步。 DRAM和SDRAM由于實(shí)現(xiàn)工藝問題,容量較SRAM大。但是讀寫速度不如SRAM,但是現(xiàn)在,SDRAM的速度也已經(jīng)很快了,時(shí)鐘好像已經(jīng)有150兆的了。那么就是讀寫周期小于10ns了。SDRAM雖然工作頻率高,但是實(shí)際吞吐率要打折扣。

2019-04-01 16:24:29 35283

35283 SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代,DDR4 SDRAM。

2019-09-12 07:02:00 2009

2009

SDRAM在計(jì)算機(jī)中被廣泛使用,從起初的SDRAM到之后一代的DDR(或稱DDR1),然后是DDR2和DDR3進(jìn)入大眾市場(chǎng),2015年開始DDR4進(jìn)入消費(fèi)市場(chǎng)。

2019-09-11 07:09:00 2239

2239

DDR2 設(shè)備概述:DDR2 SDRAM接口是源同步、支持雙速率傳輸。比如DDR SDRAM ,使用SSTL 1.8V/IO電氣標(biāo)準(zhǔn),該電氣標(biāo)準(zhǔn)具有較低的功耗。與TSOP比起來,DDR2 SDRAM的FBGA封裝尺寸小得多。

2019-06-22 10:05:01 1793

1793

本文件定義了DDR3 SDRAM規(guī)范,包括特性、功能、交直流特性、封裝和球/信號(hào)分配。本文檔的目的是為符合jedec的512 MB到8 GB的x4、x8和x16 ddr3 sdram設(shè)備定義一組最低

2019-11-04 08:00:00 73

73 H57V1262GTR SDRAM模塊B型

SDRAM外擴(kuò)存儲(chǔ) 8Mx16bit

型號(hào) SDRAM Board (B)

2019-12-30 09:01:47 1197

1197

學(xué)完SDRAM控制器后,可以感受到SDRAM的控制器的書寫是十分麻煩的,因此在xilinx一些FPGA芯片內(nèi)已經(jīng)集成了相應(yīng)的IP核來控制這些SDRAM,所以熟悉此類IP核的調(diào)取和使用是非常必要的。下面我們以A7的DDR3 IP核作為例子進(jìn)行IP核調(diào)取。

2019-11-10 10:28:45 4702

4702

DDR5 是第五代 DDR SDRAM 的簡(jiǎn)稱,DDR SDRAM 是英文 Double Data Rate SDRAM 的縮寫,中文譯為雙倍速率 SDRAM,而 SDRAM 又是

2020-02-03 18:30:59 5442

5442 SDRAM從發(fā)展到現(xiàn)在已經(jīng)經(jīng)歷了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM。第一代SDRAM

2020-04-03 16:04:01 1489

1489 DDR2 SDRAM采用雙數(shù)據(jù)速率結(jié)構(gòu)實(shí)現(xiàn)高速運(yùn)行。雙數(shù)據(jù)速率體系結(jié)構(gòu)本質(zhì)上是4n預(yù)取體系結(jié)構(gòu),其接口設(shè)計(jì)為在I/O球處每個(gè)時(shí)鐘周期傳輸兩個(gè)數(shù)據(jù)字。DDR2 SDRAM的單次讀寫操作有效地包括在內(nèi)部

2020-05-21 08:00:00 1

1 接口的異步DRAM相比,可以有一個(gè)更復(fù)雜的操作模式。下面宇芯電子介紹關(guān)于靜態(tài)SDRAM和動(dòng)態(tài)SDRAM的區(qū)別。 靜態(tài)記憶 假設(shè)我們要將16Mb存儲(chǔ)器連接到FPGA。 16Mb表示內(nèi)存可容納1600萬位(準(zhǔn)確地說是16777216位)。現(xiàn)在,很少對(duì)比特進(jìn)行單獨(dú)尋址,而是通常以8或16的數(shù)據(jù)包(

2020-06-24 12:01:55 733

733

DDR SDRAM是具有雙倍數(shù)據(jù)傳輸率的SDRAM,其數(shù)據(jù)傳輸速度為系統(tǒng)時(shí)鐘頻率的兩倍,由于速度增加,其傳輸性能優(yōu)于傳統(tǒng)的SDRAM。DDR SDRAM 在系統(tǒng)時(shí)鐘的上升沿和下降沿都可以進(jìn)行

2020-07-16 15:44:10 1938

1938 SDRAM從發(fā)展至今歷經(jīng)了五代,分別是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,第五代DDR4 SDRAM,SDRAM有一個(gè)同步

2020-07-24 14:25:27 719

719 DDR SDRAM的原理及特點(diǎn):DDR SDRAM不需要提高時(shí)鐘頻率就能加倍提高SDRAM的速度,因?yàn)樗试S在時(shí)鐘脈沖的上升沿和下降沿讀寫數(shù)據(jù)。至于地址和控制信號(hào),還是跟傳統(tǒng)的SDRAM一樣,在時(shí)鐘的上升沿進(jìn)行傳輸。

2020-08-10 17:33:21 603

603

SDRAM從SDR到DDR再到DDR2一路走來,又都產(chǎn)生了什么樣的變化,又都在哪些方面進(jìn)行了改進(jìn),帶來了速度性能的進(jìn)一步提升呢?

2020-09-26 11:47:34 10668

10668 。SDRAM可稱為SDRSDRAM。 DDR其實(shí)指的是DDRSDRAM,SDRAM及DDR主要差異有三點(diǎn)整理如下: SDRAM與DDR的主要差異

2021-02-22 15:35:48 3111

3111

本文首先分析了DDR SDRAM的基本特征,并提出了相應(yīng)的解決方案詳細(xì)介紹了基于J EDEC DDR SDRAM規(guī)范的DDR SDRAM控制器設(shè)計(jì)方案。該控制器采用Verilog HDL硬件描述語言實(shí)現(xiàn),并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)簡(jiǎn)介(arm嵌入式開發(fā)平臺(tái)PB)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)簡(jiǎn)介資料,講解的還不錯(cuò),感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)(嵌入式開發(fā)式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設(shè)計(jì)及實(shí)現(xiàn)總結(jié)文檔,是一份很不錯(cuò)的參考資料,具有較高參考價(jià)值,感興趣的可以下載看看………………

2021-07-30 13:07:09 35

35 SDRAM有一個(gè)同步接口,在響應(yīng)控制輸入前會(huì)等待一個(gè)時(shí)鐘信號(hào),這樣就能和計(jì)算機(jī)的系統(tǒng)總線同步。時(shí)鐘被用來驅(qū)動(dòng)一個(gè)有限狀態(tài)機(jī),對(duì)進(jìn)入的...

2022-01-26 19:40:35 1

1 APM32E103VET6S_SDRAM模塊_SDRAM與IO口沖突問題

2022-11-09 21:03:42 0

0 8Gb DDR4 SDRAM B裸片組織為128Mbit x 4 I/O x16banks或64Mbit x8 I/O x 16banks設(shè)備。此同步設(shè)備實(shí)現(xiàn)高達(dá)2666Mb/sec的高速雙數(shù)

2022-12-05 11:54:24 11

11 DDR3

SDRAM使用雙倍數(shù)據(jù)速率架構(gòu)來實(shí)現(xiàn)高速操作。雙倍數(shù)據(jù)速率結(jié)構(gòu)是一種8n預(yù)取架構(gòu),其接口經(jīng)過設(shè)計(jì),可在I/O引腳上每個(gè)時(shí)鐘周期傳輸兩個(gè)數(shù)據(jù)字。

DDR3

SDRAM的單個(gè)讀或?qū)懖僮饔行У匕?/div>

2023-02-06 10:12:00 3

3 DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory,雙數(shù)據(jù)率同步動(dòng)態(tài)隨機(jī)存儲(chǔ)器)通常被我們稱為DDR

2023-03-07 11:33:57 1653

1653 SDRAM有多種標(biāo)準(zhǔn),包括DDR(Double Data Rate)、DDR2、DDR3和DDR4。每個(gè)標(biāo)準(zhǔn)都具有不同的物理規(guī)格和數(shù)據(jù)傳輸速率。DDR4是現(xiàn)代計(jì)算機(jī)中使用的最新型號(hào),它具有更高的頻率和更大的容量。

2023-08-26 11:57:42 2054

2054 電子發(fā)燒友網(wǎng)站提供《PIC32系列參考手冊(cè)之DDR SDRAM控制器.pdf》資料免費(fèi)下載

2023-09-25 11:39:59 0

0 SDRAM與DDR布線指南

2022-12-30 09:20:50 10

10 JESD79-5B DDR5 SDRAM-2022 JEDEC

2023-12-25 09:51:55 2

2 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論