設(shè)計驗(yàn)證是芯片產(chǎn)業(yè)鏈中關(guān)系到芯片質(zhì)量的重要環(huán)節(jié),隨著芯片規(guī)模擴(kuò)大及片上系統(tǒng)(SoC)設(shè)計復(fù)雜度提升,驗(yàn)證目標(biāo)從功能正確、性能達(dá)標(biāo)向滿足業(yè)務(wù)應(yīng)用快速適配部署的需求發(fā)展,其難度和重要性不斷提高。

閃存主控驗(yàn)證由于其業(yè)務(wù)應(yīng)用的特點(diǎn),需要關(guān)注前端接口協(xié)議處理、后端閃存吞吐以及針對不同業(yè)務(wù)讀寫均衡和異常處理的需求。其導(dǎo)向隨著“軟件定義存儲”的發(fā)展,更加強(qiáng)調(diào)與業(yè)務(wù)系統(tǒng)實(shí)際應(yīng)用中的配合;其復(fù)雜程度也隨芯片計算存儲融合的發(fā)展而不斷提高。為了在有限的市場窗口周期內(nèi)快速迭代,縮短整體芯片及業(yè)務(wù)方案的研發(fā)周期,需要綜合應(yīng)用各類驗(yàn)證技術(shù)和工具來有效提高閃存主控的開發(fā)效率和質(zhì)量。以下是對閃存主控驗(yàn)證工作的業(yè)務(wù)梳理、目標(biāo)概述和全流程的簡要介紹。

1.閃存主控驗(yàn)證業(yè)務(wù)分析

1.1 特點(diǎn):系統(tǒng)構(gòu)成復(fù)雜。

閃存主控和網(wǎng)絡(luò)通信、圖像處理等芯片不同,它不是單純的輸入輸出數(shù)據(jù)流業(yè)務(wù)處理的模型。其系統(tǒng)由定制算法、數(shù)據(jù)調(diào)度、通用計算處理、總線仲裁、內(nèi)外存儲、數(shù)據(jù)接口以及外采三方等多功能單元構(gòu)成。對于不同類型的功能單元,其驗(yàn)證流程及策略各有其特點(diǎn)。

1.2 需求:功能性能功耗平衡

閃存主控數(shù)據(jù)流的調(diào)度效率除硬件本身的吞吐率和延遲指標(biāo)外,還受片上運(yùn)行的處理調(diào)度算法的性能影響。因此其驗(yàn)證策略上需要重視芯片在不同數(shù)據(jù)業(yè)務(wù)模式下的功能準(zhǔn)確、性能達(dá)標(biāo)和相應(yīng)的功耗表現(xiàn)。

1.3 問題:單元與系統(tǒng)偏差

閃存主控的內(nèi)部功能單元均有預(yù)期的質(zhì)量指標(biāo)。但功能單元質(zhì)量滿足目標(biāo)與實(shí)際業(yè)務(wù)滿足需求仍舊存在偏差,其契合度依賴于固件和硬件的協(xié)同處理。例如數(shù)據(jù)粒度,內(nèi)外存分配管理策略等,都會對系統(tǒng)應(yīng)用產(chǎn)生影響。為了達(dá)到功能、性能和功耗的有效平衡,需要固件的反復(fù)調(diào)試,甚至硬件架構(gòu)的調(diào)整迭代,其開發(fā)周期較長。

2.閃存主控驗(yàn)證流程策略

為了滿足芯片產(chǎn)品高效能、快產(chǎn)出、低風(fēng)險的需求,憶芯通過架構(gòu)和實(shí)踐,實(shí)現(xiàn)了適配閃存主控設(shè)計驗(yàn)證的驗(yàn)證方法論及相關(guān)流程策略等。

2.1 ESL設(shè)計驗(yàn)證流程概述

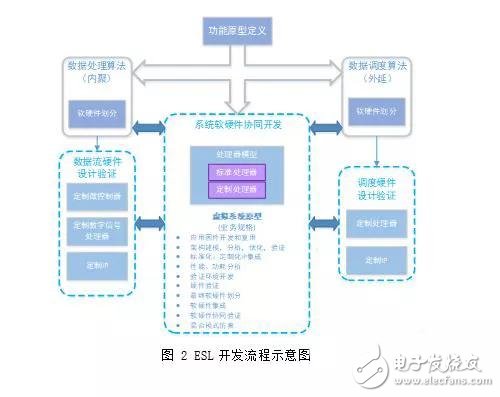

ESL(電子系統(tǒng)層次)設(shè)計驗(yàn)證方法是以能夠緊密配合的方式開發(fā)、優(yōu)化和驗(yàn)證復(fù)雜的系統(tǒng)架構(gòu)及嵌入式固件的方法學(xué),它提供了寄存器傳輸級(RTL)實(shí)現(xiàn)的驗(yàn)證基礎(chǔ)。通俗的說法,可以認(rèn)為它提供了同時開展原型系統(tǒng)研發(fā)、軟硬件劃分、固件開發(fā)、硬件驗(yàn)證的方法,讓芯片未實(shí)現(xiàn)之前就可以著手片上軟件開發(fā)工作,縮短開發(fā)周期。

對于閃存主控設(shè)計來說,ESL方法利用事務(wù)傳輸?shù)能浖P?a href="http://www.xsypw.cn/analog/" target="_blank">模擬硬件模塊劃分;利用處理器的模擬軟件進(jìn)行業(yè)務(wù)調(diào)度;利用數(shù)據(jù)結(jié)構(gòu)+命令接口模擬閃存的模型;在設(shè)計初期通過軟件原型系統(tǒng)了解調(diào)用其中的瓶頸或者高頻訪問的業(yè)務(wù)部分,分析系統(tǒng)吞吐帶寬,重點(diǎn)加速突破,快速迭代,整體加速了研發(fā)的進(jìn)程。關(guān)于設(shè)計方法細(xì)節(jié)本文就不加以贅述了。

而對于驗(yàn)證來說,基于ESL方法論的平臺開發(fā)與應(yīng)用方式與傳統(tǒng)芯片驗(yàn)證有較大不同。

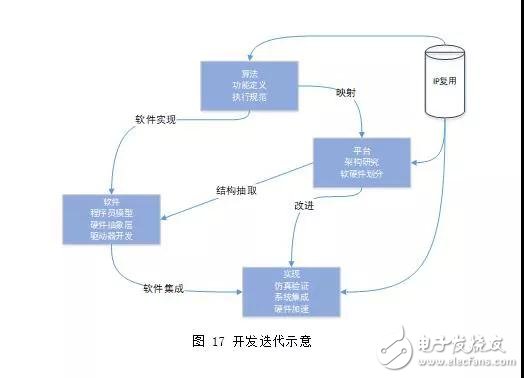

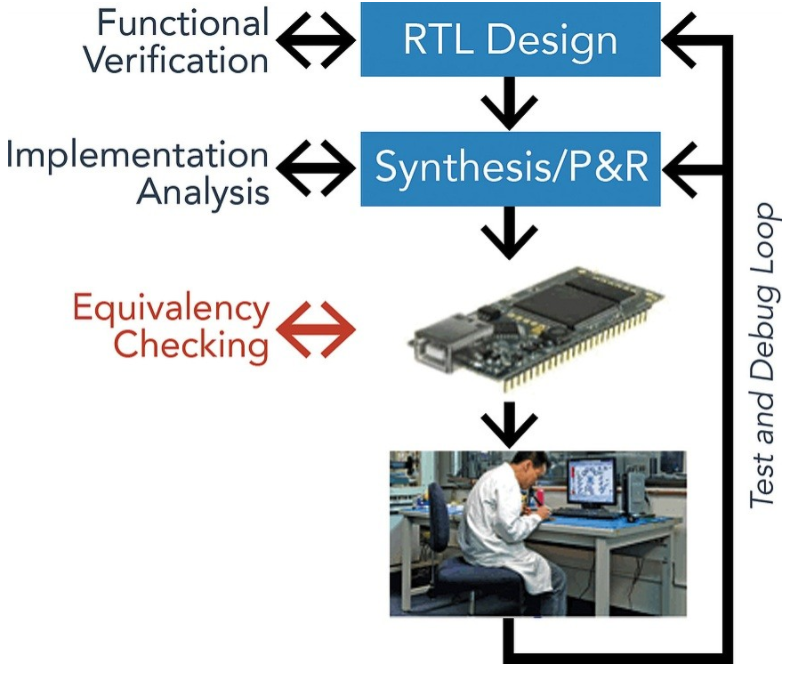

傳統(tǒng)方法中的設(shè)計驗(yàn)證迭代策略如下圖所示:

傳統(tǒng)流程在原型系統(tǒng)軟硬劃分完成后,首先開始硬件的設(shè)計以及驗(yàn)證仿真工作。在發(fā)現(xiàn)問題時,直接做硬件結(jié)構(gòu)的迭代優(yōu)化,而極少反饋到原型系統(tǒng)改動。但是此時并發(fā)的片上軟件研發(fā)仍是基于原始抽象的事務(wù)流程開展的,其控制接口定義乃至處理流程都可能與硬件系統(tǒng)形成差異。為了彌補(bǔ)該差異,通常會進(jìn)行FPGA平臺的軟件開發(fā)調(diào)試使其適應(yīng)于硬件的迭代演進(jìn)。但該方法受限于硬件開發(fā),需要單元驗(yàn)證穩(wěn)定后才能夠開展。同時,由于FPGA平臺與實(shí)際芯片存儲和總線的差異,關(guān)于性能及功耗的驗(yàn)證無法固定軟件方案,需要進(jìn)行耗時的芯片性能前端仿真加以確認(rèn)和修改;芯片實(shí)際生產(chǎn)后,仍需要進(jìn)行后續(xù)研發(fā)適配以及較長周期的迭代優(yōu)化。可以認(rèn)為片上軟件方案對于FPGA/ASIC分別都是部分定制性質(zhì)的。即使硬件規(guī)格不做任何改動完全符合原始設(shè)計規(guī)格需求,其實(shí)際硬件與固件的開發(fā)適配仍舊需要二次迭代,這是由軟件和硬件研發(fā)平臺的分立特點(diǎn)決定的。

而基于ESL的驗(yàn)證平臺系統(tǒng)的開發(fā)是從系統(tǒng)層次的業(yè)務(wù)需求開始的,從最初實(shí)現(xiàn)就體現(xiàn)了軟硬件協(xié)同和一致性導(dǎo)向。其與傳統(tǒng)驗(yàn)證方法的根本區(qū)別是開發(fā)的調(diào)度軟件或者功能模型可以和硬件實(shí)例配合,在混合系統(tǒng)里進(jìn)行協(xié)同仿真驗(yàn)證;

同時基于標(biāo)準(zhǔn)接口開發(fā)的各組件可以幾乎無縫的適配軟件功能原型平臺和硬件仿真系統(tǒng)。以下是ESL的一種典型開發(fā)方式的示意圖,定制硬件設(shè)計的同時,軟件實(shí)現(xiàn)固件、架構(gòu)、集成、驗(yàn)證仿真、分析的多類迭代的一致性出口,使得整體的開發(fā)過程不依賴于硬件設(shè)計的完備程度,且能為反向快速迭代硬件提供有力平臺保障。

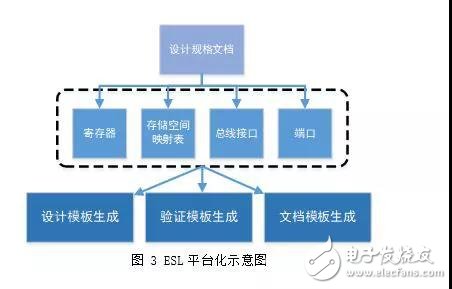

2.2 設(shè)計驗(yàn)證的平臺化

為了系統(tǒng)快速迭代,需要對軟硬件接口形式進(jìn)行統(tǒng)一管理,實(shí)現(xiàn)標(biāo)準(zhǔn)定義下軟硬件的寄存器,接口,連接關(guān)系和基礎(chǔ)測試模板的自動化生成。其中利用了標(biāo)準(zhǔn)化的IP-XACT定義規(guī)范。示圖如下:

2.3 驗(yàn)證架構(gòu)策略

對于閃存主控驗(yàn)證實(shí)現(xiàn)的方法策略分為兩類情況加以闡述。

2.3.1 新架構(gòu)

對于全新架構(gòu)的芯片,由于大部分硬件均為首次實(shí)現(xiàn),需要進(jìn)行自下而上的設(shè)計驗(yàn)證開發(fā)。其主要需求是規(guī)范的單元模塊驗(yàn)證平臺,能夠提供可復(fù)用的激勵和采樣的接口定義和主、被動模式靈活調(diào)整的激勵,檢查單元組件以及與上下游單元的接口連接關(guān)系文件。而且要求參數(shù)化定義接口,來靈活適配不同項(xiàng)目的配置調(diào)用。

該策略配合ESL平臺,可以在硬件架構(gòu)出現(xiàn)小范圍改動時第一時間一致更新原型系統(tǒng)、軟件模型及新硬件。當(dāng)單元功能開發(fā)通過回歸測試達(dá)到一定穩(wěn)定性后,可以逐步進(jìn)行部分的系統(tǒng)聯(lián)合測試。單元集成過程通過上下游功能模塊的接口定義自動連接完成。

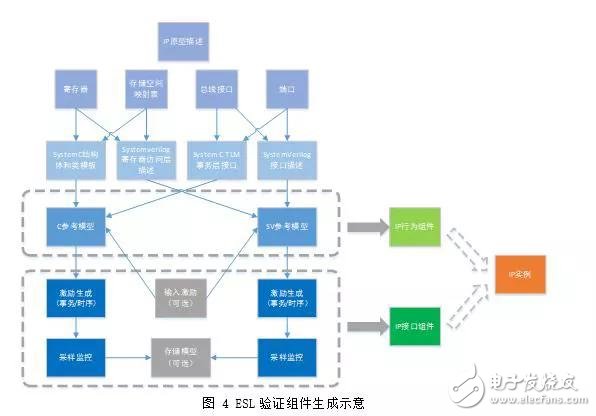

其基本關(guān)系適配的情況如下圖所示:

由圖所示,通過功能單元的原型描述生成軟件系統(tǒng)事務(wù)級的接口以及實(shí)際核心功能的參考模型框架,并開發(fā)實(shí)現(xiàn)C和Systemverilog的功能模型。對于仿真平臺需要使用的激勵和采樣監(jiān)控等功能,該流程也提供了接口、存儲和寄存器訪問層適配等基礎(chǔ)組件。信號內(nèi)聚的行為組件和外延的接口組件兩部分統(tǒng)一,構(gòu)成了功能單元的參考模型,最終會以IP功能單元的設(shè)計實(shí)例作為比較對象,對其進(jìn)行驗(yàn)證。

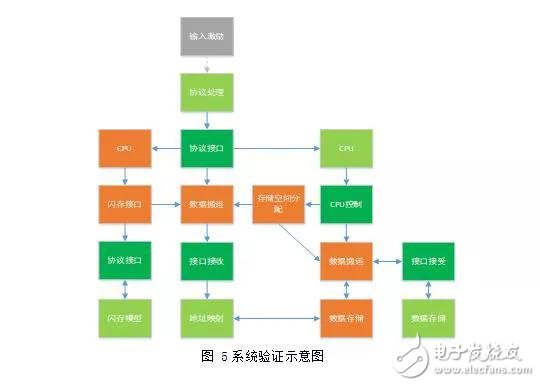

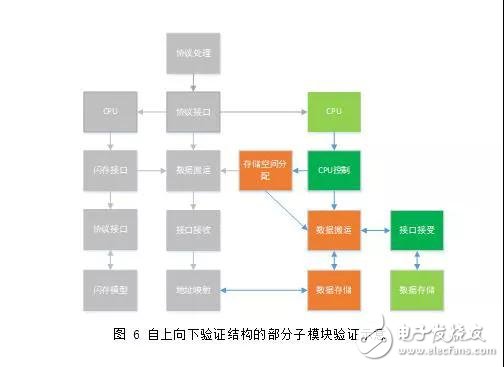

向上集成的流程會分步驟進(jìn)行行為組件+接口組件和成熟功能單元的混合連接,對于部分已完成設(shè)計的功能單元進(jìn)行子系統(tǒng)級別的驗(yàn)證,最終實(shí)現(xiàn)全實(shí)際硬件系統(tǒng)的驗(yàn)證。開發(fā)某中間階段閃存控制芯片系統(tǒng)驗(yàn)證示例如下:

由圖可見,驗(yàn)證子系統(tǒng)由部分軟件模型和硬件實(shí)例混合構(gòu)成。硬件實(shí)例的驗(yàn)證借助于實(shí)例上下游的軟件模型,對于數(shù)據(jù)通路的相關(guān)部分加以探測及數(shù)據(jù)采集。各個子模塊的業(yè)務(wù)比較可以通過內(nèi)置或者外接的記分板、斷言等對采集的數(shù)據(jù)進(jìn)行靈活應(yīng)用。

2.3.2 迭代架構(gòu)

閃存主控芯片架構(gòu)成熟后的開發(fā)多考慮迭代演進(jìn),其片上系統(tǒng)的主體架構(gòu)不變,只更新某些功能單元或調(diào)整部分架構(gòu)。驗(yàn)證開發(fā)可以用更新模塊的ESL模型并結(jié)合功能單元的參考模型進(jìn)行部分系統(tǒng)的替代進(jìn)行原型系統(tǒng)驗(yàn)證。

對新單元模塊,為了保障流程上不受到多模塊聯(lián)合調(diào)試初始階段異常查錯難以定位的影響,可以通過其上游單元參考模型為需要驗(yàn)證的子模塊提供接口激勵,同時配合該單元的下游功能單元的數(shù)據(jù)采集進(jìn)行驗(yàn)證,其他模塊內(nèi)部可以空置,以加速該模塊的驗(yàn)證過程。而片上系統(tǒng)的整體驗(yàn)證則可以基于ESL級別的C程序控制架構(gòu)及流程進(jìn)行平臺遷移,保證調(diào)度程序的一致性和無縫切換。其部分子模塊驗(yàn)證示意如下:

灰色部分即是純空接口的模型。為了驗(yàn)證新設(shè)計數(shù)據(jù)搬運(yùn)的功能,使用了CPU的模型以及部分存儲模型。

2.4 性能及功耗驗(yàn)證

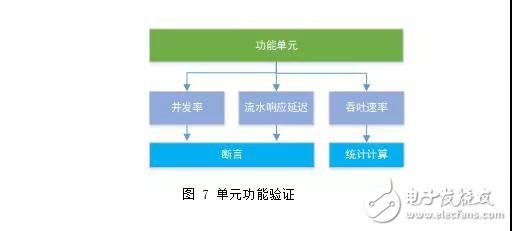

對于閃存主控來說性能指標(biāo)和各類工況的功耗指標(biāo)是產(chǎn)品競爭力的關(guān)鍵體現(xiàn)。對于系統(tǒng)的并發(fā)度、吞吐率和響應(yīng)延遲都有明確的驗(yàn)證要求。我們這里借用了軟件工程的測試方法來闡述。例如負(fù)載測試、壓力測試、沉浸測試、尖峰沖擊測試、配置測試、隔離測試等。負(fù)載和尖峰沖擊測試基于仿真平臺進(jìn)行,重點(diǎn)在系統(tǒng)的瞬時和持續(xù)極端硬件性能的驗(yàn)證。而壓力和沉浸測試會基于FPGA平臺進(jìn)行,對于系統(tǒng)長時間運(yùn)行穩(wěn)定的硬件信號基礎(chǔ)進(jìn)行驗(yàn)證。配置測試和隔離測試則會對芯片業(yè)務(wù)不同模式下的功耗需求和模塊開關(guān)定義進(jìn)行驗(yàn)證。

2.4.1 性能的分段驗(yàn)證

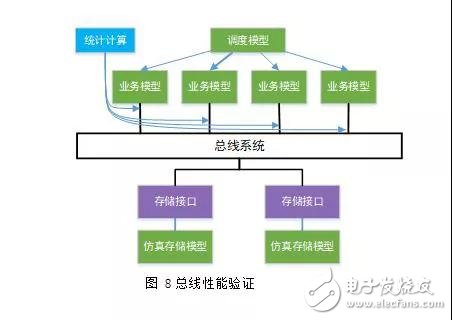

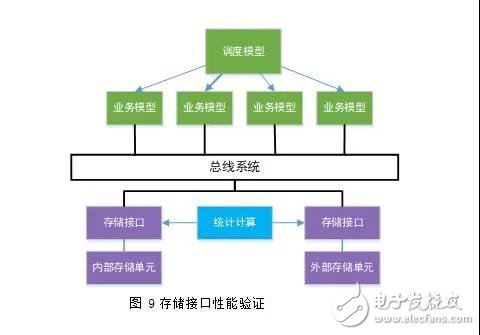

系統(tǒng)整體性能滿足需求的前提是確保單元模塊性能達(dá)標(biāo)。為此首先對各單元的數(shù)據(jù)流水延遲和吞吐速率統(tǒng)計分析驗(yàn)證。接著模擬真實(shí)業(yè)務(wù)功能模塊,真實(shí)總線配合理想的內(nèi)外存吞吐,通過統(tǒng)計計算保證總線能夠有效的進(jìn)行上游數(shù)據(jù)的接受和分發(fā)。該步驟可能會進(jìn)行內(nèi)外存尺寸,訪問方式等各類優(yōu)化。然后在該系統(tǒng)上通過功能單元仿真模型擬合的延遲和吞吐的綜合測試實(shí)際內(nèi)外存、存儲接口。以上各部分在前端仿真平臺可實(shí)現(xiàn)。其結(jié)構(gòu)如下各圖所示。

2.4.2 性能的綜合驗(yàn)證

通過單元的性能驗(yàn)證能夠保證理想工況下硬件的單元性能。而真正結(jié)合調(diào)度控制邏輯,對于閃存主控前后端通路進(jìn)行調(diào)度效率和性能驗(yàn)證調(diào)優(yōu)在芯片投片前會分兩步驟進(jìn)行。

一、通過FPGA進(jìn)行關(guān)鍵業(yè)務(wù)通路性能的等效計算。

其驗(yàn)證關(guān)注前端接口吞吐率及延遲,系統(tǒng)核心與片上內(nèi)存吞吐率及延遲和后端閃存接口的吞吐率及延遲。因?yàn)橄到y(tǒng)時鐘頻率以及FPGA的內(nèi)外存都與實(shí)際芯片不同,所以全流程業(yè)務(wù)性能不作為該階段驗(yàn)證目標(biāo)。

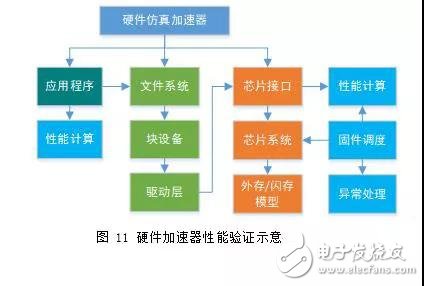

二、采用硬件加速器進(jìn)行真實(shí)操作系統(tǒng)連帶設(shè)備驅(qū)動接口的驗(yàn)證。

由于實(shí)際硬件加速器對外物理接口是標(biāo)準(zhǔn)頻率但仿真芯片系統(tǒng)運(yùn)行在較低頻率,需要操作系統(tǒng)驅(qū)動的修改以防止協(xié)議訪問超時的情況。

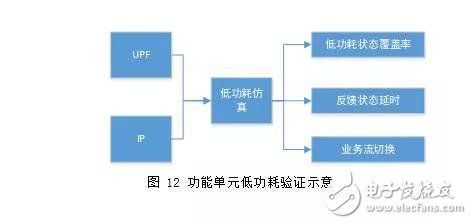

2.4.3 功耗的單元驗(yàn)證

系統(tǒng)低功耗設(shè)計基于ESL軟件模型代碼調(diào)用統(tǒng)計分析,軟硬件劃分之后開始實(shí)施功能單元的低功耗驗(yàn)證工作。其驗(yàn)證關(guān)注低功耗控制序列在單元上執(zhí)行時各功耗狀態(tài)切換流程的可靠性。內(nèi)容包括而不限于時鐘的調(diào)節(jié)、關(guān)斷;復(fù)位的控制;電壓的切換;電源的隔離管理;內(nèi)存工作狀態(tài)調(diào)整以及整體子電源域控制等部分。

通過內(nèi)部信號探針及斷言,驗(yàn)證可有效保證功能單元確實(shí)經(jīng)歷過低功耗的各個定義狀態(tài)(PST)以及正常恢復(fù)功能應(yīng)用。例如帶有動態(tài)切換頻率及電壓的功能設(shè)計,頻率切換通過網(wǎng)表+時序約束文件進(jìn)行多頻率節(jié)點(diǎn)仿真,保證時序裕量;對于電壓的變換則通過仿真的電源狀態(tài)覆蓋率(PST coverage)來確定。整體的功耗控制描述均由IEEE-1801規(guī)范確定的UPF文件來定義。不同狀態(tài)功耗估值也可通過對仿真波形計算統(tǒng)計得到結(jié)果。

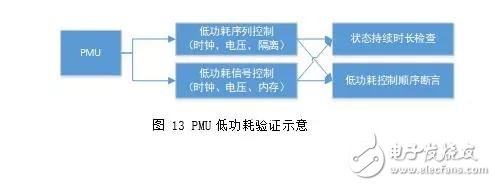

對于功耗控制單元(PMU)的驗(yàn)證,除了利用參考模型與硬件輸出控制狀態(tài)比較來保證各單元功耗狀態(tài)切換過程靈活、準(zhǔn)確,對于實(shí)際系統(tǒng)多個單元低功耗狀態(tài)的銜接配合,也會以交叉的功能覆蓋率加斷言的形式加以驗(yàn)證。

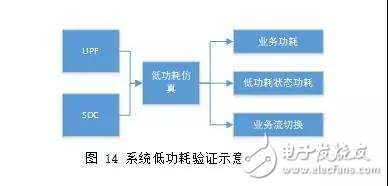

2.4.4 功耗的整體驗(yàn)證

對于實(shí)際整體片上系統(tǒng)功耗,首先通過帶有UPF的系統(tǒng)級前端仿真來驗(yàn)證,確定各個不同模式下電源域、時鐘域的切換準(zhǔn)確。UPF迭代穩(wěn)定后,通過硬件加速器業(yè)務(wù)仿真來確定功耗符合預(yù)期范圍。在網(wǎng)表綜合階段,通過形式化驗(yàn)證來保證插入的電源隔離、電源控制和電壓控制等單元符合設(shè)計時的UPF描述定義。

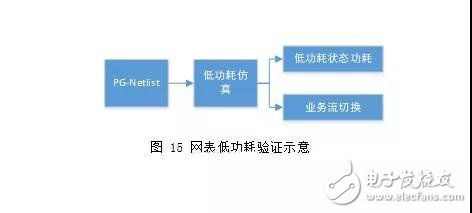

布局布線后,通過網(wǎng)表仿真(PowerGating-Gatesim),保證其實(shí)際業(yè)務(wù)切換時延及相應(yīng)的控制流程準(zhǔn)確,因?yàn)閮H形式化驗(yàn)證對某些特殊處理無法給出結(jié)論。其示意如下:

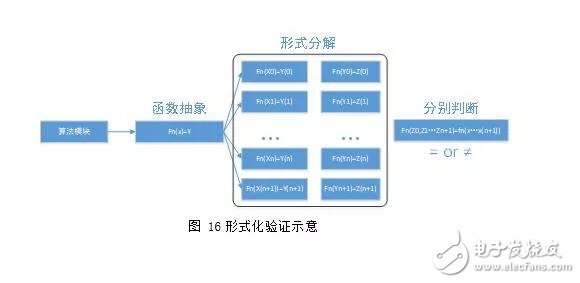

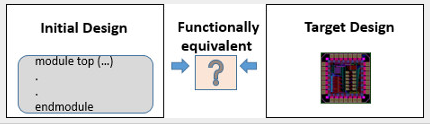

2.5 形式化驗(yàn)證

對于安全加密使用的模塊,除了保證功能性能以外,其自身的安全性如何保障是通過形式化驗(yàn)證的方法進(jìn)行的,其目標(biāo)是所有的代碼功能有效及失效分析均可以通過數(shù)學(xué)公式加以論證,為提高安全單元的可靠性提供保障。其抽象示意如下圖。

關(guān)于模塊、系統(tǒng)的異常處理部分也可以作為驗(yàn)證目標(biāo),基于形式化驗(yàn)證的方法進(jìn)行失效分析和安全策略調(diào)試。

2.6 總結(jié)

ESL方法使得驗(yàn)證可以利用基于軟件仿真器+ESL平臺開發(fā)的閃存主控固件開展,和硬件設(shè)計基本同步開始,并可以通過標(biāo)準(zhǔn)協(xié)議提供控制接口移植至FPGA進(jìn)行開發(fā)。同時調(diào)度程序也可無縫移植到硬件加速器進(jìn)行系統(tǒng)驗(yàn)證。在實(shí)際系統(tǒng)開發(fā)過程中,兩者的應(yīng)用保證團(tuán)隊可以快速獲得硬件以及固件驗(yàn)證的結(jié)果并可以相互配合分析迭代,加速整體研發(fā)進(jìn)程。在開發(fā)時,各團(tuán)隊并發(fā)同步,且回片可即刻進(jìn)行全流程的綜合調(diào)試及固件的調(diào)優(yōu)過程,降低時間成本。同時,分層驗(yàn)證組件的構(gòu)架提供可互換的軟硬件模型,可加快整體系統(tǒng)的實(shí)現(xiàn)和調(diào)試節(jié)奏。形式化驗(yàn)證則提供了安全可信的功能設(shè)計基礎(chǔ)。

3.問題提示

實(shí)際閃存主控驗(yàn)證需要關(guān)注外部業(yè)務(wù)接口發(fā)生錯誤后易混淆的部分,需要著重加強(qiáng)可測性設(shè)計以及提供充分的業(yè)務(wù)測試,特別針對協(xié)議規(guī)定的異常處理以及避免整體系統(tǒng)失效的處理設(shè)計,要加以重點(diǎn)驗(yàn)證。

電子發(fā)燒友App

電子發(fā)燒友App

評論