芯片性能優化真的是零和博弈嗎?在設計過程中,我們應該賭注押在哪里才能獲得性能的最優解決方案?

所謂零和博弈又稱零和游戲(Zero-sum game),與非零和博弈相對,是博弈論的一個概念,屬非合作博弈,指參與博弈的各方,在嚴格競爭下,一方的收益必然意味著另一方的損失,博弈各方的收益和損失相加總和永遠為“零”。雙方不存在合作的可能。

從芯片中榨出最后一點性能聽起來是個不錯的主意,但這會增加風險和成本,也延長了開發時間,降低了產量,甚至可能限制芯片的運行環境。

然而,鑒于開發過程的每一步所附加的裕度,顯然我們可以做出很多改進。 Plunify公司業務發展副總裁Kirvy Teo表示:“只要時間足夠,每個設計都可以進行優化,但時間是奢侈品。折衷是一種零和游戲,克服這種困難是一項挑戰。”

在實踐中,看似簡單的理論遠沒有那么簡單。

Open-Silicon公司芯片工程總監Sureshbabu Kosuru表示:“設計團隊應該始終以實際性能指標為目標,并在設計的早期階段對其進行定義。為了滿足緊張的日程安排而投機取巧,會增加芯片日后遇到性能問題的風險。設計團隊應該通過遵守代工廠和IP供應商的建議來開發和實踐最好的方法,把裕度建立到芯片中,并在未來的項目進度中計入這些開銷。”

這里的關鍵是,期望的性能水平必須是開發過程的一部分。

西門子公司設計驗證技術部門營銷總監Neil Hand表示:“在執行層面上推進性能極限是非常有限的,而且風險很高。此外,如果不考慮性能老化,那么就會像神話中的伊卡洛斯一樣,飛得離太陽太近了。”

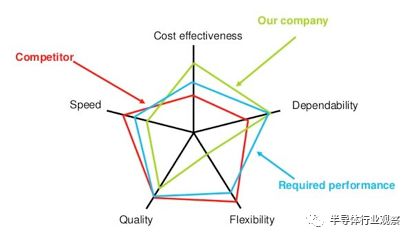

圖1: 產品折衷 (來源:哥本哈根商學院)

部分問題在于,更新的技術可能存在一些問題,這些問題沒有被設計人員、工藝技術的開發人員,以及EDA行業的設計者完全理解并表述。Kosuru說:“設計團隊應該意識到最新的技術變化及其不良影響。他們可能需要額外的分析或改進方法來應對這些變化。代工廠應定期更新客戶關于工藝成熟度和裕度的信息,以便挑戰設計裕度不會因為延長工藝周期而損害設計。”

裕度有很多來源。ANSYS半導體事業部首席技術專家Joao Geada列出了一個運營清單:

用于補償設計角度之外出現的效應的裕度。例如,鎖相環抖動、封裝與電路板的RLC諧振。

允許制造工藝與工藝模型之間的差異的裕度。“設計需要時間來創建,代工工藝也在不斷發展。在設計周期后期采用最新的代工模型通常過于昂貴,所以要為模型與將要生產的產品之間的差異留出裕度空間。從基本上講,你可以通過損失一些PPA來獲得更可預測的制造工藝和產量。 ”

在傳統的電源/地(pg)網格設計中進行的補充。“傳統方法假定pg需要均勻分布,而不考慮功率需求取決于設計的局部性質。例如,有些區域比其他區域更耗電。但是傳統流程有pg和時序解耦, 因此兩者都不能利用或影響另一個。 在傳統流程中,整個pg網格被設計成特定的最大。

避免先前“遺漏的缺陷”的裕度。“大多數大公司都制造了糟糕的硅片,并對其進行了調試。在某些情況下,遺漏的缺陷不能用現有的解決方案來解決,因此,為了避免未來的缺陷,需要把悲觀估計添加到流程中。隨著工具變得越來越好,其中一些裕度變成了歷史性的補充,從而不再合理。

用來解決效應之間的相互作用的補充。“大多數現有的解決方案都是針對單個物理問題,而不是處理效應之間的相互作用。”

Geada還列舉了一些經常不被考慮的相互作用的例子,包括:

依賴于波形效應的約束。“靜態時序分析(STA)無法模擬這些效應。現有的標準單元設計描述了約束條件,卻沒有任何關于設計效應的知識。(在低電壓下,這種效應可以達到+-50%。)

變化幅度。這會影響擺動和延遲,而擺動幅度會影響延遲和延遲幅度,但是STA無法模擬它們之間的相互關系。

IR下降和時序的相互作用。它們相互依賴,但傳統流程將它們模擬為非相關效應。

溫度變化。在大型SoC中,溫度變化不是恒定的數值,但在傳統的基于角點特征的解決方案中,它就是這樣模擬的。

重要的第一步是了解設計要適用在什么樣的市場和環境中。Open-Silicon公司的Kosuru表示:“對于STA工程師來說,了解芯片的功能和設計需要適用的環境條件非常重要。例如,如果設計不是為了在0°C以下工作,那么讓設計接近標準的-40°C溫度就毫無意義。在較低的技術節點(28nm及以下)中,這意味著由于逆溫現象,我們可以將設計性能提高至少7%至10%。這里的折衷是,IP供應商,包括標準單元的IP供應商,愿意為我們所希望的溫度提供特征庫,而他們僅僅是為了大量投資而已。這通常會對設計收斂造成不利影響。”

關注點分離

EDA流程中的許多工具都是隨著遇到特定問題和發現解決方案而演變的。這導致工具常常用來單獨處理每個問題。設計團隊也是如此。

ANSYS公司CPS解決方案高級產品經理Youngsoo Lee表示:“按照傳統的基于各自獨立的設計方法,芯片、封裝、電路板和系統設計人員使用預先確定的裕度來設計其特定組件。這些設計是由單獨的團隊,甚至單獨的公司完成的,他們之間的溝通很少。另外,現有的工具限制了每個設計團隊每次只能分析和解決單一物理量(時間、功率、溫度等),而不會看到多個物理量之間的相互作用。單獨設計和分析每個組件顯然是不夠的,一次只考慮單一的物理量同樣也不可取。”

許多工具也簡化了這個過程,或者做出了可能的悲觀假設。ANSYS半導體事業部產品營銷經理Annapoorna Krishnaswamy表示:“傳統的統一過度設計電網的方法,在較老的工藝技術中運行良好,但由于嚴格的布線限制,在先進的技術節點上無法使用。這可能會導致未來的時序收斂問題。對于高級finFET技術工藝,電網節點數量很大,任何節點數量的減少都會導致精度損失。由于設計裕度非常小,因此,功率驗收解決方案必須非常精確,否則可能導致產品失敗。對整個電網進行分析是非常重要的,不能采用‘分而治之’的方法來分割設計,否則會導致不準確。這種分析完全忽略了電網覆蓋的完整芯片環境。”

改變模型

隨著時間的推移,行業使用的模型已經改變。考慮到在20世紀80年代,所有重大的延遲都與門有關,導線是不受約束的。如今,情況幾乎完全相反。于是導線被模擬為RC模型,今天我們發現這可能還不夠好。擁有舊范式最暢銷工具的公司不愿改變,用戶同樣不愿改變,直到有錯誤出現。

互連的重要性不可忽視。Helic公司營銷副總裁Magdy Abadir指出:“嵌入所有緩沖中繼器的全局互連往往消耗芯片總功率的60%,主要的互連網絡,如電源和時鐘分配網絡和寬總線,是故障機制的來源,包括抖動、電遷移、功率分配的下降和耦合噪聲。因此,尖端芯片的性能和風險規避都是互連建模和設計的非常強大的功能。”

在芯片設計方面,電感是個丑小鴨。開羅美國大學納米電子學和器件中心主任Yehea Ismail解釋說:“從歷史上看,互連已經被廣泛地建模為RC網絡。磁效應(電感和電感耦合)在很大程度上被忽略和抑制,因此可以使用現有的工具。忽略磁效應主要是一種簡化思考和追趕上市時間的決定,通常是由極端的裕度和抑制感抗效應的設計方法來進行驗證。然而,這種設計方法正變得越來越難以驗證,甚至難以維持,因為頻率的提高幾乎肯定會很快發生,SoC也越來越復雜。”

一個邏輯問題是,在功率和延遲方面,忽視感抗效應的成本有多大?Abadir說:“我們已經看到設計需要付出巨大的功率和性能損失,以適應現有的基于RC的工具。例如,在總線上使用差分開關,并把攜帶相反的開關信號的線路布線在彼此相鄰的位置。這種方法有效地減少了電感耦合的范圍和幅度。因為相反的電流彼此接近會產生相反的磁場,從而相互抵消。然而,相對于單線開關或兩根有源耦合導線的平均開關的情況,彼此相鄰的反向開關導線消耗的功率是它們之間的耦合電容消耗功率的4倍。此外,延遲是單線開關的兩倍。”

Ismail說得很直白。“電感實際上是一種有用的元件,電阻對性能是有害的。電感是一種本身不消耗功率的電抗元件,而電阻是一種消耗功率的有源元件。兩種元件總是在互連網絡中串聯出現,抑制電感總是會因為電阻效應的提升而導致更多的損耗。”

新方法

放寬其他約束可以克服許多性能極限。Movellus公司首席執行官Muhammad Faisal表示:“我們正在討論給定功率的抖動,這永遠是一種折衷。如果你想要更小的抖動,那就消耗更多的能量。客戶希望優化他們的SoC,并愿意放棄一點抖動,如果這樣能讓他們在其他方面不受約束,并帶來潛在的功率優化的話。在SoC中,你可能會在角落里有一個鎖相環,然后你在芯片上傳輸高頻信號,結果是,你在時鐘樹中積累了大量的抖動。所有與開關有關的噪聲都被添加到時鐘中。如果你可以合成鎖相環,你就可以把它們放在使用時鐘的模塊旁邊,這樣就可以消除抖動了。”

你知道的越多,設計就會表現得越好。 Moortec公司首席執行官Stephen Crosher表示:“一種推動性能極限的方法是,通過對影響器件性能的動態變量進行嵌入式監控來最小化風險,例如PVT(工藝、電壓、溫度)。IC和SoC設計人員擁有了監控影響芯片性能的參數,以及監控在溫度和電壓應力下的電路失效的能力,便可以構建更加高效、高性能和高性價比的產品。”

Crosher解釋了提高性能的方法。“嵌入式監控為片內控制器提供更新,這有助于記錄和解釋結果。許多應用都可以使用這種兩級體系結構,從產品測試中的片內參數的一次性分析,到處理器核心和內存的實時主動管理,從而避免局部老化效應,并在給定的電壓和溫度點上最優化性能。”

工具也可以改變。Plunify公司的Teo表示:“一種解決辦法就是機器學習。使用機器學習實際上類似于使用蠻力來處理大量數據。然而,機器學習的關鍵區別在于,你可以更早地訓練模型,以提高它的準確性并進行保存,并在需要的時候使用它。坐標軸開始從‘運行時間vs QoR’演化為‘數據vs QoR’。能夠積累和分析的數據越多,預測模型就越好。可以預測問題或預測性能的工具可以在糟糕的設計選擇上節省寶貴的迭代。最終,這將是優秀設計和平庸設計之間的區別。”

新的電路技術也可以改變一些長期以來的看法。Faisal表示:“數字設計師總是用固定頻率和電壓設計他們的模塊,因為頻率來自于鎖相環的設計,而模擬被認為是黑魔法。你必須假定這個頻率,然后用這個頻率進行時序收斂。當你可以使用數字方法來實現數字鎖相環時,你便可以開始對約束數字模塊的因素(即頻率和裕度)進行協同優化,并且可以對它們一起進行協同優化。這就開辟了額外的設計空間,從而實現更多的優化。”

有時候最艱難的教訓是我們不愿意聽到的。西門子公司的Hand表示:“作為一個行業,我們一直被推動接近裕度——這是人之常情。但是,這并不是要取得巨大收益的地方。正如他們所言,‘在裕度邊緣徘徊。’真正的性能是在系統級別設計和驗證的。”

Hand表示:“系統級的性能分析,以及一個跨越模擬、仿真和原型的統一驗證和驗證平臺,可以在設計過程中盡早考慮性能折衷,并隨著設計實現的不斷完善在軟硬件方面不斷進行完善。”

他們都有一個共同點:你的知識越多,做出的決定就越好。當信息被故意忽略時,其含義必須是清楚的。否則,你最好增加足夠的裕度來彌補。

-

芯片

+關注

關注

456文章

51149瀏覽量

426175 -

電感

+關注

關注

54文章

6153瀏覽量

102596 -

低電壓

+關注

關注

5文章

128瀏覽量

29884

發布評論請先 登錄

相關推薦

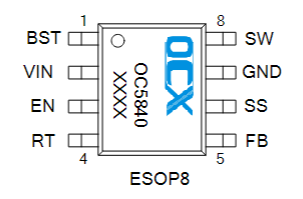

歐創芯電源芯片OCE200產品介紹

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+介紹基礎硬件算法模塊

介紹FIR濾波模型的建立,分4個步驟

Linux服務器性能查看方法

歐創芯電源芯片OC5840產品介紹

芯片測試有哪些 芯片測試介紹

人工智能神經網絡芯片的介紹

性能測試的實現方法是什么

ARM系列STM32F103芯片的解密方法

詳細介紹OVP過壓保護芯片的功能及使用方法

關于芯片性能的介紹和方法介紹

關于芯片性能的介紹和方法介紹

評論