明確并滿足不同的需求

互連產品發(fā)展迅速:最初的系統(tǒng)相對簡單,最具挑戰(zhàn)性的設計需求通常也只涉及通信的某些方面;而如今,設計人員的處境卻更為艱難:各個應用領域中,需求組合不斷擴展,卻幾乎不容妥協(xié)任何方面。每種應用都要求開發(fā)人員根據(jù)需要轉移重點,以應對該應用獨有的挑戰(zhàn)。不過,對更高性能和更低功耗的需求卻是大多數(shù)主流應用領域的共同主題。

例如,智能工廠不僅依賴于低延時、高性能器件(用于信號處理),而且要求降低功耗,以便工廠工程師能在狹小空間中容納更多器件。消費類可穿戴設備不僅需要低功耗設計以延長電池續(xù)航時間,而且面臨著不斷增長的信號處理需求,以便能夠處理更復雜的工作負載。在各個應用領域中,設計人員承受的壓力越來越大,需要更有效地響應關于器件、網(wǎng)絡和企業(yè)資產的漏洞的實際擔憂,使其免遭來自個別網(wǎng)絡竊賊、犯罪組織甚至國家贊助團體的直接攻擊或高級持續(xù)性威脅。

為了滿足這些不同的需求,開發(fā)人員通常需要作出抉擇,在設計的某一方面作出妥協(xié)。他們可能會選擇犧牲應用性能以降低功耗,使用較低性能的處理器、降低時鐘速率,或者降低處理器的占空比來支持低功耗狀態(tài)。然而,為了滿足嚴格的性能要求,他們就可能會采取相反的做法,使用更強大的處理器、更快的時鐘速率和更高的占空比,但代價則是功耗劇增。對于計算復雜度較高的應用,他們可能會添加專用數(shù)字信號處理器 (DSP) 來加速算法執(zhí)行,但設計復雜性、成本和系統(tǒng)功耗也會相應增加。即使功耗與性能達到了可接受的平衡,他們往往也需要接受設計成本和復雜性的增加以滿足安全要求。

盡管設計人員為滿足不同需求而心力交瘁,但對于醫(yī)療設備、工業(yè)自動化系統(tǒng)、零售支付設備等關鍵應用,用戶可接受的妥協(xié)空間越來越小,甚至拒不接受。NXP Semiconductors 的 LPC55S6x 微控制器系列器件架構,既有通用處理器的靈活性,又有新興應用所需的專門處理能力和安全性,從而免除設計人員的妥協(xié)之困。

功能豐富,兼有專用處理內核

NXP Semiconductors 的單核LPC55S66和雙核LPC55S69微控制器是市面上首款基于Arm?Cortex?-M33 的通用 MCU,具有 Arm M 系列架構典型的低延時、確定性性能。NXP 的 LPC55S6x 器件在架構上加設了諸多增強功能,包括該公司的高性能 PowerQuad DSP 加速器、CASPER(Cryptographic Accelerator and Signaling Processing Engine with RAM,帶 RAM 的加密加速器及信號處理引擎)加密引擎以及全面安全子系統(tǒng)。除了高達 640 KB 的閃存、320 KB 的 SRAM 和 128 KB 的 ROM 外,LPC55S6x 器件還集成了大量功能元件,而這些元件通常需要用于所有深度嵌入式系統(tǒng)設計(圖 1)。

圖 1:LPC55S6x 微控制器架構在 Arm Cortex-M33 內核的通用處理能力基礎上,擴展了專門硬件模塊用于執(zhí)行信號處理、加密、安全存儲和密鑰管理,同時還提供典型嵌入式設計所需的全套外設。(圖片來源:NXP Semiconductors)

在這些功能元件中,LPC55S6x 器件配備了功能全面的定時器子系統(tǒng)、多個串行接口、安全的直接存儲器訪問 (DMA) 控制器和多達 64 個通用 I/O (GPIO) 引腳。除了這些數(shù)字子系統(tǒng),LPC55S6x 器件還集成了 16 位多通道逐次逼近寄存器 (SAR) 模數(shù)轉換器 (ADC)、模擬比較器和溫度傳感器。此外,片上可編程邏輯單元 (PLU) 允許開發(fā)人員配置 26 個五輸入查找表 (LUT) 結構,構建狀態(tài)機等自定義組合邏輯或時序邏輯。開發(fā)人員可以訪問 PLU 寄存器,直接對 PLU 編程以實現(xiàn)小型邏輯電路,或使用 NXP 工具實現(xiàn)使用 Verilog 寄存器傳輸語言 (RTL) 描述的較大型邏輯電路。

為了避免訪問多個子系統(tǒng)時出現(xiàn)瓶頸問題,LPC55S6x 器件采用多層總線矩陣,以 Arm 高級微控制器總線架構 (AMBA) 的高級高性能總線 (AHB) 架構構建。AHB 總線矩陣提供總線主控器與外設或存儲器之間的直接連接。例如,這種方法允許 DMA 傳輸以全速運行,而不會影響處理器對存儲器的訪問性能。事實上,在眾多設計需求中,使處理器效率最大化的能力是 LPC55S6x 架構的基礎。

在 LPC55S6x 架構中,Cortex-M33 內核提供多種功能來幫助設計人員更輕松地應對不同的設計要求。與其他同類器件一樣,LPC55S6x 處理器支持多種低功耗模式。如果器件長時間處于非活動狀態(tài),開發(fā)人員可以將器件置于省電模式,可以完全保留 SRAM 的內容,但是功耗僅為 15.4 μA;或將器件置于深度省電模式,繼續(xù)為 4 KB 的 SRAM 部分供電,而功耗只有大約 0.59 μA。休眠模式和深度休眠模式下,處理器關閉,但會為外設和存儲器提供不同程度的操作:休眠模式下可進行全面操作,功耗約為 2.7 mA,而深度休眠模式會對外設使用時鐘門控,從而將功耗降至約 110 μA。

增強功能

除了低功耗模式外,LPC55S6x 架構還通過集成功能擴展對不同設計需求的支持,從而提高性能和安全性。Cortex-M33 主內核內置的集成功能包括 Arm TrustZone 安全擴展 (SECEXT)、存儲器保護單元 (MPU)、IEEE 754 標準浮點運算單元 (FPU) 和嵌入式跟蹤宏單元 (ETM)。此外,主內核還包含 CASPER 加密引擎和 PowerQuad 加速器,支持 DSP 和單指令多數(shù)據(jù) (SIMD) 操作。

請注意:雙核 LPC55S69 微控制器的另一個 Cortex-M33 內核不包含這些附加功能。

對于這些集成子系統(tǒng)和架構特性,每個特性都能提供豐富的功能,相關詳細說明遠遠超出了本文的涵蓋范疇。例如,PowerQuad DSP 加速器本身就是精密協(xié)處理器,能夠獨立完成信號處理功能,同時又可作為總線主控器訪問存儲器。

在內部,PowerQuad 加速器將多個寄存器和接口與一組硬件引擎相結合,用于執(zhí)行關鍵信號處理功能,包括快速傅里葉變換 (FFT)、離散余弦變換 (DCT)、無限脈沖響應 (IIR)、有限脈沖響應 (FIR) 以及用于高效計算三角函數(shù)的坐標旋轉數(shù)字計算機 (CORDIC) 算法(圖 2)。

圖 2:NXP Semiconductors 的 LPC55S6x 微控制器系列集成了該公司的 PowerQuad 協(xié)處理器,后者使用專門引擎來加速信號處理應用常用算法的執(zhí)行。(圖片來源:NXP Semiconductors)

借助 PowerQuad 加速器,開發(fā)人員可以執(zhí)行復雜的信號處理運算,而不會影響主機處理器響應實時事件或完成一系列擴展操作。主機處理器只需使用所需的信號處理函數(shù)設置 PowerQuad 寄存器,并指定來源、目標和工作存儲區(qū)的存儲器地址。一旦調用,PowerQuad 加速器就會作為真正的協(xié)處理器運行,作為總線主控器使用 AHB 矩陣來執(zhí)行 128 位存儲器傳輸。與此同時,主機處理器可以立即返回執(zhí)行主處理任務,只需定期輪詢 PowerQuad 忙位,或簡單響應 PowerQuad 發(fā)送的完成中斷以訪問結果。

不過,對于開發(fā)人員而言,PowerQuad 操作大多是透明的。開發(fā)人員可使用標準應用程序編程接口 (API) 來調用 Arm Cortex 微控制器軟件接口標準 (CMSIS) 的 DSP 庫。NXP Semiconductors 的 MCUXpresso 軟件開發(fā)套件 (SDK) 包含支持 PowerQuad 的 NXP 版 DSP 庫。該庫通過調用 PowerQuad API 替代軟件實現(xiàn)的低級數(shù)學函數(shù)。

例如,若需計算復數(shù) FFT,開發(fā)人員使用標準 CMSIS-DSP 函數(shù)arm_cfft_q31(),數(shù)據(jù)設為 Q 格式,即 32 位定點數(shù)用 1 個符號位和 31 個指數(shù)位來表示。在純軟件實現(xiàn)中,調用arm_cfft_q31()函數(shù)會相應地調用 CMSIS DSP FFT 蝶形運算函數(shù)arm_radix4_butterfly_q31()和結束函數(shù)arm_cfft_radix4by2_q31();計算復數(shù)逆 FFT 時則會調用相應的反函數(shù)。

但是,若使用 NXP 的 DSP 庫和 PowerQuad,正常調用arm_cfft_q31()卻會調用PQ_TransformCFFT(),并在硬件中處理相同的計算。最終,不僅減輕了 Cortex-M33 內核的處理負荷,而且加速了 DSP 函數(shù)的執(zhí)行(圖 3)。

圖 3:MCUXpresso 軟件開發(fā)套件可顯著加速常用 DSP 算法的執(zhí)行,同時通過直接調用 PowerQuad 加速器來替代低級 CMSIS-DSP 函數(shù),從而保持與標準 Arm CMSIS DSP 庫高級調用的兼容性。(圖片來源:NXP Semiconductors)

CASPER 加密引擎作為另一個協(xié)處理器,同樣能減輕主處理器的負擔,使其免于處理與非對稱加密算法相關的繁重計算負荷。CASPER 加密引擎執(zhí)行 Rivest-Shamir-Adleman (RSA) 算法、Diffie-Hellman 算法、橢圓曲線加密法 (ECC) 和橢圓曲線數(shù)字簽名算法 (ECDSA) 的速度是 Cortex-M33 內核運行同類加密軟件的八倍。

為了加速對稱算法的執(zhí)行,LPC55S6x 還集成了硬件模塊以支持高級加密標準 256 位加密 (AES-256) 和安全散列算法 2 (SHA-2)。

這些硬件模塊與 CASPER 引擎的組合為開發(fā)人員提供基于硬件的支持,有利于實現(xiàn)身份驗證和數(shù)據(jù)加密常用的加密算法,滿足互連產品保護數(shù)據(jù)交換的需求。

正如本系列文章第 2 部分所討論,LPC55S6x 系列對安全性的支持遠遠超出了基本加密算法;該系列提供基于硬件的安全功能,可滿足全生命周期安全性的需求。

系統(tǒng)開發(fā)

借助 NXP 的LPC55S69 EVK,開發(fā)人員可以快速探索 LPC55S6x 微控制器的加密引擎、DSP 和通用處理能力。LPC55S69 EVK 旨在加速這些器件應用的開發(fā)工作,該電路板具有雙核 LPC55S69 微控制器、NXP 的MMA8652FCR1加速計、LED、按鈕、調試接口,并支持ArduinoUNO、MikroElektronicaClick 和DigilentPMod 附加硬件等多種擴展選項。

該電路板具有多個跳線和針座,可讓開發(fā)人員輕松設置不同的硬件配置并仔細檢測性能細節(jié)(圖 4)。例如,關注功耗的開發(fā)人員只需使用電壓表測量 P12 針座處的電壓降,便可測量 LPC55S69 的供電電流。

圖 4:NXP Semiconductors 的 LPC55S69 EVK 圍繞該公司的雙核 LPC55S69 微控制器構建,提供多個跳線和針座,使開發(fā)人員可以輕松配置并檢測微控制器的電流消耗等性能細節(jié)。(圖片來源:NXP Semiconductors)

開發(fā)應用時,設計人員可將該電路板與 MCUXpresso 集成開發(fā)環(huán)境 (IDE) 和 SDK 配合使用,該套件使用 PowerQuad 功能(如前所述)等 LPC55S6x 專用硬件。此外,IAR和 Keil IDE 也支持 LPC55S69-EVK。NXP 還提供免費軟件包,通過樣例代碼演示 LPC55S6x 功能使用的主要軟件設計模式。

總結

在物聯(lián)網(wǎng)、工業(yè)自動化、醫(yī)療系統(tǒng)、消費類設備等廣泛的應用中,開發(fā)人員希望取得高性能、低功耗與安全性之間的平衡。如上所述,LPC55S6x 系列微控制器兼有功能強大的通用內核與專用硬件和處理引擎,讓開發(fā)人員能夠更輕松地滿足高性能專用功能的需求,同時保持低功耗。

本系列文章第 2 部分介紹如何使用 LPC55S6x 系列來管理器件的全生命周期安全性。

-

ARM

+關注

關注

134文章

9111瀏覽量

368032 -

物聯(lián)網(wǎng)

+關注

關注

2910文章

44778瀏覽量

374676

發(fā)布評論請先 登錄

相關推薦

MAX32675C超低功耗Arm? Cortex?-M4F MCU

兆易創(chuàng)新推出基于Arm Cortex-M33內核的GD32G5系列高性能微控制器

樹莓派Pico 2發(fā)布,搭載RP2350雙核RISC-V和Arm Cortex-M33微控制器!

請問Matter Android APP是否支持連接市面上的Matter設備?

求助:現(xiàn)在市面上有成熟穩(wěn)定貨源的8k分辨率CMOS嗎?

市面上很火的32位單片機—PY32F030單片機的產品特性介紹

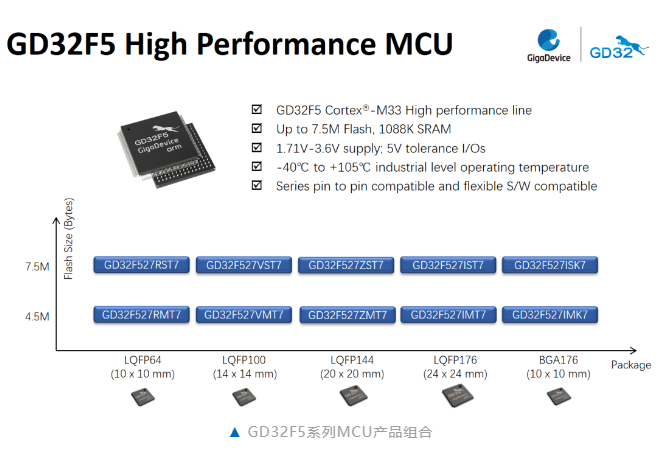

兆易創(chuàng)新推出GD32F5系列Cortex-M33內核MCU

兆易創(chuàng)新推出GD32F5系列Cortex?-M33內核MCU,提供工業(yè)高性能應用新選擇

兆易創(chuàng)新推出GD32F5系列Cortex?-M33內核MCU

兆易創(chuàng)新推出基于Arm? Cortex?-M33內核的GD32F5系列高性能微控制器

業(yè)界首款基于Arm Cortex-M85處理器的MCU

ARM?Cortex?-M23 32位MCU數(shù)據(jù)表

使用市面上首款基于 Arm? Cortex?-M33 的 MCU – 第 1 部分:管理功耗與性能

使用市面上首款基于 Arm? Cortex?-M33 的 MCU – 第 1 部分:管理功耗與性能

評論