針對數字有源EMI濾波器(DAEF)信號檢測點與注入點的耦合會降低EMI抑制性能問題,本文通過建立含有解耦電路的DAEF模型,仿真分析解耦電路對濾波特性的影響,提出一種DAEF系統解耦電路的設計方法。該方法基于實測阻抗匹配原則,在不改變原電路結構,不增加DAEF體積的前提下,大幅度提高了DAEF系統EMI抑制能力。對消技術可有效降低開關電源工作中產生的傳導EMI。本文基于FPGA控制器搭建了含有解耦電路的DAEF控制系統平臺,利用R&S公司的EMI接收機實驗測試EMI,仿真及實驗結果表明本文提出的解耦電路設計方法有效地提高了DAEF的濾波能力。

Abstract:Aiming at the problem that the coupling between EMI signal detection point and injection point in digital active EMI filter (DAEF) reduces EMI suppression performance, this paper presents a design method about decoupling circuit in DAEF system through building DAEF model with decoupling circuit and analyzing effect of the decoupling circuit on filter characteristics. Based on real tested impedance matching principle, and no changing original circuit structure and no increasing the volume of DAEF, this method greatly improves DAEF system EMI suppression performance. This paper builds a DAEF control system with decoupling circuit based on FPGA controller. Experiments results show that the proposed method effectively improves the filtering performance of DAEF.

Key words: Electro-Magnetic Interference, EMI filter, filter performance, decouple, impedance matching

1. 引言

開關功率變換器的高頻化使得其產生的高頻傳導EMI噪聲越來越嚴重,為保證電子設備的正常工作,國標GB/T 21419-2013規定了傳導EMI信號在0.15 MHz~30 MHz頻率范圍內的允許發射限值[1]。

傳導EMI的一般抑制方法是在變換器前端加EMI濾波器。模擬無源EMI濾波器 (Passive EMI Filter,PEF) 電路拓撲簡單,運行可靠[2],但其體積和損耗較大、濾波靈活性差。模擬有源EMI濾波器 (Active EMI Filter, AEF) 克服了PEF靈活性差的缺點,但由于速度、功率損耗和增益帶寬的限制,在抑制高頻噪聲或強噪聲電流方面能力不強[3]。進而出現了PEF與AEF相結合的混合模擬有源EMI濾波器 (Hybrid Active EMI filter, HAEF) [3,4],但其寬頻率范圍內的抑制效果不佳,另外清除運算放大器的偏置電壓問題還有待解決。這些技術未從根本上解決EMI濾波器的體積和功耗問題。

隨著FPGA的廣泛發展,A/D轉換速度和精度的大幅提高,加上數字處理器成本不斷降低,使得數字有源EMI濾波器(Digital Active EMI Filter, DAEF) 實際應用成為可能 [5,6]。DAEF因不在主電路中串聯器件,所以從根本上解決了EMI濾波器體積和功耗問題,且不受功率與電流的限制,但該方法中EMI信號的檢測和注入點存在耦合,這個耦合會使得DAEF的濾波性能降級。

本文對DAEF系統中EMI信號檢測與注入點的耦合作用進行仿真分析,提出一種解耦電路的設計方法,解決了這種耦合帶來DAEF濾波性能降級的問題。

2. DAEF系統的設計及建模分析

2.1 DAEF的拓撲及原理

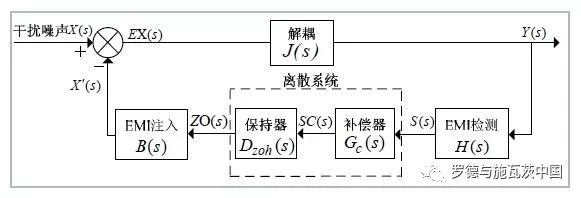

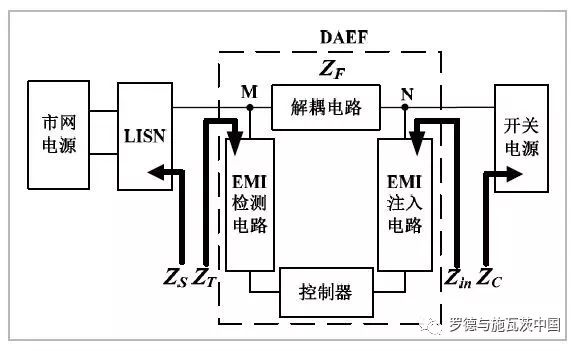

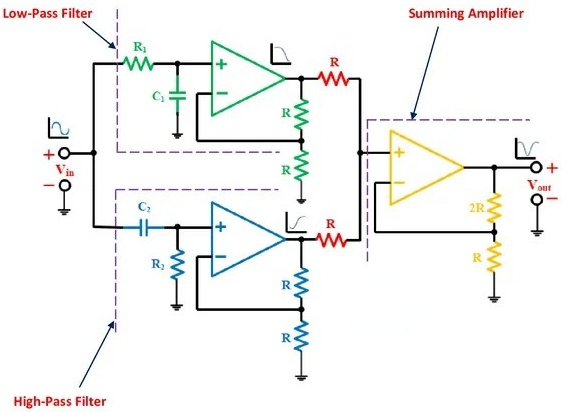

抑制共模EMI是開關功率變換器傳導EMI抑制的主要任務,在低壓交流電源端口的共模EMI電壓為L線與N線對地EMI電壓的平均值,減小其中任何一個均可減小共模傳導EMI,由于兩個信號在傳輸和抑制機理上相同,本文僅以抑制L線對地的傳導EMI信號為例說明該方法。L線上DAEF抑制傳導EMI的原理圖如圖1所示,DAEF系統包括EMI信號檢測電路和注入電路、ADC采樣、數字控制器、DAC輸出和解耦電路6部分。

圖1 DAEF系統應用原理框圖

EMI信號檢測電路由電阻RS和電容CS構成的高通濾波器實現,提取功率變換器在L線上產生的高頻傳導EMI信號;ADC將檢測的EMI信號進行采樣,得到相應的數字EMI信號;控制器對數字EMI信號進行EMI補償控制,這里的控制器最好采用硬件描述語言編程和并行處理的FPGA;DAC把控制處理后的數字EMI信號轉化為輸出能力為0~20 mA的模擬EMI電流信號,該電流信號可以抑制86 dBμA (120 dBμV)的EMI信號。EMI信號注入電路是電阻Ri和電容Ci構成的低通濾波器,一方面把0~20 mA的模擬EMI電流信號注入到功率變換器輸入端以消除其產生的EMI噪聲,一方面利用電容Ci有效防止電源線上低頻功率電流對DAC輸出端口的損壞。 LD為檢測和注入點之間的解耦電路。

2.2 DAEF的EMI控制方案

DAEF檢測電源線L對地的傳導EMI信號,經A/D轉換采樣、控制器補償處理和D/A模擬輸出,最后經注入電路注入到功率變換器的輸入側,形成一個閉環控制系統,其控制框圖如圖2所示,控制目標為使得沿L線傳入供電電源的EMI信號Y(s)最小,即Y(s)=0。

圖2 DAEF系統控制框圖

圖2中,H(s)為EMI檢測電路的傳遞函數,補償器GC(s)為補償控制算法的傳遞函數,Dzoh(s)為保持器的傳遞函數,B(s)為EMI注入電路的傳遞函數,J(s)為解耦電路的傳遞函數,Y(s)為經濾波之后的噪聲信號;X(s)為功率變換器產生的未經濾波的EMI信號,X'(s)為經控制器處理后產生的反相補償EMI注入信號。理想狀況下,功率變換器產生的EMI信號X(s)和補償注入的EMI信號X'(s)幅值相等、相位相反,相互抵消,實現抑制傳導EMI的作用。

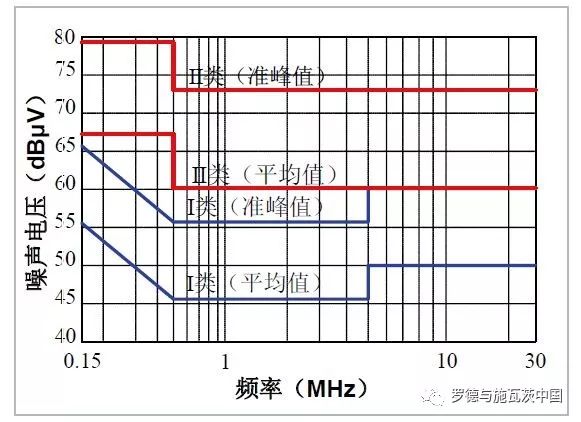

國標GB/T 21419-2013規定了低壓交流端口傳導EMI發射頻率范圍為0.15 MHz~30 MHz,如圖3所示。因此提取EMI信號的RC高通濾波器的截止頻率需在0.15 MHz以下;注入EMI信號的RC低通濾波器的截止頻率需在30 MHz以上。

圖3 GB/T 21419-2013規定的低壓交流端口傳導EMI發射限值

2.3 DAEF系統建模與分析

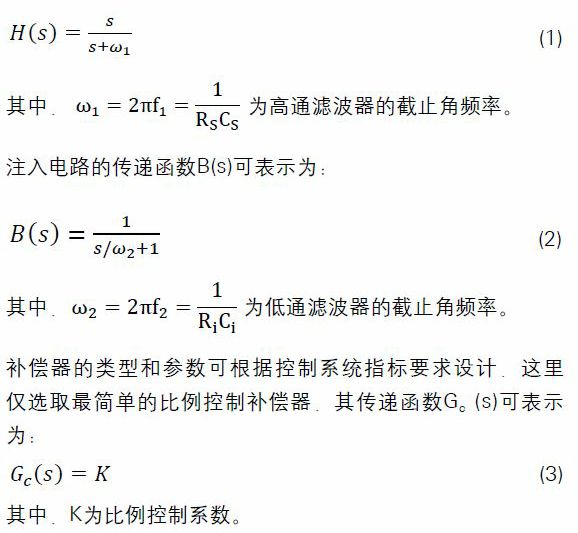

EMI檢測電路的傳遞函數H(s)可表示為:

解耦電路可以等效為一個高阻抗解耦電感LD,其傳遞函數J(s)可表示為:

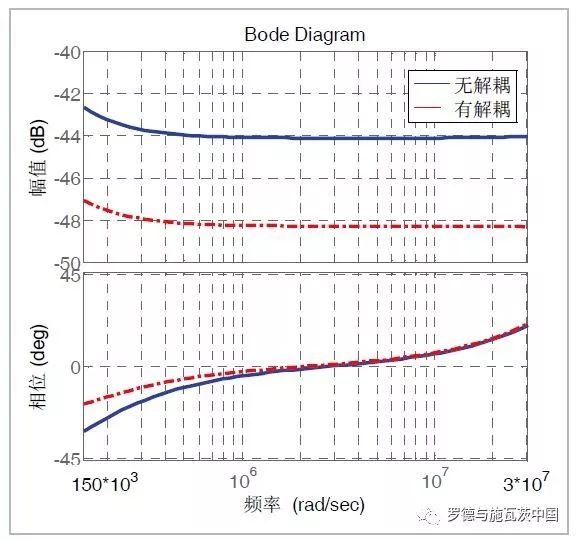

補償器選純比例補償增益為100的情況下,對有解耦電路(J(s)=5.4×10-7s) 和無解耦電路(J(s)=1)時閉環DAEF控制系統進行仿真分析,得出其頻率響應曲線如圖4所示。

圖4 DAEF系統頻率響應曲線圖

由圖4可知,在0.15 MHz~30 MHz頻率范圍內,無解耦電路時DAEF的抑制能力僅在-44 dB,但是如果加入解耦電路DAEF的抑制能力達到了-48.3 dB,提高了4.3 dB。

3. 解耦電路的設計

在EMI信號檢測電路和注入電路之間,傳統方法為加入繞線式電感解耦,但這會增加EMI濾波器體積和功耗。本文提出一種在不改變原電路形式及結構的前提下,采用單匝電感作為解耦電路的方法。該單匝電感的磁芯材質、頻率阻抗曲線和尺寸是該設計方法的重點。

3.1 解耦電感磁芯材料設計

由于鎳鋅鐵氧體對于高頻段的電磁干擾有很好的抑制作用,因此,本文選用鎳鋅鐵氧體作為解耦電感的磁芯材料,該磁芯根據NiO與ZnO含量可工作在100 kHz~140 MHz頻率之內。

在鎳鋅鐵氧體中,NiO與ZnO的含量與鎳鋅鐵氧體工作上限截止頻率及相對磁導率μr有直接關系,鎳鋅鐵氧體常用的配比如表1所示。

表1 鎳鋅鐵氧體配比與截止頻率的關系

由于傳導EMI頻率范圍要求在0.15 MHz~30 MHz,所以選擇上限截止頻率為30 MHz的鎳鋅鐵氧體配比:Fe2O3ZnO=50.224.9,所以鎳鋅鐵氧體的相對磁導率μr為150。

3.2 解耦電感阻抗曲線設計

解耦電感的設計需要先確定其頻率阻抗曲線范圍,其次根據阻抗曲線進一步確定解耦電感的尺寸規格。

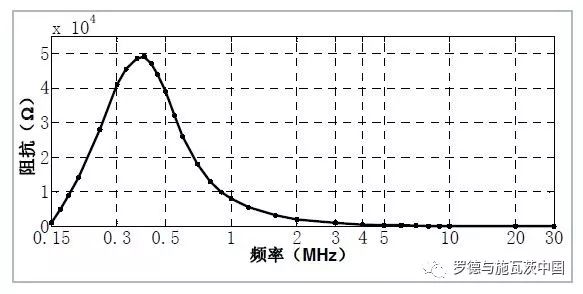

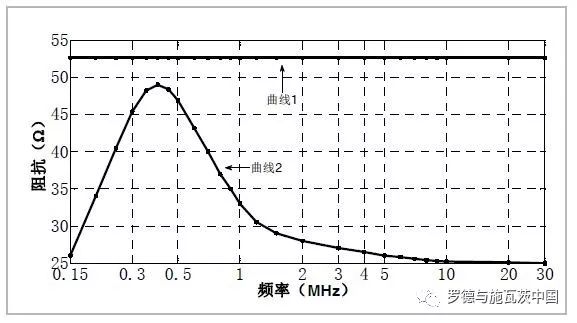

DAEF系統的等效阻抗電路如圖5所示,其中ZS為從檢測點M向市網電源端看的對地電源等效阻抗,由于LISN阻抗在0.15 MHz~30 MHz全頻段穩定在50Ω,所以ZS在全頻段滿足ZS≈50Ω;ZT為從檢測點M向EMI檢測電路方向看的對地等效阻抗,在高頻情況下電容可視作短路,所以ZT等效為RS;Zin為從注入點N向EMI注入電路看的對地等效阻抗,在高頻情況下, Zin可等效為Ri; ZC為開關電源的對地等效內阻抗曲線,由雙電流探頭測試法得到[7],某品牌筆記本供電電源L線對地阻抗測量曲線如圖6所示。

圖5 DAEF系統等效阻抗電路圖

圖6 筆記本電腦供電電源L線對地阻抗測試曲線

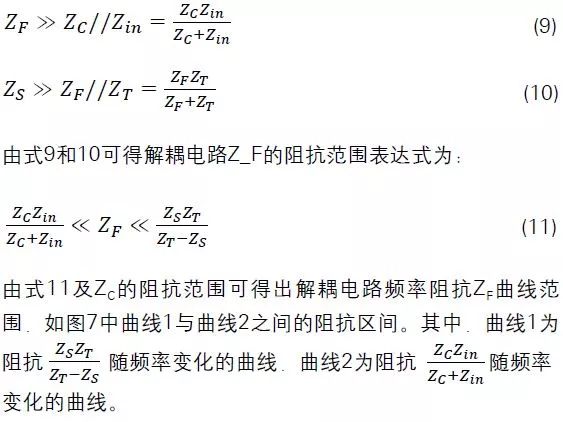

由于ZF在全頻段內應對從開關電源即噪聲源流出的EMI信號呈現高阻抗,所以ZF的阻抗應遠遠大于從注入點N向EMI注入電路與開關電源并聯反向看的對地等效阻抗,即滿足式9;由于電源等效阻抗ZS應對流入LISN的EMI信號呈現高阻抗,所以ZS在全頻段內應遠遠大于從檢測點M向EMI檢測電路與解耦電路并聯方向看的對地等效阻抗,即滿足式10。

圖7 解耦電路阻抗Z_F的取值范圍

3.3 解耦電感尺寸的設計

單匝電感的電感值與其內、外徑及長度的關系為:

根據圖7,可選取解耦電感在0.15 MHz~30 MHz頻率范圍內阻抗為50Ω。由于|ZF|=2πfL,f取中間頻率15 MHz,可算出電感值為0.54 μH。由式13和D/d=1.67及h/d=0.67可計算出解耦單匝電感的尺寸規格為:D=14.31mm,h=5.74mm,d=8.57mm。

4. 實驗驗證

基于FPGA控制器建立DAEF控制器參數如下:

A/D轉換器:14 bits,250 MSPS;

D/A轉換器:14 bits,260 MSPS;

檢測電路:Rs=1kΩ,Cs=0.1 μF;

注入電路:Ri=30Ω,Ci=1nF。

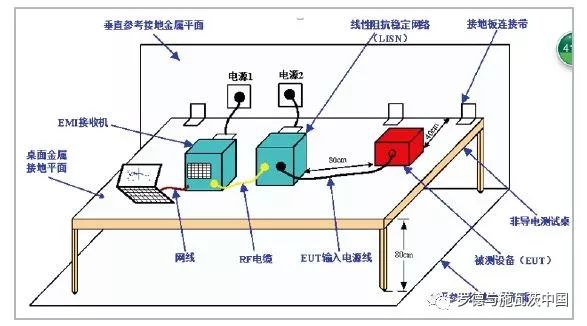

基于R&S公司的EMI接收機和線性阻抗穩定網絡建立傳導EMI測試平臺如圖8所示。測試平臺設備型號及建立參數如下:

筆記本:華碩S550C

EMI接收機:R&S ESL3

LISN: ENV216 TWO-LISN V-NETWORK

被測設備:開關電源+DAEF

非導電測試桌:桌子高度0.8米,金屬板厚2毫米,寬度為0.7米,長度為1.6米

垂直參考接地金屬平面:鋁金屬板2毫米,水平寬度為1.6米,垂直長度為2米

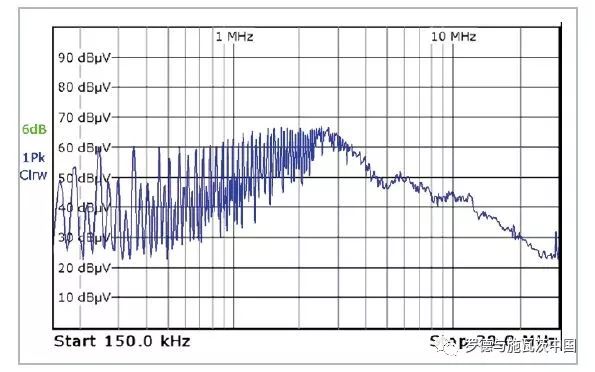

A/D轉換器和D/A轉換器均是高速、高采樣率的器件,采用FPGA實現對數字EMI信號補償控制處理。無EMI濾波器時,筆記本電腦供電電源L線對地傳導EMI信號的頻譜圖如圖9所示。

圖8 EMI實驗測量平臺原理圖

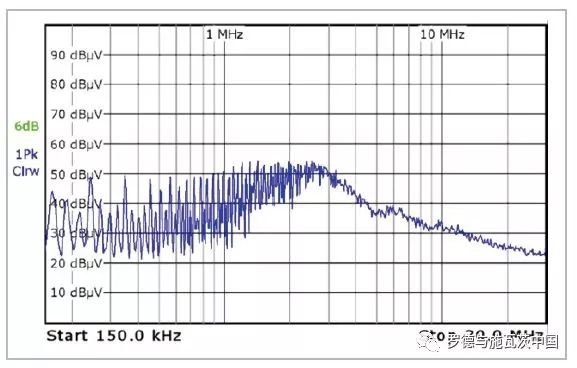

圖9 無EMI濾波時L線對地傳導EMI頻譜圖

從圖9中可以看出,在不加EMI濾波器時,在0.5 MHz~5 MHz頻段EMI噪聲信號平均值約為55 dBμV,超過了國標限值46 dBμV。

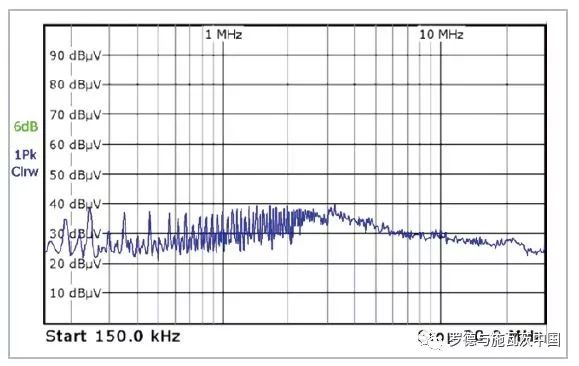

當用沒有解耦電路的DAEF濾波時,筆記本電腦供電電源L線對地傳導EMI信號的頻譜圖如圖10所示。

圖10 無解耦電路的DAEF濾波時L線對地傳導EMI信號頻譜圖

由圖10可知,采用無解耦的DAEF濾波時,L線對地的EMI得到抑制,均小于國標限值,采用DAEF達到了EMI濾波的目的。

當用有解耦電路的DAEF濾波時,筆記本電腦供電電源L線對地傳導EMI信號的頻譜圖如圖11所示。

圖11 有解耦電路DAEF濾波L線對地傳導EMI頻譜圖

由上圖11可知,在采用了有解耦電路的DAEF后,濾波效果不僅能達到國標限值,并且比沒有解耦電路時濾波效果降低了5~10 dBμV。

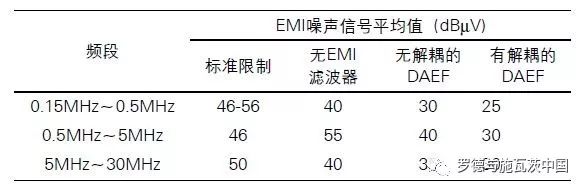

把無EMI濾波、無解耦的DAEF濾波、有解耦的DAEF濾波與國標限值對比如表2。

表2 各頻段EMI噪聲信號平均值

由表2可看出,DAEF對傳導EMI有很好的抑制效果,DAEF的解耦電路有效的提高了DAEF的抑制能力,與仿真結果一致。

5. 結束語

本文針對DAEF系統信號檢測點與注入點的耦合會降低EMI抑制性能問題,設計了帶有解耦電路的DAEF系統及控制方案,建立了帶有解耦電路的DAEF系統的模型,仿真分析了解耦電路對DAEF系統濾波性能的影響,給出了解耦電路的設計方法。利用R&S公司的EMI接收機實驗測試EMI,基于FPGA搭建了DAEF控制系統平臺,實驗證明所提出的解耦電路設計方法有效的提高了DAEF的抑制能力,這將有效促進對數字有源EMI濾波器的進一步研究和廣泛推廣。

-

檢測電路

+關注

關注

13文章

308瀏覽量

58198 -

轉換器

+關注

關注

27文章

8728瀏覽量

147446 -

濾波器

+關注

關注

161文章

7846瀏覽量

178413

發布評論請先 登錄

相關推薦

有源陷波濾波器的定義和工作原理

關于數字有源EMI濾波器解耦電路的設計方法的介紹和研究

關于數字有源EMI濾波器解耦電路的設計方法的介紹和研究

評論