Q:我在PLL設計中使用+12/-5V電源運行此元件(AD8610)。現在我發現使用+12和0V也運行得很好(不管規格是什么)。不知我這樣使用此元件會遇到哪些問題?(規格為最小+5/-5V)

A:運算放大器沒有接地端子。可以由對稱或不對稱雙電源供電,也可由單電源供電。

就電源工作范圍而言,+12/-5V的供電電壓類似于+17/0V或+8.5/-8.5V。因此,+12/-5V供電在AD8610的工作電壓范圍內。AD8610是JFET輸入運算放大器,這意味著它不是軌到軌輸入。由于輸出也不是軌到軌,因此請密切留意數據手冊“電氣規格”部分中,表2(Vs=+/-13V)的輸入和輸出電壓范圍規格。

請記住,輸入電壓范圍和輸出電壓范圍的規格作為絕對電壓列出,但對于+12/-5V的供電而言,需要類比+/-13V供電,保留電軌余量(2.25至2.5V)。

此外,參考電平會從地電壓移動到供電電壓范圍的中心。因此,對于+12V/-5V的供電電壓,參考電平上升到+3.5V,而對稱雙電源(如+/-5V或+/-13V)為0V。

2、如何防止過壓?

Q:對于如AD8646這樣的運算放大器,如何防止過壓?

A:通常,建議您在任何可能超過絕對最大額定值的輸入端添加外部肖特基二極管和限流電阻。請注意,二極管需要安裝在AD8646的附近。理想情況下,您的系統應設計為確保AD8646在施加任何模擬或數字信號之前能充分上電。下面概括了一些關于過壓的一般注意事項。

任何其他半導體IC都有基本的ESD保護二極管,用來保護器件免遭運輸和生產過程中可能造成的ESD損害。如果輸入隨時可能超過電源,設計人員應提供外部保護電路。

這些ESD二極管可保護IC免受高達約1.5kV的ESD影響。這些ESD保護二極管的作用是將任何引腳上的電壓箝位在與電源電壓相差0.5V的范圍內。(所以問題解決了,對吧?不完全是。)ESD保護二極管雖然能承載相當高的電流,但只能維持很短的時間,因此可以保護IC免受持續時間較短的大脈沖影響(總能量仍然相當低)。這些保護二極管能承受的最大直流電流為10mA。因此,除非您可以保證流入引腳的電流小于10mA,否則就需要某種外部保護。外部保護可以是在輸入引腳上串聯限流電阻這樣的簡單設計。例如,如果施加到引腳上的最大過壓為5V,則在每條線路上串聯一個500Ω電阻即可將電流限制在10mA以內。此串聯電阻設置得越高越好。

然而,IO線路中的高串聯電阻可能導致其他問題,例如延長高速信號的上升和下降時間。如果在防止更高過壓的同時又不想再增加串聯電阻,該怎么做呢?可以在每個輸入端和供電之間添加外部肖特基二極管來做到這一點。肖特基二極管會將施加的電壓箝位在電源的~0.3V范圍內,因此大部分電流將通過外部二極管(可承載更高電流)分流,而不通過內部ESD保護二極管。其他保護技術包括使用火花隙、接地大電容、小扼流圈電感等。防止過壓和ESD的最佳結構之一是一個小串聯電阻,后面是連接到電源的肖特基二極管,再后面是另一個小串聯電阻。

可見,設計合適的保護電路并不是一件容易的事情。您需要決定所需的保護程度、系統可承受的受損程度、所允許的電路板空間和元件成本,以及需要達到的測試水平。

3、如何解釋放大器的負載電流規格?

Q:我的問題是關于放大器的負載電流。

這個值的確切含義是什么?在數據手冊中,有時給出的是+-10mA,有時又只寫成10mA。

此負載電流是指放大器可以提供的最大輸出電流嗎?比如說,我的放大器在輸出端為+-4Vp。如果數據手冊中給出+-10mA負載電流,是不是就是說只能在4V/10mA=400 Ω的最小負載時使用?我說的對嗎?

A:放大器通常具有短路保護,可限制流出輸出端的電流。通常在短路情況下會觸發這種保護,以防止損壞放大器。但是,這并非是嚴格控制的參數,且未經生產測試。它隨溫度變化而變化,有時也因低電壓供電軌而異,放大器甚至可能由于低供電電壓的內部限制,而無法提供這種電流電平。不管規格中是否有+/-,都是一樣的。但是,這并不意味著兩個極性的實際限值會一樣。沒有一個輸出級是完全對稱的,但是由于它不是一個精確的數字,因此沒有那么重要。

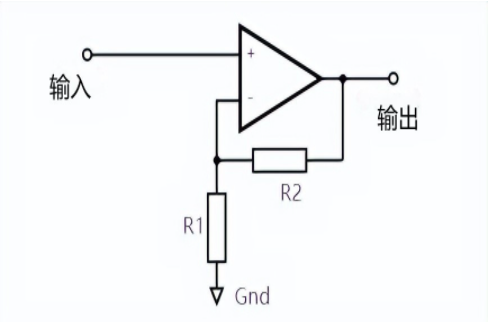

您指出放大器的最小負載將根據您的計算給出,這點是正確的,但只能將其作為指導。對最小負載保持合理的余量是比較好的做法(出于上述所有原因)。此外,不要忘記,如果您使用的是帶反饋的運算放大器(如同相放大器),則反饋電阻也是負載的一部分。還要謹記,在負載更重時,放大器會產生更大的功耗,從而提高芯片溫度。在您舉的例子中,4V輸出端為10mA是指,如果您使用15V為放大器供電,則放大器會額外消耗11V*10mA=110mW,這會使溫度(如果是SOIC)上升約15℃。這不是大問題,但會限制放大器的工作溫度范圍,并且也可能增加與輸入有關的偏置。然而,有些放大器可能具有更大的電流驅動能力,因此,如果加載至限值,功耗會大得多。

4、使用高阻抗源時的噪聲考慮因素是什么?

Q:使用具有高阻抗源的ADA4661-2/ADA4666-2時的噪聲考慮因素是什么?

A:ADA4661-2/ADA4666-2在10KHz時具有14nV/√Hz的低電壓噪聲密度。在放大器輸入端放置一個熱噪聲為12.6nV/√Hz的10K?電阻,會使折合到輸入端的總噪聲增加到18.9nV/rtHz。使用較低的源電阻時,放大器電壓噪聲將占主導地位。電阻熱噪聲隨著源電阻的提高而增加。當源電阻進一步提高時(>1M?),電流噪聲會占總噪聲的大部分。

5、哪種電阻值可用于低噪聲應用?

Q:放大器ADA4528-x周圍應使用哪些電阻值?

A:ADA4528-x的低電壓噪聲密度為5.6nV/√Hz。在放大器輸入端放置一個熱噪聲為4nV/√Hz的1K?電阻,會使折合到輸入端的總噪聲增加到6.9nV/√Hz。請務必在低噪聲放大器周圍使用低值電阻。使用低源電阻,放大器電壓噪聲將占主導地位。電阻熱噪聲隨著源電阻的提高而增加。當源電阻進一步提高時(>100K?),放大器電流噪聲會成為總輸入噪聲的主要因素。

Q:放大器ADA4500周圍應使用哪些電阻值?

A:ADA4500的低電壓噪聲密度為14.5nV/√Hz。在放大器輸入端放置一個熱噪聲為4nV/√Hz的1K?電阻,會使折合到輸入端的總噪聲增加到15nV/√Hz。在輸入端放置4k?電阻會將總噪聲增加到21.6nV/√Hz。請務必在低噪聲放大器周圍使用低值電阻。

6、單電源使用時的輸出擺幅

Q:如果在AD817運算放大器上使用+5V和0V的供電軌,輸出擺幅是否會下降到0V?

A:供電軌的輸出余量要求是距離供電軌最大電壓為1.8V,因此使用0V作為VE電軌可能僅允許您擺動到1.8V。擺幅要下降到零,需要+/-5V雙電源。

7、放大器的容性負載驅動

Q:規格表指出,ADA4807-2的容性負載驅動為15pF。ADA4807-2能否驅動更大的電容負載?這種大的容性負載是否會使放大器不穩定?

A:ADA4807-2可以驅動更大的電容負載。容性負載會對放大器的傳輸函數增加一個額外極點,這在很多情況下可能會影響穩定性。在這種情況下保持穩定性的常見方法是在放大器輸出和容性負載之間添加一個串聯電阻。對于大電容來說要提供一個串聯小電阻,例如如果使用10uF電容,由于該電容比較大,所以有該電容的PCB走線電阻和ESR需要足夠的串聯電阻來保持放大器的穩定。

-

電容

+關注

關注

100文章

6073瀏覽量

150640 -

運算放大器

+關注

關注

215文章

4959瀏覽量

173238 -

驅動

+關注

關注

12文章

1844瀏覽量

85406

發布評論請先 登錄

相關推薦

高速運算放大器的應用場景 運算放大器電路中的反饋機制

運算放大器的輸入輸出特性 運算放大器的噪聲分析與抑制

常見運算放大器型號及其特點

線性運算放大器和非線性運算放大器的區別

運算放大器在音頻處理中的應用

運算放大器和普通放大器的區別

運算放大器的基本原理 運算放大器的應用實例

同相運算放大器的應用場景

簡述運算放大器的失調電壓

運算放大器的輸入電阻怎么算

運算放大器和儀表放大器的區別

什么是理想的運算放大器?運算放大器的基本應用

公式+案例 搞定同相運算放大器

關于運算放大器常見問題分析和解答

關于運算放大器常見問題分析和解答

評論