HDL Coder 利用 MATLAB 函數、Simulink 模型和 Stateflow 圖生成可移植、可綜合的 Verilog 和 VHDL 代碼。生成的 HDL 代碼可用于 FPGA 編程或 ASIC 原型開發和設計。

HDL Coder 提供了一個 Workflow Advisor,可以自動執行 Xilinx 和 Altera FPGA 編程。您可以控制 HDL 架構和實施、突出顯示關鍵路徑,并估算硬件資源利用率。HDL Coder 在 Simulink 模型與生成的 Verilog 和 VHDL 代碼之間提供了可追溯性,使高完整性應用程序的代碼驗證遵守 DO-254 和其他標準。

主要特性

獨立于目標的、可綜合的 VHDL 和 Verilog 代碼

代碼生成支持MATLAB 函數、系統對象以及 Simulink 模塊

使用 Stateflow 實施 Mealy 和 Moore 有限狀態機以及控制邏輯

用于 Xilinx 和 Altera 應用程序面板編程的 Workflow Advisor

資源共享和重定時,用以平衡面積速度

符合 DO-254 的代碼到模型和模型到代碼可追溯性

舊有代碼集成

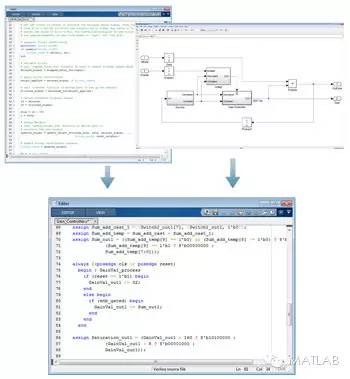

使用 HDL Coder 從 MATLAB 或 Simulink 生成 HDL 代碼。您可以使用 MATLAB 函數、Simulink 模型或將兩者結合使用來生成可綜合的 VHDL 和 Verilog 代碼。

主要功能

1.生成HDL代碼

使用 HDL Coder,只需幾個步驟便可為 FPGA 和 ASIC 實施生成可綜合的 HDL 代碼:

將 MATLAB 代碼、Simulink 模塊和 Stateflow 圖組合使用,進行設計建模。

優化模型以滿足面積速度設計目標。

使用為 MATLAB 和 Simulink 集成的 HDL Workflow Advisor 生成 HDL 代碼。

使用 HDL Verifier 驗證生成的代碼。

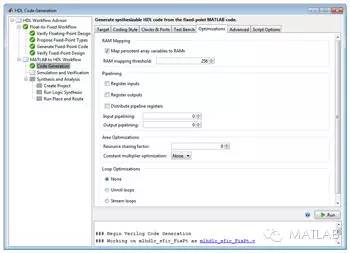

2.優化 HDL 代碼

在 MATLAB 或 Simulink 中,通過采用分布式流水線、流式處理和資源共享,可以優化 HDL 代碼以實現速度面積目標。在 MATLAB 中,您可以使用高級循環優化,如循環流和循環展開,用于包含 for 循環或矩陣運算的 MATLAB 設計。您可以將 MATLAB 代碼中的持續陣列或矩陣變量映射到 Block RAM。在 Simulink 中,您可以實施信號處理和多媒體應用中常用的多聲道設計和序列化技術。

適用于 MATLAB 的 HDL Workflow Advisor 提供了多個優化選項,如 RAM 映射、流水線、資源共享和循環展開

面積速度優化。用一個乘法器取代四個乘法器,降低了設計面積成本,數據率提升4倍。

3. FPGA 設計自動化

HDL 中的 HDL Workflow Advisor 可以自動執行將 MATLAB 算法和 Simulink 模型實施到 Xilinx 和 Altera FPGA 的工作流程。HDL Workflow Advisor 集成了 FPGA 設計流程的所有步驟,包括:

檢查 Simulink 模型的 HDL 代碼生成兼容性

生成 HDL 代碼、HDL 測試工作臺和協同仿真模型

通過與 Xilinx ISE 和 Altera Quartus II 集成,執行合成和時序分析

估算設計中的資源使用

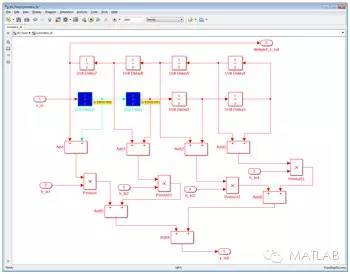

使用關鍵路徑時序回注 Simulink 模型

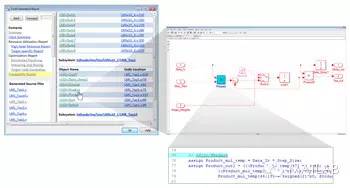

使用關鍵路徑時序回注 Simulink 模型。HDL Workflow Advisor 會在 Simulink 中突出顯示關鍵路徑時序,以幫助識別速度瓶頸并提高設計性能。

您可以查看合成后時序報告并回注 Simulink 模型,以識別時序約束瓶頸。與合成工具的這一集成實現了快速設計迭代,并顯著縮短了 FPGA 設計周期時間。

4.驗證 HDL 代碼

HDL Coder 可以生成 VHDL 和 Verilog 測試工作臺以快速驗證生成的 HDL 代碼。您可以使用各種選項自定義 HDL 測試工作臺,測試HDL 代碼。您還可以生成腳本文件,在 HDL 仿真器中自動處理代碼編譯和仿真。

HDL Coder 與 HDL Verifier 配套使用,可以自動生成兩類協同仿真模型:

HDL 協同仿真模型,用于使用 Simulink 和 HDL 仿真器(如 Cadence Incisive 或 Mentor Graphics ModelSim 和 Questa)執行 HDL 協同仿真

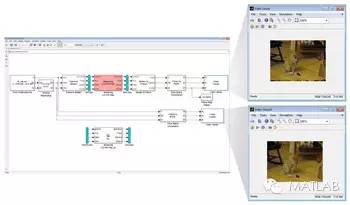

FPGA 在環 (FIL) 協同仿真模型,用于使用 Simulink 和 FPGA 板驗證設計

自動生成 FPGA 在環 (FIL) 模型,用于視頻銳化。FIL 仿真可以在硬件上高效地執行設計空間探查。

5. 記錄和追蹤HDL 代碼

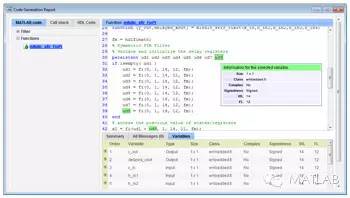

HDL Coder 會將生成的代碼記錄在 HTML 報告中,該報告包括帶超鏈接 的HDL 代碼和生成的 HDL 文件表。通過 HDL 代碼中的超鏈接,可以導航到與代碼對應的 MATLAB 算法或 Simulink 模塊。

為滿足 DO-254 等標準對高完整性應用程序的代碼可追溯性要求,HDL Coder 讓您能夠執行以下操作:

從生成的 HDL 代碼導航到 MATLAB 代碼

在 Simulink 模塊與生成的 HDL 代碼之間導航,實現雙向追蹤

插入用戶注釋和描述,增加代碼可讀性

MATLAB 中的代碼生成報告,使您可以從生成的 VHDL 和 Verilog 代碼導航到 MATLAB 代碼。

將 Simulink Verification and Validation 與 HDL Coder 搭配使用,可以將系統需求作為注釋嵌入到從 Simulink 或 Stateflow 生成的 HDL 代碼中。這樣,您便可以使整個工作流程完全透明,包括從系統需求到生成的 HDL 代碼。

Simulink 中的 HDL 代碼生成報告,使您可以在模型與生成的 HDL 代碼之間導航。

6.HDL 編碼標準

用于工業 FPGA 和 ASIC 應用(如航空航天工業中的 DO-254)的開發過程可能建議使用特定的 RTL 編碼指南。HDL Coder 旨在生成滿足通用行業編碼指南(如 RMM 和 STARC)的 VHDL 和 Verilog 代碼。HDL Coder 還可生成報告,幫助您確定 Simulink 模型和 MATLAB 代碼中不合適的結構,這樣您可以調整您的模型,使生成的 RTL 符合這些編碼指南。

HDL Coder 還可以生成第三方 lint 工具腳本,用于檢查您生成的 HDL 代碼。HDL Coder 自動生成的代碼可通過多種行業標準的 lint 工具的檢查,例如Atrenta SpyGlass, Real Intent Ascent Lint, Synopsys Leda, 和 Mentor Graphics HDL Designer。HDL Coder 可生成允許與任何 lint 工具集成的自定義腳本。

使用 HDL Coder 生成的代碼遵循 RTL 編碼原則,通過:

避免 FSM 狀態可訪問性和編碼問題

避免仿真和綜合語義之間的差異

避免在實現代價高昂的操作

避免下游工具流問題

遵循命名規則和RTL編碼習慣

強 RTL 建模的清晰度并降低復雜性

增強對時鐘資源(時鐘、啟用、復位)和控制信號的檢查

支持代碼的可測性和可追溯性

-

編碼

+關注

關注

6文章

942瀏覽量

54829 -

代碼

+關注

關注

30文章

4788瀏覽量

68612 -

腳本

+關注

關注

1文章

389瀏覽量

14865

發布評論請先 登錄

相關推薦

Verilog 與 ASIC 設計的關系 Verilog 代碼優化技巧

Verilog 測試平臺設計方法 Verilog FPGA開發指南

Verilog與VHDL的比較 Verilog HDL編程技巧

FPGA與ASIC的區別 FPGA性能優化技巧

Verilog vhdl fpga

怎么樣提高verilog代碼編寫水平?

FPGA Verilog HDL代碼如何debug?

FPGA芯片架構和資源有深入的理解,精通Verilog HDL、VHDL

FPGA Verilog HDL有什么奇技巧?

【招聘】verilog vhdl FPGA

Verilog到VHDL轉換的經驗與技巧總結

關于為FPGA和ASIC生成Verilog和VHDL代碼分析和應用介紹

關于為FPGA和ASIC生成Verilog和VHDL代碼分析和應用介紹

評論