與幾年前相比,這些SoC中的模擬/混合信號(AMS)內容和交互要多得多。為了避免錯誤和重新旋轉,有必要實現模擬IP和子系統的良好參數覆蓋,以便不會遺漏角落情況。

因此,精心制作的預硅片AMS驗證混合信號SoC中的模擬子系統是必需的,但是這種模擬可以非常長時間運行,即使在沒有完整SoC的情況下也是如此。基于命令行的SoC AMS仿真(其中設計采用RTL和SPICE)是普遍的。隨著SoC中模擬和混合信號組件的集成度和復雜性的增加,在實際的時間限制內實現這種詳盡的仿真和越來越多的驗證測試用例變得越來越不可行。

當前方法

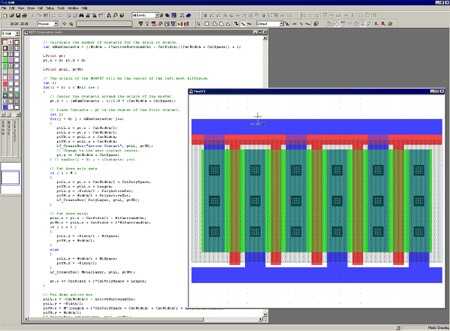

當前方法如圖1所示:

圖。 1傳統方法

是的,有一種回歸技術。但所有這些都是目前的手工努力。事實上,我們可以說它們容易出現人為錯誤。此外,還有許多工具可用于最終生成可分析的圖形輸出。這種方法(見上面的圖1)非常繁瑣,既不是用戶友好的,也是手動干預使其很容易出錯。這通常會限制驗證范圍。

同樣在當前的方法中,后期運行數據分析必須通過不同的圖形繪制和后分析工具分別處理,這使得它成為一項繁瑣的任務。

建議的方法論

為了克服所有這些困難,肯定需要自動回歸以及一些可以接受參數化的技術輸入然后自動觸發并行設置。一個這樣的電源啟用工具是Cadence的ADE-XL。

自動回歸- 我們遵循的自動回歸方法基于以下幾點:

在Cadence的Virtuoso中定義參數化混合信號測試平臺。

使用ADE-XL使用單個按鈕在指定的參數范圍內啟動回歸:Go!

模擬后綜合結果分析

利用ADE-XL ViVA的內部功能及其與自定義腳本的兼容性來分析結果摘要,只產生圖形輸出。這使它成為單點解決方案。

目前,業界部署了Cadence的ADE-XL的參數化和掃描功能,以便徹底地運行不同的角落。我們提出了一個新穎的想法(見圖2),從AMS驗證角度灌輸ADE-XL的類似技能。

結果

ADC子系統是混合信號SoC中非常重要的部分,因此需要在AMS環境中進行廣泛的驗證。從需要驗證的時間和詳盡性的角度來看,這是一個問題。線性檢查和噪聲靈敏度是兩個這樣的關注領域。

我們深入研究這兩個例子來看看&感覺上述方法。

通過ADE-XL的ADC噪聲靈敏度

如圖3所示,噪聲靈敏度驗證方法的第一階段是從A-IP的每個端口獲得部分噪聲傳遞函數(p-NTF)到功能輸出。這是通過在功能操作模式下執行A-IP的瞬態分析,同時在不同頻率下在一個輸入端口上注入噪聲來完成的。輸入噪聲頻率范圍應涵蓋整個可能的噪聲源。在SAR-ADC的情況下,輸出頻譜限制在奈奎斯特頻率FN(Fs/2,其中Fs是采樣率)的采樣系統中,選擇輸入噪聲頻率,使得在折回時,它們代表不同的譜線在0Hz到FN的范圍內。為確保小信號假設有效,噪聲幅度應保持足夠低,使得與A-IP操作的大信號偏置點相比,總噪聲包絡看起來很小。對于具有K端口的A-IP(包括一個功能輸出端口),需要K-1瞬態分析來獲得所有p-NTF。

圖3獲得A-IP的p-NTF(左);圖4(a)參數化設置可視化(右)

如圖4(b& c)所示,我們創建了一個完全參數化的設置,其中輸入作為端口和要掃描的頻率,可以通過ADE -XL單擊按鈕來觸發。在這里,我們提供一個自定義參數來掃描頻率和端口,然后設置運行一個詳盡的排列運行所有模擬。下面的圖5顯示了靈敏度的最終結果。

圖。 4(b)ADE-XL噪聲靈敏度參數化方法的實現

圖。 4(c)ADE-XL的運行窗口顯示并行運行。

圖。 5通過并行回歸技術獲得的不同端口的噪聲靈敏度結果

使用ADE-XL進行ADC線性檢查

ADC線性度意味著計算INL (積分非線性)/DNL(差分非線性)ADC。通常要有16個命中/代碼和12位ADC,理想情況下我們需要4096 * 16 = 65536 us的斜坡時間來實現結果(假設總轉換時間為1μs)。這將導致大量仿真時間,因為平均而言,28nm ADC SoC仿真需要大約48小時才能運行1000μs。因此,此設置大約需要1個月的運行時間。

圖6通過ADE-XL進行線性檢查的參數化TB。突出顯示的部分表示參數化。

圖7運行窗口顯示廣義參數和并行運行的矢量值被觸發。

如圖6所示,我們通過提供所需命中數和需要運行的并行運行數來參數化通用測試平臺。一個合理的模擬時間。然后,ADE-XL自動生成具有不同起始和終止斜坡點的所有并行設置(如圖7所示)。這使得設置更加節省時間并且更加普遍。

結論

文章討論了一些困難混合信號驗證工程師面對AMS驗證,以及如何通過Cadence的ADE-XL&它的創新融合,我們提出了一個實用的解決方案。我們通過這種新的定制方法,進行混合信號驗證的一體化單點自動回歸驗證解決方案。這種方法為自動化指定了大量工作,并且有助于在沒有太多用戶參與的情況下對新設計進行新的回歸/詳盡測試。此外,由于其總結的結論表和內置的圖繪制功能,推斷數據也變得容易。使用這些工具和我們提出的方法有助于我們實現四倍的生產率提升,并縮短設置驗證臺所需的手動時間。

-

soc

+關注

關注

38文章

4170瀏覽量

218373 -

PCB打樣

+關注

關注

17文章

2968瀏覽量

21717 -

華強PCB

+關注

關注

8文章

1831瀏覽量

27779 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43059

發布評論請先 登錄

相關推薦

一種基于混合信號技術的汽車電子單芯片設計

混合SOC驗證的挑戰與方法介紹

混合信號 SOC 產品用戶指南

DFT和BIST在SoC設計中的應用

混合信號SoC助力模擬IP發展

混合信號示波器解決方案

Actel的SmartFusion混合信號FPGA開發評估方

混合信號SoC在應用中的設計開發和使用正在增加

混合信號SoC在應用中的設計開發和使用正在增加

評論