IC設計人員非常清楚“兩周到出帶模式”實際上可能持續數月,導致錯過里程碑和失去市場窗口。盡管使用了先進的點工具,但隨著團隊在出帶之前解決信號完整性和時序收斂問題,布局后設計時間也在不斷增加。

修復一個違規通常會導致另一個違規,從而導致看似無窮無盡的不可預測的循環。現在,新的設計規則和技術挑戰在設計融合方面占據主導地位,許多設計師認為IC設計已成為一個不穩定,脆弱的領域。

單程布局布線流程的前納米日已經過去,當設計通常只需要最終的“整形”修正來將數據庫調整為特定的設計規則時。對于130nm以下的設計,規則已經改變。信號完整性問題(如串擾,噪聲和IR降)阻礙了設計到達流片,導致產品交付出現危機點。

今天的典型設計包含數百萬個信號,甚至其中一小部分可能導致數千次無法手動解決或以后處理修補方式解決的違規行為。即使公司使用高級點工具,許多公司也發現他們的結果錯過了目標設計目標。

一些公司試圖通過手動迭代增量分析和ECO修復來解決問題。不幸的是,他們發現在布局后階段的這種迭代通常不會可預測地收斂,因為有太多不相關的違規。會帶來痛苦的經歷。公司不得不在設計質量和周轉時間上妥協,否則就會達到低于其設計規格的性能和面積。

雖然EDA工具可用于分析設計并識別SI問題,但有沒有集成,系統和自動的方法來解決分析的問題。因此,設計人員采用蠻力方法來修復這些違規行為,或者通過“自動”流程進行無休止的手動迭代。

他們按順序執行點工具,試圖在統計上最小化潛在的信號完整性和可制造性問題,但發現這個多階段補丁過程根本不起作用。即使在流程開始時建立預防性利潤,并進行后處理以試圖消除剩余的違規行為,也不盡如人意。事后的IC實施對于納米設計來說還不夠,因為它留下了太多的開放違規并且太耗時。

市場對更好的解決方案的需求促使公司進行收購或嘗試新的本地化發展。但是,這個問題的真正解決方案可能需要一個可以同時構建和分析設計的集成設計流程。

通過互連可以大大影響融合,從而實現了一種新的物理設計對象查看方式對于。一種實用的方法是取代簡化流程?物理放置細胞,然后在固定細胞之間路由?可以修改網表,進行布局調整并同時進行詳細布線。

這種方法需要在很大程度上依賴于關鍵設計決策的詳細實施,而不是統計預路由和全局假設。它需要能夠在后處理之前增強可制造性,以充分評估增強對設計行為的影響。

這種方法可以將設計從物理設計輸入轉變為干凈的路由設計,滿足所有DRC,時序,SI和DFM要求,但不需要布局后迭代。通過自動實現最終關閉,它可以證明是推進公司產品交付時間表的一個非常有吸引力的解決方案。

最終,它可以在可預測的周轉時間內實現更優化的設計。通過納米級工藝,顯然迫切需要這種緊密集成的物理設計方法,以便公司堅定地關閉。

審核編輯 黃宇

-

IC

+關注

關注

36文章

5961瀏覽量

175776 -

信號

+關注

關注

11文章

2794瀏覽量

76880

發布評論請先 登錄

相關推薦

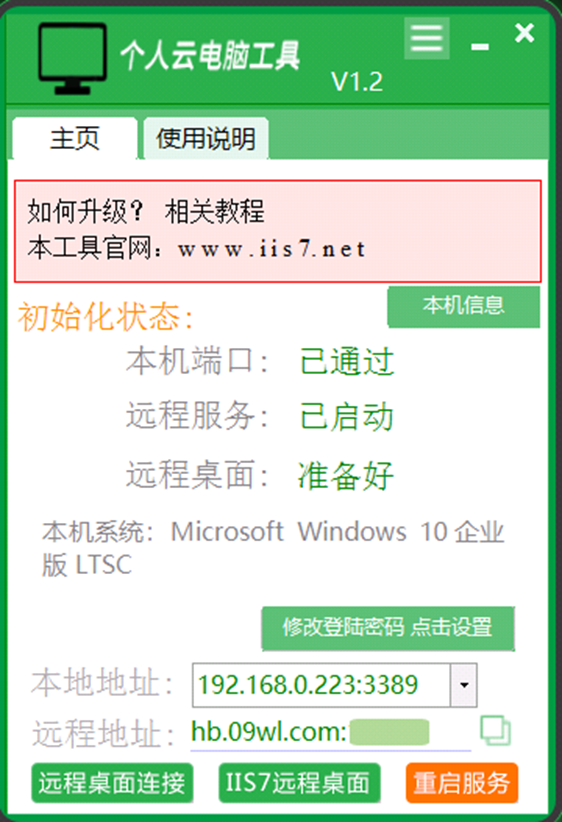

聯想電腦如何關閉云存儲,聯想電腦如何使用才能關閉云存儲

IC關閉的更好途徑

IC關閉的更好途徑

評論