在髙速PCB電路原理全過程中,常常會(huì)碰到信號(hào)完整性難題,造成數(shù)據(jù)信號(hào)傳送品質(zhì)不佳乃至錯(cuò)誤。那麼怎樣區(qū)別髙速數(shù)據(jù)信號(hào)和一般數(shù)據(jù)信號(hào)呢?許多人感覺數(shù)據(jù)信號(hào)頻率高的就是說髙速數(shù)據(jù)信號(hào),其實(shí)要不然。人們了解一切數(shù)據(jù)信號(hào)能夠由正弦數(shù)據(jù)信號(hào)的N次脈沖電流來表達(dá),而數(shù)據(jù)信號(hào)的最大頻率或是數(shù)據(jù)信號(hào)網(wǎng)絡(luò)帶寬算是考量數(shù)據(jù)信號(hào)是不是髙速數(shù)據(jù)信號(hào)的規(guī)范。

圖一

圖二

圖三

圖四

圖五

1、防護(hù)

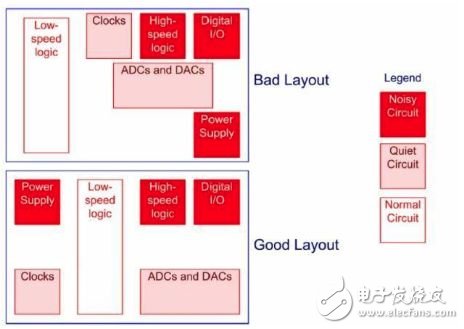

一塊兒PCB板上的電子器件有各式各樣的邊值(edge rates)和各種各樣噪音差別。對(duì)改進(jìn)SI最立即的方法就是說根據(jù)元器件的邊值和敏感度,根據(jù)PCB板上電子器件的物理學(xué)防護(hù)來保持。

圖1是1個(gè)案例。在事例中,供電系統(tǒng)開關(guān)電源、大數(shù)字I/O端口號(hào)和髙速邏輯性這種對(duì)鐘表和數(shù)據(jù)轉(zhuǎn)換電源電路的高風(fēng)險(xiǎn)電源電路將被非常考慮到。

第一位合理布局中置放鐘表和統(tǒng)計(jì)數(shù)據(jù)轉(zhuǎn)化器在鄰近于噪音元器件的周邊。噪音將會(huì)藕合到比較敏感電源電路及減少她們的特性。下一個(gè)合理布局干了合理的電源電路防護(hù)將有益于控制系統(tǒng)設(shè)計(jì)的信號(hào)完整性。

2、特性阻抗、反射面及終端設(shè)備配對(duì)

特性阻抗操縱和終端設(shè)備配對(duì)是髙速電路原理中的基礎(chǔ)難題。一般每一電路原理中頻射電源電路均被覺得是最關(guān)鍵的一部分,殊不知某些比頻射更高頻的數(shù)字電路設(shè)計(jì)反倒忽略了特性阻抗和終端設(shè)備配對(duì)。

因?yàn)樘匦宰杩故湓斐傻膸最悓?duì)數(shù)字電路致命性的危害,參照?qǐng)D為:

a.模擬信號(hào)將會(huì)在接受機(jī)器設(shè)備鍵入端和發(fā)射點(diǎn)機(jī)器設(shè)備的輸出端間導(dǎo)致反射面。反射面數(shù)據(jù)信號(hào)被彈回而且順著線的兩邊散播直至最終被徹底消化吸收。

b.反射面數(shù)據(jù)信號(hào)導(dǎo)致數(shù)據(jù)信號(hào)在根據(jù)傳輸線的響鈴效用,響鈴將危害工作電壓和數(shù)據(jù)信號(hào)延遲和數(shù)據(jù)信號(hào)的徹底惡變。

c.失配數(shù)據(jù)信號(hào)相對(duì)路徑將會(huì)造成數(shù)據(jù)信號(hào)對(duì)自然環(huán)境的輻射源。

由特性阻抗不配對(duì)造成的難題能夠根據(jù)終端設(shè)備電阻器降至最少。終端設(shè)備電阻器一般是在挨近接收端的電源線上置放一到2個(gè)吸收合并元器件,簡易的作法就是說接雙小的電阻器。

終端設(shè)備電阻器限定了數(shù)據(jù)信號(hào)上升時(shí)間及消化吸收了一部分反射面的動(dòng)能。特別注意的是運(yùn)用阻抗匹配并不可以徹底清除毀滅性要素。殊不知用心的采用適合的元器件,終端設(shè)備特性阻抗能夠很合理的操縱數(shù)據(jù)信號(hào)的一致性。

并并不一定的電源線都必須特性阻抗操縱,在某些諸如此類緊湊 PCI 規(guī)格型號(hào)規(guī)定中的特點(diǎn)特性阻抗和終端設(shè)備特性阻抗特點(diǎn)。針對(duì)其他沒有特性阻抗操縱標(biāo)準(zhǔn)規(guī)定的別的規(guī)范及其設(shè)計(jì)師并沒有刻意關(guān)心的。

最后的規(guī)范將會(huì)變化很大從1個(gè)運(yùn)用到另外運(yùn)用中。因而必須考慮到電源線的長短(有關(guān)與延遲時(shí)間 Td)及其數(shù)據(jù)信號(hào)上升時(shí)間(Tr)。通用性的對(duì)特性阻抗操縱標(biāo)準(zhǔn)是 Td(延遲時(shí)間)應(yīng)超過 Tr 的 1/6。

3、內(nèi)電層及內(nèi)電層切分

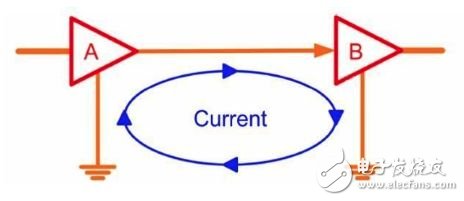

在電流量環(huán)路布置時(shí)會(huì)被數(shù)字電路設(shè)計(jì)者忽略的要素,包含對(duì)單端數(shù)據(jù)信號(hào)在2個(gè)門電路間傳輸?shù)目紤]到(圖2)。從門 A 流入門 B 的電流量環(huán)路,隨后再從地平面圖回到到門 A。

門電路電流量環(huán)路中存有2個(gè)潛在性的難題:

a、 A 和 B 二點(diǎn)間地平面圖必須被聯(lián)接根據(jù)1個(gè)低特性阻抗的通道

假如地平面圖間連接了很大的特性阻抗,在地平面圖腳位間將會(huì)出現(xiàn)工作電壓倒風(fēng)。這就必將會(huì)造成全部元器件的數(shù)據(jù)信號(hào)幅度值的失幀而且累加鍵入噪音。

b、 電流量流回環(huán)的總面積應(yīng)盡量的小

環(huán)路如同無線天線。一般說話,這種更大環(huán)路總面積將會(huì)擴(kuò)大了環(huán)路輻射源和傳輸?shù)臋C(jī)遇。每1個(gè)電源電路設(shè)計(jì)師都期待流回電流量都可以立即順著電源線,那樣就最少的環(huán)路總面積。

用大規(guī)模接地裝置能夠一起處理左右2個(gè)難題。大規(guī)模接地裝置能夠出示全部接地址間小的特性阻抗,一起容許回到電流量盡可能立即順著電源線回到。

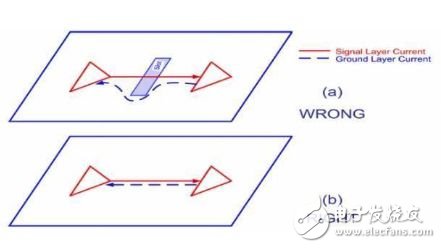

在 PCB 布置中1個(gè)普遍的不正確是在虛梁打過孔和打槽。圖3顯示信息了當(dāng)這條電源線在1個(gè)開了槽的不一樣層上的電流量流入。控制回路電流量將強(qiáng)迫繞開打槽,這就必定會(huì)造成1個(gè)大的環(huán)流控制回路。

一般來講,在地開關(guān)電源平面圖上是不能打槽的。殊不知,在某些難以避免要打槽的場(chǎng)所,PCB 設(shè)計(jì)師務(wù)必最先明確在打槽的地區(qū)沒有數(shù)據(jù)信號(hào)控制回路歷經(jīng)。

一樣的標(biāo)準(zhǔn)也適用混和數(shù)據(jù)信號(hào)電源電路 PCB 板中除非是采用好幾個(gè)地質(zhì)構(gòu)造。尤其性能ADC電源電路中能夠運(yùn)用分離出來模擬信號(hào)、模擬信號(hào)及時(shí)鐘電路的地質(zhì)構(gòu)造合理的降低數(shù)據(jù)信號(hào)間的干撓。

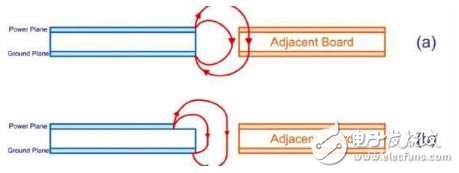

必須再度注重的,在某些難以避免要打槽的場(chǎng)所,PCB 設(shè)計(jì)師務(wù)必最先明確在打槽的地區(qū)沒有數(shù)據(jù)信號(hào)控制回路歷經(jīng)。在含有1個(gè)鏡像系統(tǒng)差別的電源層中也應(yīng)留意虛梁地區(qū)的總面積(圖4)。

在主控板的邊沿存有開關(guān)電源平面圖層對(duì)地平面圖層的輻射源效用。從邊緣泄露的電磁感應(yīng)動(dòng)能將毀壞鄰近的主控板。見圖為4a。適度的降低開關(guān)電源平面圖層的總面積(圖4 b),以致于地平面圖層在必須的地區(qū)內(nèi)相疊。這將降低電磁感應(yīng)泄露對(duì)相鄰主控板的危害。

4、串?dāng)_

在PCB布置中,串?dāng)_難題是另外最該關(guān)心的難題。圖為中顯示信息出在1個(gè)PCB中鄰近的三對(duì)并列電源線間的串?dāng)_地區(qū)及關(guān)系的電磁感應(yīng)區(qū)。當(dāng)電源線間的間距太鐘頭,電源線間的電磁感應(yīng)區(qū)將相互關(guān)系,可能會(huì)導(dǎo)致數(shù)據(jù)信號(hào)的轉(zhuǎn)變就是說串?dāng)_。

串?dāng)_能夠根據(jù)提升電源線間隔處理。殊不知,PCB 設(shè)計(jì)師一般依賴于日漸縮緊的走線室內(nèi)空間和狹小的電源線間隔;因?yàn)樵诓贾弥袥]有大量的挑選,進(jìn)而難以避免的在布置中導(dǎo)入某些串?dāng)_難題。顯而易見,PCB 設(shè)計(jì)師必須必須的管理方法串?dāng)_難題的工作能力。

一般業(yè)內(nèi)認(rèn)同的標(biāo)準(zhǔn)是 3W 標(biāo)準(zhǔn),即鄰近電源線間隔最少應(yīng)是電源線總寬的 3 倍。可是,具體工程項(xiàng)目運(yùn)用中可接納的電源線間隔取決于具體的運(yùn)用、辦公環(huán)境及布置沉余等要素。

電源線間隔從這種狀況轉(zhuǎn)化成另這種及其每一次的測(cè)算。因而,當(dāng)串?dāng)_難題難以避免時(shí),就應(yīng)當(dāng)對(duì)串?dāng)_定量化。這能夠根據(jù)計(jì)算機(jī)仿真技術(shù)性表達(dá)。運(yùn)用仿真器, 設(shè)計(jì)師能夠決策信號(hào)完整性實(shí)際效果和評(píng)定系統(tǒng)軟件的串?dāng)_危害實(shí)際效果。

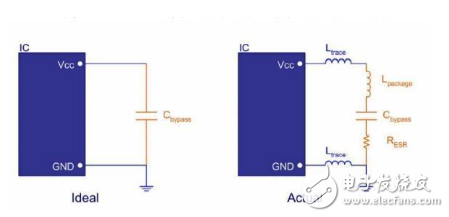

5、開關(guān)電源去耦

開關(guān)電源去耦是數(shù)字電路設(shè)計(jì)中國際慣例,退耦有利于降低電源插頭上噪音難題。迭加進(jìn)開關(guān)電源上的高頻率噪音將會(huì)對(duì)鄰近的大數(shù)字機(jī)器設(shè)備都是產(chǎn)生難題。典型性的噪音于地彈、數(shù)據(jù)信號(hào)輻射源或是大數(shù)字元器件本身。

非常簡單的處理開關(guān)電源噪音方法是運(yùn)用電容器對(duì)土里的高頻率噪音去耦。理想化的退耦電容器為高頻率噪音出示了這條對(duì)地的低阻通道,進(jìn)而消除了開關(guān)電源噪音。

根據(jù)具體運(yùn)用挑選去耦電容器,大部分的設(shè)計(jì)師會(huì)挑選表貼電容器在盡量挨近開關(guān)電源腳位,而容值應(yīng)大到充足為可預(yù)料的開關(guān)電源噪音出示這條低阻對(duì)地通道。

選用退耦電容器一般會(huì)碰到的難題是不可以將退耦電容器簡易的當(dāng)做電容器。有下列幾類狀況:

a、 電容器的封裝會(huì)造成內(nèi)寄生電感器;

b、 電容器會(huì)產(chǎn)生某些等效電阻;

c、 在開關(guān)電源腳位和退耦電容器間的輸電線會(huì)產(chǎn)生某些等效電感器;

d、 在地腳位和地平面圖間的輸電線會(huì)產(chǎn)生某些等效電感器;

從而而引起的效用:

a、 電容器將會(huì)對(duì)特殊的頻率引起共振效應(yīng)和由其造成的互聯(lián)網(wǎng)特性阻抗對(duì)鄰近頻率段的數(shù)據(jù)信號(hào)導(dǎo)致更大的危害;

b、 等效電阻(ESR)還將危害對(duì)髙速噪音退耦所產(chǎn)生的低阻通道;

下列小結(jié)了從而對(duì)1個(gè)大數(shù)字設(shè)計(jì)師造成的效用:

a、 從元器件上 Vcc 和 GND 腳位找出的導(dǎo)線必須被作為小的電感器。因而提議在布置中盡量使 Vcc 和 GND 的導(dǎo)線短而粗。

b、 挑選低 ESR 效用的電容器,這有利于提升對(duì)開關(guān)電源的退耦;

c、 挑選小封裝電容件將會(huì)降低封裝電感器。更換更小封裝的元器件將造成溫度特點(diǎn)的轉(zhuǎn)變。

因而在挑選1個(gè)小封裝電容器后,必須調(diào)節(jié)布置中元器件的合理布局。在布置中,用 Y5V 型號(hào)規(guī)格的電容器替換成 X7R 型號(hào)規(guī)格的電容件,可確保更小的封裝和更低的等效電感器,但一起也會(huì)為確保高的溫度特點(diǎn)花銷大量的元器件成本費(fèi)。

在布置中還應(yīng)考慮到用大空間電容器對(duì)高頻噪音的退耦。選用分離出來的電解電容和貼片電解電容能夠非常好的提升元器件的性價(jià)比高

-

pcb

+關(guān)注

關(guān)注

4319文章

23099瀏覽量

397892 -

信號(hào)完整性

+關(guān)注

關(guān)注

68文章

1408瀏覽量

95488

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高速PCB設(shè)計(jì)的信號(hào)完整性問題

基于信號(hào)完整性分析的高速PCB設(shè)計(jì)

高速PCB設(shè)計(jì)信號(hào)完整性問題形成原因是什么?

高速PCB設(shè)計(jì)的信號(hào)完整性問題分析

如何克服高速PCB設(shè)計(jì)中信號(hào)完整性問題?

高速PCB設(shè)計(jì)信號(hào)完整性問題形成原因及方法解決資料下載

高速電路信號(hào)完整性分析與設(shè)計(jì)—PCB設(shè)計(jì)1

高速電路信號(hào)完整性分析與設(shè)計(jì)—PCB設(shè)計(jì)2

PCB設(shè)計(jì)中的信號(hào)完整性問題

高速pcb設(shè)計(jì)的信號(hào)完整性問題

高速pcb設(shè)計(jì)的信號(hào)完整性問題

評(píng)論