“互連組件”的概念與組件之間的總線和數據傳輸概念一樣古老。互連組件支持在沒有兼容接口的各種處理元件之間進行數據傳輸。它們還用于擴展沒有所需扇出或足夠帶寬的系統總線,以滿足數據傳輸需求。根據應用,使用不同類型的互連組件,具有不同的規格。一些流行的互連組件是雙端口緩沖器,SERDES和PCI橋接芯片。以下是有效使用這些互連組件的幾個示例:

將一個處理元件連接到另一個處理元件,例如,使用雙端口緩沖器將DSP連接到RISC處理器。

將處理器連接到背板,例如,使用SERDES芯片將處理器上的并行接口連接到串行背板。

將處理器連接到總線,例如,使用PCI橋接芯片將主機處理器連接到PCI總線。

擴展總線,例如,使用PCI橋擴展PCI總線。

本文探討了應用,要求和參數芯片到芯片互連,例如雙端口緩沖器,用于將一個處理器連接到另一個處理器。由于簡單的存儲器接口,缺乏復雜的協議和各種選項,雙端口緩沖器是最流行的芯片到芯片互連之一。此外,憑借廣泛的組件組合,雙端口緩沖器可有效支持各種要求,從電信號和數據傳輸帶寬等基本物理層到多個虛擬通道等更復雜的需求。

以下部分深入探討了互連標準演進過程,雙端口作為默認互連,以及雙端口如何滿足各種應用的通用和特定需求。

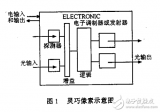

圖1:互連組件示例。

標準:相關性,風險和更安全的方法

標準在定義接口方面發揮著重要作用。與專有接口相比,使用基于標準的接口有許多優點。使用標準接口可以提供多個組件這一事實提供了諸如易于設計,低成本和組件可用性等優點。使用標準接口的設計也提供了簡便的可擴展性和設計可升級性。特定于應用程序的標準還提高了性能,因為它們針對給定的應用程序進但是,標準演進需要時間和精力。如下面IEEE標準的示例時間表所示(圖2),標準的形成可能需要兩年才能獲得批準,可能還需要一年才能獲得廣泛的組件。

多方都是經過多年的努力,在批準和廣泛適應之前,對即將推出的標準接口進行調整風險很大。

圖2:IEEE標準流程圖的時間線。

更安全和實用的替代方法是使用默認標準。對于給定的應用,默認標準不一定由行業機構開發。但是,默認標準是在許多具有明確定義規范的設備中使用的標準。使用默認標準可以獲得準確的性能,并且業務風險有限。

SRAM接口:默認標準

具有雙向數據總線,單向地址總線和相關控制信號的SRAM接口是最常見的接口之一在各種微處理器,數字信號處理器和其他處理元件上。標準SRAM接口也是最簡單的總線,可以在CPLD和FPGA等可編程邏輯器件中實現。

今天的SRAM接口提供了選擇總線寬度和高速I/O的靈活性,例如HSTL和LVTTL。它可以提供從幾Kbps到36 Gbps的數據傳輸速率,具有72位總線寬度和250 MHz訪問頻率。這涵蓋了芯片到芯片通信的各種應用的性能需求。

標準SRAM接口在大多數處理器平臺(如RISC和CISC CPU,DSP和ASSP)中也非常常見。以下(圖3)是具有SRAM接口的CPU的示例。這里要注意的一個關鍵點是這些處理器之間的接口速度和總線寬度的變化。

圖3:幾個具有存儲器接口的流行DSP和處理器。

雙端口緩沖器作為互連組件

鑒于存儲器接口的存在非常普遍并且提供了諸如帶寬之類的所需性能,因此存儲器接口可以用作互連功能的“默認”接口。然而,存儲器接口對于數據是雙向的并且是用于控制的單向的。對于對等數據傳輸,絕對需要雙向控制。雙端口緩沖器使兩個處理器都能像“主設備”一樣工作,并有效地創建雙向控制。

此外,雙端口緩沖區提供了完全的靈活性,可以簡化系統設計并實現性能目標,而不會增加多層協議的復雜性和與之相關的處理延遲。因此,雙端口緩沖區通常用作互連組件。

為滿足不同的系統要求,雙端口緩沖區具有多種功能和參數。下一節將介紹雙端口緩沖區如何解決各種系統的通用和特定于應用程序的需求。

實際問題

對于芯片到芯片的數據傳輸,互連組件(如雙端口緩沖器)有效地彌合了不同的差距系統組件,解決了幾個關鍵的互連問題:

時鐘頻率:兩個處理元件之間的時鐘頻率差異給將數據從一個處理元件傳輸到另一個處理元件帶來了嚴峻挑戰。例如,在視頻基礎設施設備中,圖像處理元件可以以一個時鐘速率操作,而MPEG編碼器在另一個時鐘速率下操作。

在這種情況下,真正的雙端口存儲器可以使用自己的時鐘連接這兩個處理元件。由于設備的兩個端口完全相互獨立,因此這些時鐘可以以不同的速率運行。

傳輸速率:兩個處理元件之間的傳輸不匹配率非常高在多處理環境中很常見。在雙端口互連中具有內置緩沖存儲器有效地解決了這個問題。

圖4:雙端口解決方案符合物理層互連要求。

總線不匹配:總線寬度和電氣接口的不匹配可能是約束或理想情況。例如,在設計升級中,經過驗證的具有100 MHz LVTTL I/O的ASSP需要連接到FPGA。 ASSP可以以恒定速率抽出數據,但FPGA設計要求它以突發方式并以更高的傳輸速率輸入數據。這意味著如果FPGA可以使用其200 MHz HSTL I/O,則可以使設計升級更加簡單。

即使FPGA能夠以恒定速率輸入數據,使用只有一半總線寬度的200 MHz HSTL I/O可以顯著增強電路板的PCB布線。更靈活的雙端口在任一端口上提供各種不同的電接口,以最有效的方式解決這種情況。

通用控制和數據接口:控制平面和數據平面的通用物理接口是復雜多處理環境中的最佳要求。例如,在多個DSP在它們之間傳輸碼片速率和符號率數據的無線基站中,它們還需要將控制信息(例如天線數,信號強度和過載情況)傳送到另一個DSP。理想情況下,這需要通過用于數據平面的相同高速接口來實現,以保持電路板設計的復雜性。只有當接口能夠支持多個虛擬通道時,才能執行此操作。

雙端口緩沖區支持此要求,無需任何協議開銷即可實現性能。通過使用郵箱,雙端口緩沖區甚至可以向接收處理器發送中斷信號,以進行高優先級控制平面通信。

虛擬通道:用于傳輸多個,獨立的虛擬通道處理器之間的數據流可以從處理器中獲取大量協議開銷。

雙端口緩沖區通過提供機制來靈活管理多個虛擬流,以便處理器可以處理這些虛擬流,如如果它們位于特定的存儲位置。

互連的應用要求

除了雙端口緩沖區解決的通用系統設計問題之外,如上所述,不同的應用程序要求定義了該特定應用程序的雙端口緩沖區的參數。

例如,無線基礎設施受性能的高度推動。 3G基站中的芯片到芯片數據傳輸可以達到多個Gbps。這要求互連組件不僅支持高數據傳輸速率,而且還提供足夠的緩沖深度和架構靈活性,以支持高速數據傳輸。

同樣,對于高端存儲系統,支持多個虛擬通道的能力對于支持不同數據流的信用緩沖區非常有用。互連組件中的這種能力可以為系統設計增加更多價值。

新一代手機使用獨立的基帶處理器和應用處理器。連接手機中這兩個處理器的雙端口緩沖器需要非常小并且功耗很低。

最后,考慮視頻基礎設施環境通常同時處理多個視頻源。通過互連組件的多個虛擬通道極大地簡化了設計。

圖5:雙端口符合特定應用的互連要求。

處理器間互連要求通常隨應用程序而變化。對于芯片到芯片的互連要求 - 在應用架構和優化的接口標準成熟之前 - 使用“默認”接口(例如存儲器接口)可提供最佳性能而無需額外風險。

-

處理器

+關注

關注

68文章

19286瀏覽量

229815 -

dsp

+關注

關注

553文章

7998瀏覽量

348904 -

接口

+關注

關注

33文章

8596瀏覽量

151146

發布評論請先 登錄

相關推薦

如何安裝紅杉WiFi組件?

無源組件與有源元件及機電組件的功能區別

有人有使用SPI-FRAM的示例代碼或IDF組件嗎?

CoreLink網絡互連NIC-301技術參考手冊

OpenHarmony組件復用示例

LTCC微波多芯片組件中鍵合互連的微波特性

多芯片組件(MCM),多芯片組件(MCM)是什么意思

OpenHarmony自定義組件FlowImageLayout

OpenHarmony自定義組件CircleProgress

互連組件使用示例

互連組件使用示例

評論