由于多種因素的綜合作用,電源噪聲和相關(guān)問(wèn)題已成為90nm及以下設(shè)計(jì)的關(guān)鍵。由于電網(wǎng)噪聲,定時(shí)減速和功能故障在這些設(shè)計(jì)中變得普遍。然而,物理設(shè)計(jì)和驗(yàn)證方法尚未充分發(fā)展以充分解決這些電源噪聲問(wèn)題。

芯片電源的規(guī)劃,資源分配和設(shè)計(jì)(包括封裝,去耦電容和電網(wǎng)網(wǎng)絡(luò))必須以整體方式進(jìn)行,并進(jìn)行簽核質(zhì)量驗(yàn)證和分析。設(shè)計(jì)人員需要降低設(shè)計(jì)中動(dòng)態(tài)壓降(DvD)的技術(shù)及其對(duì)時(shí)序和功能的影響,他們需要采用功耗感知物理設(shè)計(jì)方法。

動(dòng)態(tài)電網(wǎng)噪聲

電源噪聲具有以下組成部分:電阻網(wǎng)絡(luò)壓降,電容耦合電網(wǎng)噪聲和電感元件誘發(fā)噪音。技術(shù)和設(shè)計(jì)趨勢(shì)加劇了電源噪聲水平及其對(duì)性能的影響。

圖1顯示了基于ITRS數(shù)據(jù)的平均電流和di/dt值預(yù)測(cè)[1]。該趨勢(shì)表明,在先進(jìn)技術(shù)節(jié)點(diǎn)中,同時(shí)切換設(shè)備的動(dòng)態(tài)電壓降將變得更糟。不僅更高的di/dt會(huì)導(dǎo)致更大的動(dòng)態(tài)壓降,而且導(dǎo)線中更高的開(kāi)關(guān)電流也會(huì)導(dǎo)致更大的電阻壓降。

圖1 - 電流消耗趨勢(shì)

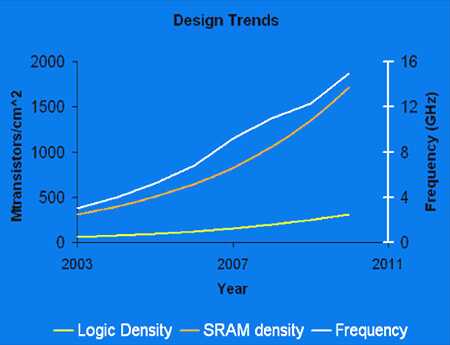

如圖2所示,更高的單元放置密度,更短的邊沿速率和更快的時(shí)鐘周期將導(dǎo)致更多的單元在時(shí)間上和空間上更緊密地切換,從而提高對(duì)瞬時(shí)電流的需求。針對(duì)封裝設(shè)計(jì),片上電網(wǎng)尺寸調(diào)整和去耦電容分配的現(xiàn)有方法和設(shè)計(jì)實(shí)踐將不足以創(chuàng)建能夠響應(yīng)更大和更頻繁的片上電流尖峰的電源系統(tǒng),這將在下一代中看到設(shè)計(jì)。

圖2 - 設(shè)計(jì)趨勢(shì)

隨著設(shè)計(jì)從130nm技術(shù)節(jié)點(diǎn)遷移,設(shè)計(jì)人員正在超越傳統(tǒng)靜態(tài)電壓降分析采用全芯片動(dòng)態(tài)仿真方法,該方法考慮了同步開(kāi)關(guān)電流與設(shè)計(jì)中存在的電感和電容元件的相互作用。一種早期的動(dòng)態(tài)分析形式包括將模擬周期劃分為幾個(gè)區(qū)間,并在每個(gè)區(qū)間內(nèi)進(jìn)行靜態(tài)分析。

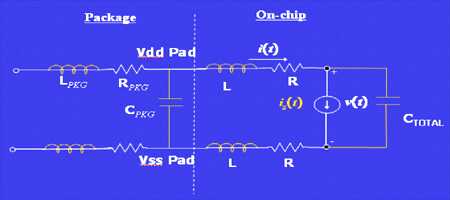

今天,這種方法已被高度精確的全芯片瞬態(tài)仿真解決方案所取代。提供設(shè)計(jì)中動(dòng)態(tài)電壓曲線的完整畫(huà)面。該仿真技術(shù)考慮了芯片封裝和片上網(wǎng)格中的電阻,電感和電容元件,同時(shí)切換輸出所消耗的動(dòng)態(tài)電流以及設(shè)計(jì)中存在的容性負(fù)載。圖3說(shuō)明了該解決方案中建模的仿真框架。

圖3 - 動(dòng)態(tài)仿真模型

影響動(dòng)態(tài)電源噪聲

靜態(tài)定時(shí)工具不能解決DvD對(duì)松弛和轉(zhuǎn)換的影響,這通常遠(yuǎn)大于靜態(tài)壓降預(yù)算。在存在電網(wǎng)噪聲的情況下,電池的傳播延遲增加。

此外,高級(jí)流程中的大門(mén)更有可能受到DvD的影響。高柵極延遲靈敏度和增加的電網(wǎng)噪聲的組合導(dǎo)致芯片中的頻率減慢,否則通過(guò)靜態(tài)時(shí)序分析。許多設(shè)計(jì),特別是那些90nm節(jié)點(diǎn)的設(shè)計(jì),都出現(xiàn)了動(dòng)態(tài)電壓降相關(guān)問(wèn)題的失敗。

時(shí)鐘網(wǎng)絡(luò)上的時(shí)序影響會(huì)更大,因?yàn)榫彌_區(qū)通常彼此靠近并且切換一起。電網(wǎng)噪聲的可變性轉(zhuǎn)化為增加的偏斜,導(dǎo)致保持時(shí)間要求失敗。定時(shí)和時(shí)鐘偏移分析必須考慮關(guān)鍵路徑中實(shí)例或時(shí)鐘網(wǎng)絡(luò)中緩沖器所見(jiàn)的動(dòng)態(tài)電壓降。

電網(wǎng)噪聲也會(huì)影響a的串?dāng)_抗擾度。設(shè)計(jì)。當(dāng)電池同時(shí)經(jīng)歷電壓降和/或接地反彈時(shí),電池更可能從耦合噪聲中失效。細(xì)胞的譜庫(kù)表征通常不能解釋瞬態(tài)電壓降及其對(duì)細(xì)胞性能的影響。因此,功能可能會(huì)受到影響,尤其是在一段時(shí)間內(nèi)持續(xù)保持動(dòng)態(tài)電壓降時(shí)。

固定電網(wǎng)噪聲

設(shè)計(jì)人員必須估算和補(bǔ)償電網(wǎng)噪聲,以確保其電路正常運(yùn)行并防止前面提到的電源發(fā)生故障。傳統(tǒng)技術(shù)是過(guò)度設(shè)計(jì)電源網(wǎng)絡(luò)并用去耦電容器填充所有可用區(qū)域。對(duì)于具有更高噪聲容限和更大設(shè)計(jì)保護(hù)頻帶的上一代設(shè)計(jì),這種方法已經(jīng)相當(dāng)不錯(cuò)。

然而,通過(guò)先進(jìn)的流程,設(shè)計(jì)師不再擁有填充設(shè)計(jì)目標(biāo)和增加豐厚利潤(rùn)的奢侈品。更嚴(yán)格的設(shè)計(jì)規(guī)范(包括更低的電源電壓和更快的時(shí)鐘頻率)留下的誤差空間更小。在投入生產(chǎn)之前,關(guān)鍵設(shè)計(jì)的上市時(shí)間只能提供非常少的流片迭代。

低成本設(shè)計(jì)受到過(guò)度設(shè)計(jì)的電網(wǎng)和更多硅資源使用的嚴(yán)重影響。需要多個(gè)調(diào)試和流片周期來(lái)識(shí)別和修復(fù)與電網(wǎng)相關(guān)的芯片故障。由于缺乏可用的路由空間,電網(wǎng)的過(guò)度設(shè)計(jì)也會(huì)影響項(xiàng)目進(jìn)度,因?yàn)槁酚珊蜁r(shí)序收斂變得更加困難。

電網(wǎng)設(shè)計(jì)傳統(tǒng)上基于啟發(fā)式或經(jīng)驗(yàn)。電力網(wǎng)絡(luò)在整個(gè)設(shè)計(jì)中的寬度和間距通常是均勻的。設(shè)計(jì)完成后,電源路由保持不變,除非在流片輸出之前執(zhí)行的壓降驗(yàn)證表明存在問(wèn)題區(qū)域。這種方法的問(wèn)題是:

網(wǎng)格未針對(duì)特定設(shè)計(jì)及其功耗進(jìn)行優(yōu)化。

網(wǎng)格均勻設(shè)計(jì)過(guò)度或設(shè)計(jì)不足。

電網(wǎng)問(wèn)題僅在設(shè)計(jì)周期的后期解決。

故意去耦電容( decap)放置也是臨時(shí)的,無(wú)助于抑制電網(wǎng)噪聲。這些開(kāi)蓋單元通常放置在空單元行中,其中沒(méi)有足夠的切換使它們有效。此外,通過(guò)消耗更多的漏電流,不加選擇的去耦位置會(huì)對(duì)設(shè)計(jì)產(chǎn)生不利影響,這是一個(gè)問(wèn)題,因?yàn)?0nm設(shè)計(jì)中芯片總功率的約30%將來(lái)自漏電流。

功率感知物理設(shè)計(jì)

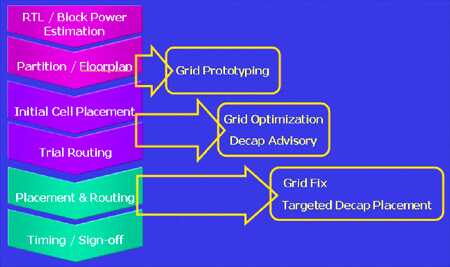

電源感知物理設(shè)計(jì)需要改變當(dāng)前的設(shè)計(jì)實(shí)踐。初始電網(wǎng)的設(shè)計(jì)應(yīng)符合某些規(guī)范。應(yīng)該使用原型解決方案來(lái)快速生成針對(duì)各種用戶定義約束的多個(gè)電網(wǎng)設(shè)計(jì),例如不同的布局規(guī)劃或功耗方案,以估計(jì)路由資源需求。

在設(shè)計(jì)過(guò)程的早期階段,應(yīng)該優(yōu)化選定的原型網(wǎng)格,同時(shí)仍然可以靈活地更改電源路徑。應(yīng)使用簽核質(zhì)量的電網(wǎng)分析解決方案來(lái)驗(yàn)證優(yōu)化的質(zhì)量。

在設(shè)計(jì)的后期階段,當(dāng)更多地定義放置時(shí),應(yīng)該對(duì)電網(wǎng)執(zhí)行目標(biāo)修復(fù)以解決電壓降問(wèn)題。去耦電容建議應(yīng)該是自動(dòng)的,以解決動(dòng)態(tài)熱點(diǎn)問(wèn)題,并使設(shè)計(jì)人員能夠有針對(duì)性地進(jìn)行去耦,優(yōu)化動(dòng)態(tài)電壓降,同時(shí)最大限度地減少對(duì)去耦泄漏電流的影響。

圖4顯示了功率感知物理設(shè)計(jì)流程,為初始P/G路由定義提供原型解決方案,允許沿設(shè)計(jì)周期優(yōu)化P/G網(wǎng)格,修復(fù)P/G網(wǎng)格問(wèn)題,建議十進(jìn)制要求,并以有針對(duì)性的方式進(jìn)行減速。

圖4 - 功率感知物理設(shè)計(jì)流程

網(wǎng)格原型設(shè)計(jì)

網(wǎng)格原型設(shè)計(jì)應(yīng)允許設(shè)計(jì)人員針對(duì)各種設(shè)計(jì)方案探索不同的電網(wǎng)設(shè)計(jì)選項(xiàng)。高效,快速,準(zhǔn)確的電網(wǎng)原型設(shè)計(jì)解決方案將使設(shè)計(jì)人員能夠嘗試不同的布局規(guī)劃選項(xiàng),多種功耗場(chǎng)景和多種布線預(yù)算。原型設(shè)計(jì)解決方案應(yīng)該足夠靈活,可以在設(shè)計(jì)的最初階段工作,當(dāng)最小的布局信息可用時(shí),或者在設(shè)計(jì)的稍微更確定的階段,當(dāng)早期布局信息和定義全球和本地電網(wǎng)的范圍是可用。

網(wǎng)格原型設(shè)計(jì)應(yīng)受約束驅(qū)動(dòng),以滿足用戶定義的動(dòng)態(tài)和靜態(tài)電壓降目標(biāo),同時(shí)滿足特定的路由資源使用限制。由原型解決方案生成的多層電網(wǎng)應(yīng)該遵循阻塞和電遷移限制,探索焊盤(pán)放置選項(xiàng),并在需要時(shí)生成環(huán)。

它應(yīng)該為用戶提供探索非均勻網(wǎng)格選項(xiàng)的能力,其中高功率區(qū)域獲得更高的電網(wǎng)資源份額。原型設(shè)計(jì)解決方案還應(yīng)具有快速周轉(zhuǎn)時(shí)間,以實(shí)現(xiàn)多次迭代。

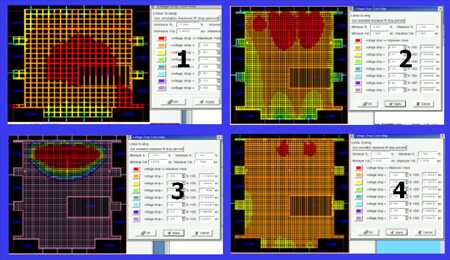

圖5顯示了設(shè)計(jì)團(tuán)隊(duì)如何針對(duì)不同的布局規(guī)劃和功耗場(chǎng)景探索不同的電網(wǎng)結(jié)構(gòu)。通過(guò)執(zhí)行此練習(xí),設(shè)計(jì)團(tuán)隊(duì)可以獲得每個(gè)方案所需的P/G網(wǎng)格路由資源的工程估計(jì)。然后,他們可以選擇最適合其最可能的設(shè)計(jì)方案的電網(wǎng)。這個(gè)選定的電網(wǎng)將是最佳的,以滿足其功率和路由目標(biāo)。

圖5 - 電網(wǎng)結(jié)構(gòu)探索

電網(wǎng)優(yōu)化和修復(fù)

隨著設(shè)計(jì)的發(fā)展,應(yīng)優(yōu)化原型網(wǎng)格以反映設(shè)計(jì)變化。為了滿足設(shè)計(jì)的電壓降目標(biāo),優(yōu)化解決方案應(yīng)根據(jù)用戶提供的限制(如節(jié)距和軌道要求)重新定義電網(wǎng)。這種方法可以讓設(shè)計(jì)人員通過(guò)精煉電網(wǎng)的自動(dòng)化流程來(lái)滿足其降壓預(yù)算。對(duì)于給定的壓降預(yù)算,優(yōu)化解決方案將調(diào)整導(dǎo)線的尺寸以最小化P/G網(wǎng)格的金屬布線使用。設(shè)計(jì)人員不是首先設(shè)計(jì)網(wǎng)格然后獲得電壓降數(shù),而是首先確定下降預(yù)算并設(shè)計(jì)一個(gè)符合該預(yù)算的網(wǎng)格。

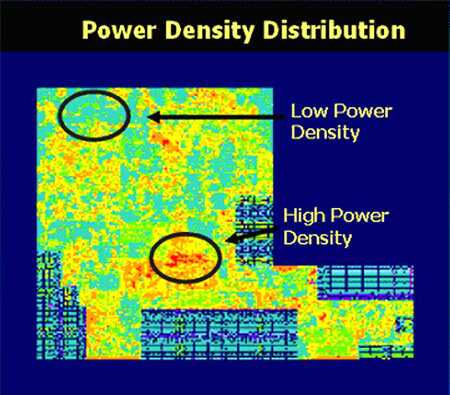

設(shè)計(jì)中的功耗,尤其是功率密度,通常非常不均勻,如圖6所示。功率密度“熱點(diǎn)”通常出現(xiàn)在插入時(shí)鐘緩沖器的區(qū)域。

圖6 - 功率密度圖

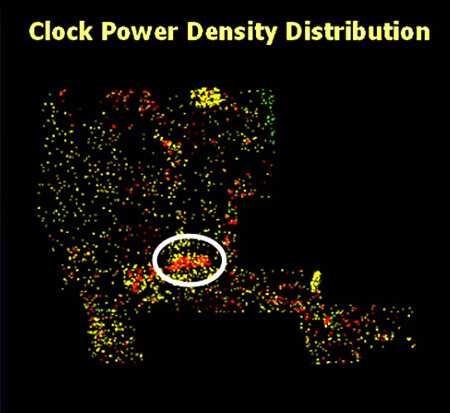

時(shí)鐘實(shí)例功率圖,如圖8所示,顯示了與圖7中的功率密度圖。電網(wǎng)優(yōu)化解決方案應(yīng)該將更多的金屬資源分配給可能具有比具有稀疏單元布局的區(qū)域更高的電壓降的區(qū)域。對(duì)于采用有線封裝設(shè)計(jì)的電源和分布問(wèn)題更加局部化的倒裝芯片設(shè)計(jì),情況尤其如此。

圖7 - 時(shí)鐘功率密度

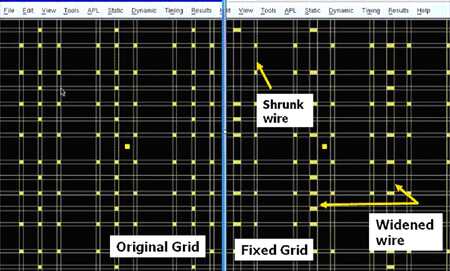

一旦完成詳細(xì)布局并且正在進(jìn)行時(shí)序優(yōu)化,電力和地面網(wǎng)絡(luò)的全局優(yōu)化就不再可行。在這種情況下,需要對(duì)電網(wǎng)進(jìn)行有針對(duì)性的修復(fù)以解決電壓降“熱點(diǎn)”。電網(wǎng)應(yīng)僅在熱點(diǎn)區(qū)域加寬,在其他區(qū)域縮小,不會(huì)影響總電壓降。

解決方案應(yīng)提供快速周轉(zhuǎn)時(shí)間,以解決可能導(dǎo)致的P/G問(wèn)題來(lái)自設(shè)計(jì)迭代。用戶應(yīng)該只能修復(fù)他們?cè)O(shè)計(jì)中的特定區(qū)域,限制對(duì)某些金屬層的修復(fù),并定義修復(fù)的方式。

圖8說(shuō)明了設(shè)計(jì)的電網(wǎng)如何運(yùn)行自動(dòng)修復(fù)解決方案后更改。左側(cè)面板顯示原始的均勻網(wǎng)格,而右側(cè)面板顯示固定網(wǎng)格,其中一些導(dǎo)線已經(jīng)加寬而其他導(dǎo)線已經(jīng)縮小。

圖8 - 非均勻的線柵固定

開(kāi)蓋建議和修理

Decaps作為當(dāng)?shù)氐某潆娝畮?kù),它們的位置應(yīng)該是以有針對(duì)性的方式完成,以將功率和地面噪聲降低到可接受的限度。然而,特殊的decap接頭增加了不必要的漏電流,同時(shí)降低了動(dòng)態(tài)電壓降。沿著電源線和地線的電阻降的增加需要將decap放置在更靠近開(kāi)關(guān)區(qū)域的位置。

設(shè)計(jì)師應(yīng)該被引導(dǎo)到最有效的開(kāi)蓋位置的位置,并且它們應(yīng)該能夠自動(dòng)重新定義細(xì)胞并去除放置位置以減少DvD。高壓降區(qū)域不一定必須重新設(shè)計(jì),除非它影響通過(guò)該區(qū)域的路徑的時(shí)序或影響該區(qū)域中的單元的功能。因此,固定解決方案應(yīng)該基于精確的動(dòng)態(tài)功耗分析,并提供反饋到時(shí)序分析,并應(yīng)確定需要使用開(kāi)蓋放置或線尺寸調(diào)整來(lái)固定的區(qū)域。

開(kāi)蓋放置解決方案應(yīng)該在咨詢模式,向設(shè)計(jì)者提供關(guān)于需要減速的地方的反饋,以及通過(guò)在合法化的放置區(qū)域中放置decap來(lái)修復(fù)模式。它應(yīng)滿足用戶指定的目標(biāo),同時(shí)遵守總泄漏電流和放置限制等約束。

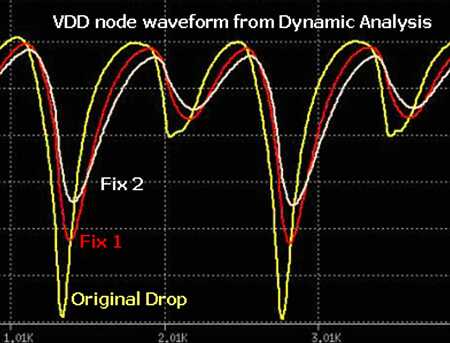

它應(yīng)該提供根據(jù)用戶的規(guī)范通過(guò)使用電線更改或decap放置或兩者來(lái)解決問(wèn)題的選項(xiàng)。圖9示出了在具有用于降低動(dòng)態(tài)電壓噪聲的不同目標(biāo)的兩個(gè)不同的去耦固定運(yùn)行之后的實(shí)例的電源節(jié)點(diǎn)處的電壓噪聲。

圖9 - 對(duì)Vdd噪聲進(jìn)行消隱固定結(jié)果

結(jié)論

縮短產(chǎn)品生命周期加快了新設(shè)計(jì)的推出速度。首先進(jìn)入市場(chǎng)會(huì)顯著影響產(chǎn)品在這種環(huán)境中取得成功的機(jī)會(huì)。

掩模組的高價(jià)格以及與頻繁設(shè)計(jì)變更相關(guān)的成本要求設(shè)計(jì)團(tuán)隊(duì)預(yù)測(cè)并解決設(shè)計(jì)失敗的原因。他們必須超越傳統(tǒng)的電網(wǎng)設(shè)計(jì)和分析技術(shù)來(lái)估計(jì)和減少P/G噪聲對(duì)設(shè)計(jì)時(shí)序和功能的影響。

在許多失敗的90nm設(shè)計(jì)中,電網(wǎng)噪聲最常被認(rèn)為是失效源。其他設(shè)計(jì)團(tuán)隊(duì)發(fā)現(xiàn)P/G噪音更明顯地表現(xiàn)在產(chǎn)量損失等問(wèn)題上。下一代芯片需要采用整體的電源設(shè)計(jì)方法來(lái)解決這些問(wèn)題,其中過(guò)度設(shè)計(jì)和保護(hù)帶不再是可行的選擇。

本文概述了功率感知物理設(shè)計(jì)該方法允許工程師設(shè)計(jì)芯片電源,以幫助減輕P/G噪聲引起的設(shè)計(jì)故障并避免后期設(shè)計(jì)變更。它突出顯示了使用商用解決方案生成的數(shù)據(jù),該解決方案集成了動(dòng)態(tài)電網(wǎng)噪聲的電網(wǎng)原型設(shè)計(jì),優(yōu)化,修復(fù)和驗(yàn)證,可實(shí)現(xiàn)更快,更有效的設(shè)計(jì)收斂。

-

電源

+關(guān)注

關(guān)注

184文章

17740瀏覽量

250524 -

電網(wǎng)

+關(guān)注

關(guān)注

13文章

2082瀏覽量

59212

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

可解決動(dòng)態(tài)電網(wǎng)噪聲的電網(wǎng)原型設(shè)計(jì)方案

可解決動(dòng)態(tài)電網(wǎng)噪聲的電網(wǎng)原型設(shè)計(jì)方案

評(píng)論