降低片上功耗已成為納米技術(shù)時(shí)代的關(guān)鍵挑戰(zhàn)。現(xiàn)在,性能和面積之間的傳統(tǒng)權(quán)衡因此增加了權(quán)力。

與功耗相關(guān)的問題不僅適用于電池供電,手持和移動(dòng)應(yīng)用,還包括90nm及以上的所有產(chǎn)品,其功率不僅會(huì)影響設(shè)計(jì)上市時(shí)間,還會(huì)影響成本和可靠性。

為什么功耗低

在進(jìn)入分析和降低功耗的細(xì)節(jié)之前,我們首先要看看為什么它如此關(guān)鍵在今天的設(shè)計(jì)中。

在SoC中不斷增加的功能,性能和集成應(yīng)用的持續(xù)趨勢導(dǎo)致功耗在數(shù)百瓦的設(shè)計(jì)。這可以從英特爾的最新處理器變體中看出,例如,Itanium2接近130瓦[1]。這類器件需要昂貴的封裝,散熱片和冷卻環(huán)境。

這導(dǎo)致了許多其他問題需要解決,以保持未來應(yīng)用的可行性。與前幾代產(chǎn)品相比,移動(dòng)應(yīng)用程序集成度的提高對產(chǎn)品的電池壽命提出了更高的要求。雖然CMOS技術(shù)的進(jìn)步使晶體管密度大約每18個(gè)月翻一番,但電池技術(shù)的同等進(jìn)步大于每五年。

芯片上有大電流會(huì)縮短使用壽命和可靠性的產(chǎn)品。隨著頻率的增加,充電(和放電)總負(fù)載電容所需的平均片上電流也增加,而電流浪涌的時(shí)間導(dǎo)致器件的配電網(wǎng)絡(luò)上的功率波動(dòng)。

這些動(dòng)態(tài)電壓降是產(chǎn)生延遲不確定性的一個(gè)問題,導(dǎo)致可能的功能問題,并最終通過完整的器件故障縮短產(chǎn)品壽命[2]。最后,作為整體系統(tǒng)設(shè)計(jì)的一部分,如何解決器件耗散的功率問題變得越來越昂貴。

耗電的地方

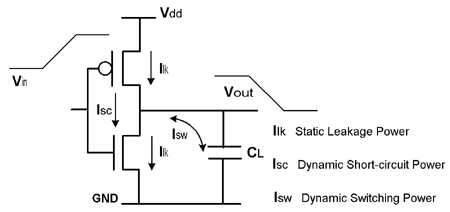

設(shè)備內(nèi)的功耗可以分為兩種基本類型 - 基于開關(guān)活動(dòng)的動(dòng)態(tài)功耗和基于泄漏的靜態(tài)功耗。由于電路驅(qū)動(dòng)的容性負(fù)載的充電和放電(包括凈電容和輸入負(fù)載),動(dòng)態(tài)功耗可以分解為開關(guān)功率,并且當(dāng)成對的PMOS和NMOS晶體管在切換期間瞬間發(fā)生短路功率。同時(shí)進(jìn)行。

泄漏功率也可以分解為許多關(guān)鍵貢獻(xiàn)者。一個(gè)是流過在擴(kuò)散區(qū)和襯底之間形成的反向偏置二極管的電流(I 二極管)。另一種是流過不導(dǎo)通的晶體管的電流,隧道穿過柵極氧化物(I subthreshold )。請注意,設(shè)備的泄漏會(huì)受到工作溫度的極大影響。因此,隨著芯片升溫,靜態(tài)功耗呈指數(shù)增長。

圖1 - CMOS功耗

泄漏在具有0.7V閾值的130nm工藝中,每個(gè)晶體管產(chǎn)生大約10-20pA的電流;在同一過程中將閾值降低至0.3V,并且每個(gè)晶體管的漏電流火箭升至10-20 nA,在較小的幾何結(jié)構(gòu)中呈指數(shù)增長。

因此可以看出,泄漏受Vth相對于Vdd,晶體管尺寸和溫度的接近程度的影響。 David J. Frank [3]和Tadahiro Kuroda [4]在論文中深入討論了變化和優(yōu)化Vdd和Vth的影響。

以下等式定義了器件內(nèi)的功率:

泄漏 =(I二極管 +I亞閾值)* V

A=開關(guān)活動(dòng)

C=總負(fù)載電容

V=電源電壓

F=目標(biāo)頻率

B=增益系數(shù)

T=上升/下降時(shí)間(門輸入)

V th=電壓閾值

P 總計(jì) = P 動(dòng)態(tài) + P 短 + P 泄漏

P 開關(guān) = A * C * V 2 * F P short = A(B/12)(V-2V th ) 3 * F * T

注意,消耗不是恒定的,即使平均功率消耗,峰值功率也是由于電遷移和電壓下降引起的故障的一個(gè)重要問題離子很低。

我們可以做些什么來降低功耗

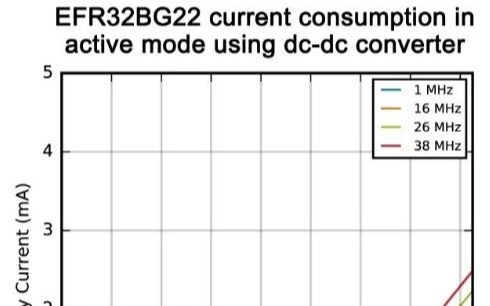

在針對低功耗應(yīng)用的SoC架構(gòu)中,我們必須首先完全理解將定義功率預(yù)算。這些可以源自某些形式的基于標(biāo)準(zhǔn)的要求,其限制在某些條件下的電流消耗,或者在移動(dòng)應(yīng)用的情況下可延長電池的壽命。針對目標(biāo)應(yīng)用的解決方案將在設(shè)備的控制和架構(gòu)方面有所不同。

一旦明確定義了要求,我們就可以開始探索各種架構(gòu)并確定潛在的權(quán)衡。從最高抽象層次開始,最大限度節(jié)省的潛力,并通過設(shè)計(jì)抽象層次進(jìn)一步完善,我們可以不斷將功率節(jié)省向下推向目標(biāo)預(yù)算。

圖2 - 通過抽象級別減少回報(bào)

在最終確定SoC架構(gòu)時(shí),需要在各個(gè)階段做出一些考慮和決定。設(shè)計(jì)抽象以達(dá)到最佳解決方案。這些要求包括系統(tǒng)性能,處理器和其他IP選擇,要設(shè)計(jì)的新模塊,目標(biāo)技術(shù),要考慮的電源域數(shù)量,目標(biāo)時(shí)鐘頻率,時(shí)鐘分配和結(jié)構(gòu),I/O要求,內(nèi)存要求,模擬功能和電壓調(diào)節(jié)。所有這些都是功率預(yù)算的貢獻(xiàn)者,因此可以針對功耗最小化來實(shí)現(xiàn)低功耗目標(biāo)。

在將架構(gòu)的所有部分組合在一起時(shí),接下來我們需要了解可用于降低系統(tǒng)總體功耗的全局控制和時(shí)鐘功能。對于各種應(yīng)用需求,設(shè)計(jì)可能有許多操作模式,例如啟動(dòng),活動(dòng),待機(jī),空閑和斷電。

在某些情況下,這些模式的多個(gè)級別將用于實(shí)現(xiàn)最佳的整體電源管理策略。這些模式通常通過軟件和硬件功能的組合來控制,并且需要從設(shè)計(jì)過程的早期階段計(jì)劃到系統(tǒng)開發(fā)中。

從前面描述的等式中,它可以可以看出,盡可能節(jié)省功率的最佳方法是將電壓調(diào)整到所需性能的最佳水平。然而,降低電壓電平的影響是增加?xùn)艠O延遲,并超出一定程度,這變得不可行。

理想的解決方案是采用不同的工作模式,目標(biāo)是盡可能減少給定應(yīng)用的設(shè)計(jì)電流,從而降低動(dòng)態(tài)和漏電功率。例如,在待機(jī)模式下,應(yīng)在低電壓域上維持所需的最小邏輯量,以便根據(jù)某些外部事件使設(shè)備退出此狀態(tài),然后通過操作模式轉(zhuǎn)換到所需的性能級別。

雖然此解決方案提供了最大的節(jié)省,但它在復(fù)雜性方面也帶來了最大的開銷。這些考慮因素包括片內(nèi)或片外開關(guān)調(diào)節(jié),電源域隔離,與切換和恢復(fù)穩(wěn)定電源相關(guān)的延遲的性能影響,以及觸發(fā)器和需要保存和恢復(fù)例程的存儲(chǔ)器的潛在狀態(tài)損失,以及所有其他相關(guān)的測試和驗(yàn)證要求。

在開發(fā)此類實(shí)施時(shí),需要考慮上述所有項(xiàng)目以及管理可實(shí)現(xiàn)這一目標(biāo)的時(shí)間段的可行性。

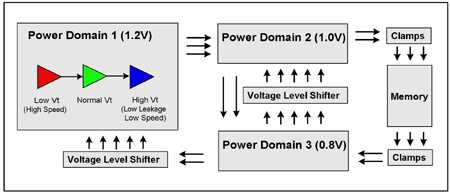

圖3 - 多域結(jié)構(gòu)示例

包含多個(gè)域但沒有切換或縮放的簡單實(shí)現(xiàn)將從二次電壓效應(yīng)中獲得一些相關(guān)的好處。在這些情況下,需要考慮將設(shè)計(jì)劃分為高性能/高電壓和低性能/低電壓。

在定義電壓分配和縮放后,下一級考慮應(yīng)該是系統(tǒng)級時(shí)鐘架構(gòu)和控制頻率和相關(guān)切換級別的方法。雖然它沒有通過泄漏解決功耗問題,但這種方法在降低器件的動(dòng)態(tài)功耗方面還有很長的路要走。

設(shè)計(jì)使時(shí)鐘分配和時(shí)鐘元素消耗超過設(shè)備總功耗的50%并不罕見[5]。注意,如果實(shí)現(xiàn)頻率縮放可以與任何電壓縮放成正比,以滿足所需的系統(tǒng)級性能。

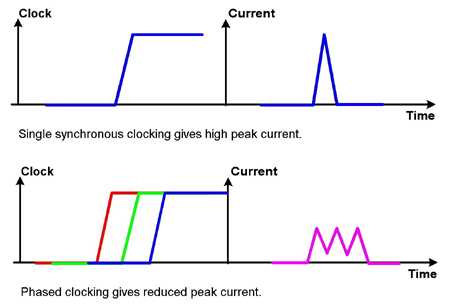

在給定的空閑或休眠模式下,所有非相關(guān)模塊都可以完全從樹的路徑中關(guān)閉,從而消除了設(shè)計(jì)這些部分中時(shí)鐘分布和邏輯的切換。使用多個(gè)時(shí)鐘域,頻率調(diào)整和頻率相位來降低峰值功率都可以從中央分配管理。

圖4 - 時(shí)鐘定相

時(shí)鐘架構(gòu)的控制通常通過處理器提供的軟件接口進(jìn)行控制。然而,也可以實(shí)現(xiàn)用于按需激活的動(dòng)態(tài)硬件控制切換 - 例如,在支持?jǐn)?shù)據(jù)流量突發(fā)所需的某些解碼器功能的情況下。這些類型的功能減少了總軟件序列支持和系統(tǒng)延遲。

在定義的系統(tǒng)時(shí)鐘架構(gòu)的所有上述實(shí)現(xiàn)方面,需要詳細(xì)考慮以避免所有形式的時(shí)鐘故障,額外的開銷在功能測試,偏斜控制,測試考慮設(shè)計(jì)和時(shí)序收斂影響方面與多個(gè)域相關(guān)聯(lián)。

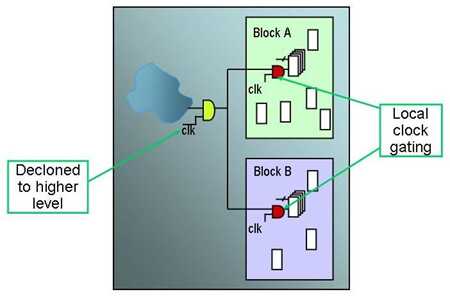

一旦捕獲了設(shè)計(jì)架構(gòu),RTL代碼現(xiàn)在可以針對低功耗合成流程,自動(dòng)交易權(quán)力以及普遍接受的表現(xiàn)和區(qū)域限制。這些工具的主要特點(diǎn)包括多閾值泄漏優(yōu)化,多電源電壓域,基于本地鎖存器的時(shí)鐘門控,去克隆和重新克隆重構(gòu),操作數(shù)隔離和門級功率優(yōu)化。

多閾值泄漏優(yōu)化,通常使用多達(dá)三個(gè)版本的目標(biāo)庫:低V th (快速,高泄漏),標(biāo)準(zhǔn)V th 和高V th (慢,低泄漏)。該工具將盡可能多地使用高閾值單元,同時(shí)保持時(shí)序約束,僅將低閾值單元用于關(guān)鍵路徑。顯然,選擇和定位適當(dāng)?shù)膸旌捅碚鲬?yīng)用程序性能要求是一個(gè)關(guān)鍵考慮因素,應(yīng)該在設(shè)計(jì)過程的早期解決。

圖5 - 多電壓閾值泄漏優(yōu)化

為了支持多個(gè)電壓域,需要針對目標(biāo)電壓的附加特征庫。這些還可以包括其中的多個(gè)閾值變體。功率方面的成本節(jié)省顯然與二次電壓縮放效應(yīng)有關(guān)。除了一致且支持的工具流程外,管理域分區(qū)還需要在開發(fā)的早期階段仔細(xì)考慮設(shè)計(jì),并在前端設(shè)計(jì)和布局處理之間進(jìn)行緊密集成,以支持上述所有方法。

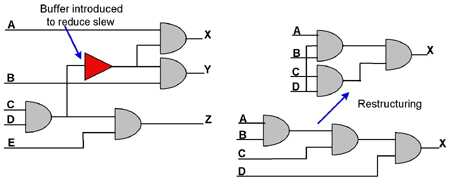

如果啟用,基于本地鎖存器的時(shí)鐘門控通常會(huì)在關(guān)聯(lián)觸發(fā)器的組或組之前盡可能插入特定于庫的時(shí)鐘門控鎖存器。這樣做的效果是減少不必要的時(shí)鐘切換到相關(guān)的觸發(fā)器。

用戶通常可以定義從單個(gè)時(shí)鐘門驅(qū)動(dòng)的觸發(fā)器范圍,以避免時(shí)鐘分配網(wǎng)絡(luò)中出現(xiàn)任何不必要的不平衡。每個(gè)時(shí)鐘門控單元為時(shí)鐘路徑提供功能和測試激活使能,如果需要達(dá)到所需的目標(biāo)ATPG覆蓋范圍,可選擇添加可觀察性。

關(guān)于時(shí)鐘門控,可以使用物理數(shù)據(jù)添加額外的步驟來重構(gòu)時(shí)鐘門控,從而進(jìn)一步降低功耗和面積。這是通過寄存器和門控單元的相對位置實(shí)現(xiàn)的,從而減少了碎片和復(fù)制。在可能的情況下,時(shí)鐘門控單元到觸發(fā)器的原始邏輯分區(qū)將被重構(gòu)以提供更物理的布局友好結(jié)構(gòu)。

圖7—時(shí)鐘門重組

完整的流程有很多步驟。在預(yù)布局設(shè)計(jì)中,本地時(shí)鐘門控被去克隆到更高的公共級別,減少了區(qū)域并為時(shí)鐘樹合成(CTS)創(chuàng)建了更清晰的起點(diǎn)。然后在詳細(xì)的放置/CTS階段,可以重新克隆本地時(shí)鐘門控單元以提供最佳的所需時(shí)鐘樹。

操作數(shù)隔離步驟自動(dòng)識別和關(guān)閉數(shù)據(jù)路徑元素和分層組合模塊共同的控制信號。該工具僅部分承諾重組,以實(shí)現(xiàn)最佳時(shí)序和功率權(quán)衡。

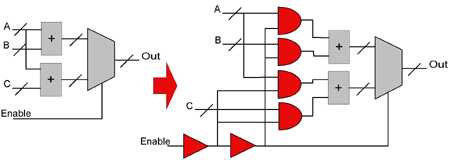

圖8—操作數(shù)隔離

經(jīng)典門級優(yōu)化調(diào)整單元大小,執(zhí)行引腳交換,刪除不必要的緩沖,合并門,添加緩沖區(qū)以減少壓擺,并重構(gòu)邏輯以提供最佳的功耗優(yōu)化。然而,這些步驟中的大多數(shù)也在具有實(shí)際布局和線長約束的物理域中重新進(jìn)行。

圖9—門級優(yōu)化中心

基線流與采用上述技術(shù)的低功耗合成流之間的比較數(shù)表明采用90納米技術(shù)的嵌入式處理器器件,大約650K門可以動(dòng)態(tài)開關(guān)電源和漏電功率可節(jié)省大于40%[6]。

-

soc

+關(guān)注

關(guān)注

38文章

4188瀏覽量

218618 -

低功耗設(shè)計(jì)

+關(guān)注

關(guān)注

0文章

80瀏覽量

16179

發(fā)布評論請先 登錄

相關(guān)推薦

Arm SoC芯片低功耗設(shè)計(jì)分享會(huì)在深圳成功舉辦

SoC低功耗設(shè)計(jì)

最新SOC低功耗帶學(xué)習(xí)碼接收方案

基于Foundation IP的低功耗IoT SoC實(shí)現(xiàn)

行業(yè)最低功耗藍(lán)牙SoC NCV-RSL10有什么優(yōu)勢?

如何設(shè)計(jì)超低功耗的嵌入式應(yīng)用?

【書籍評測活動(dòng)NO.19】 SoC底層軟件低功耗系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

《SoC底層軟件低功耗系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)》閱讀筆記

SoC的低功耗設(shè)計(jì)

如何選擇低功耗藍(lán)牙SoC

低功耗藍(lán)牙模塊備受歡迎的原因有哪些?

低功耗SoC設(shè)計(jì)的原因有哪些

低功耗SoC設(shè)計(jì)的原因有哪些

評論