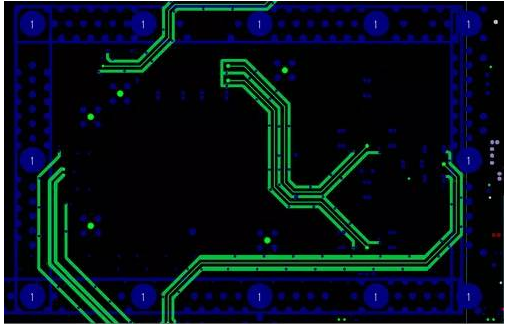

為什么在PCB設計中盡可能使用地平面?接地平面減小了信號返回路徑的電感。反過來,這可以最大限度地減少瞬態接地電流產生的噪聲。

在本文中,我們將討論信號路徑如何在多層PCB上工作以及返回路徑電感的概念。

信號選擇最小阻抗路徑

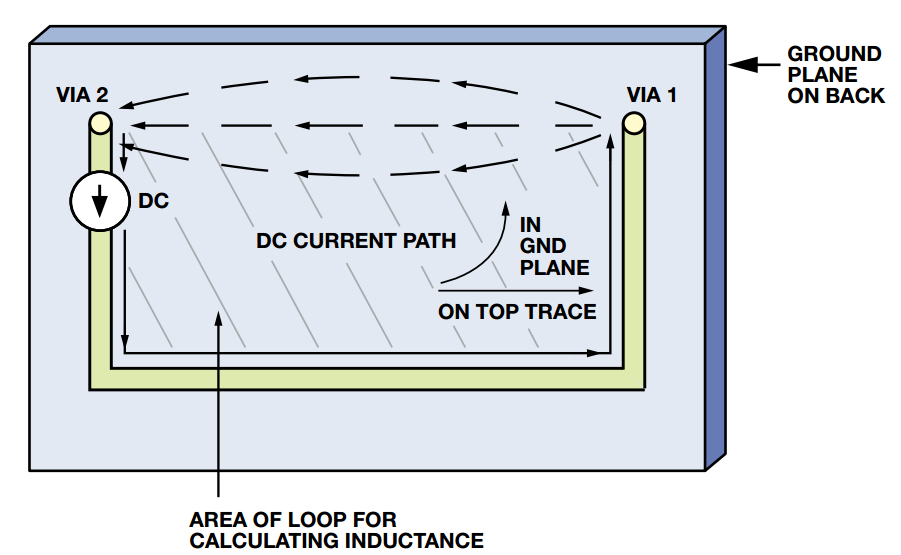

考慮一個雙層電路板,如圖1所示。底層是接地層,電流源是連接到頂層的U形跡線。頂層跡線通過VIA1和VIA2連接到底層。

首先,如圖所示在圖2中,DC電流注入頂層跡線。

圖2。圖片由ADI公司提供。

電流沿著U形跡線下降。然后,通過VIA1,它到達地平面。地平面的哪一部分將電流傳回VIA2?我們可以將地平面設想為無限數量的并行的窄軌跡。電流將選擇具有相對較小阻抗的跡線。由于從VIA1到VIA2的直接路徑最短并且電阻最小,因此大部分電流將流過該路徑。當我們離開這條阻力最小的路徑時,電流密度會迅速下降。

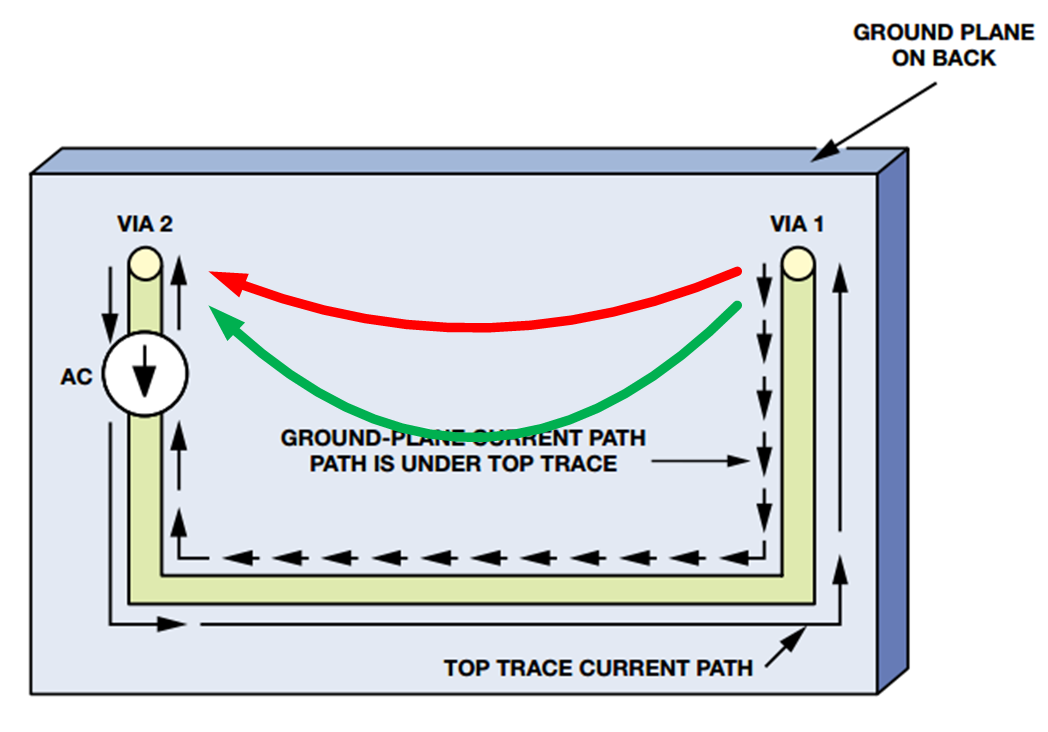

現在,我們假設我們將一個交流電流注入U形跡線。

它會不會采用相同的直流電流路徑?

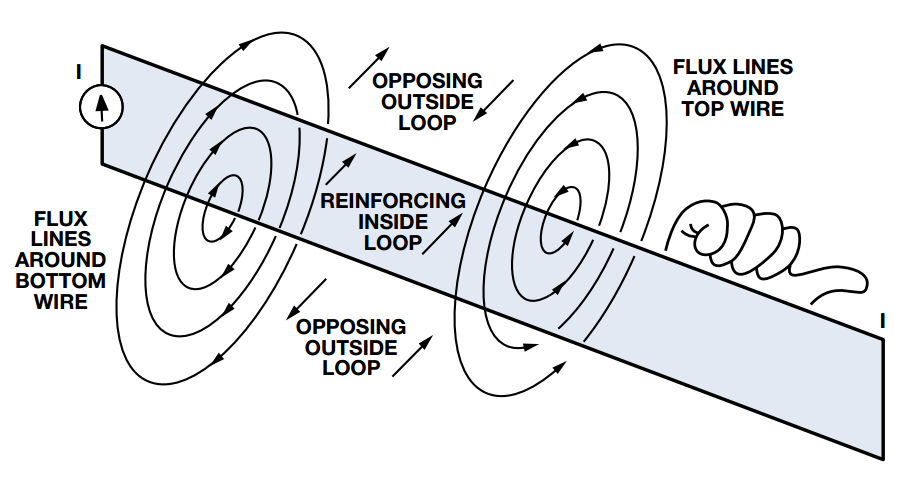

直流電流采用阻抗最小(或最小電阻)的路徑。對于AC電流,阻抗取決于路徑的電阻和電感。雖然最短路徑提供最小電阻,但它不一定提供最小電感。路徑的電感取決于電流產生的環路面積。圖3顯示了信號跟蹤及其返回路徑創建的示例電流環路。如果由電流產生的環路面積增加,則電感將按比例增加。

圖3。圖片由ADI公司提供。

例如,紅色返回路徑在圖4中,創建了一個比綠色路徑更大的循環。因此,在這兩條路徑之間,AC電流通過綠色路徑,其具有較小的電感。對于路徑的總阻抗,我們實際上應該考慮電阻和電感。然而,隨著AC信號的頻率增加,電感對路徑阻抗的貢獻最終變得大于電阻的數量級。因此,如圖4所示,高頻返回電流將直接在U形跡線下方流動,以最小化環路面積(為簡單起見,我們忽略了路徑電阻)。當我們在地平面上遠離這條路徑時,電流密度會迅速下降。

圖4。圖片由ADI公司提供

對于上面的例子,我們有一個可以設想為無限多個窄平行路徑的地平面。返回電流流過那些使阻抗最小化的路徑。使用雙層電路板,我們買不起地平面。在這種情況下,我們可能有一條軌道(而不是一個平面)用于返回電流。即使電流可能表現出很大的電感,也要強制電流經過這條路徑。對于雙層電路板的一些關鍵信號走線(例如時鐘信號),我們可以路由適當的返回路徑,但我們不能對電路板上的所有走線執行此操作。我們如何降低雙面電路板上所有走線的電流路徑電感?我們將很快討論雙層電路板的高效接地系統,但在此之前,我們先簡要介紹接地路徑電感增加電路板噪聲的機制。

為什么返回路徑電感很重要?

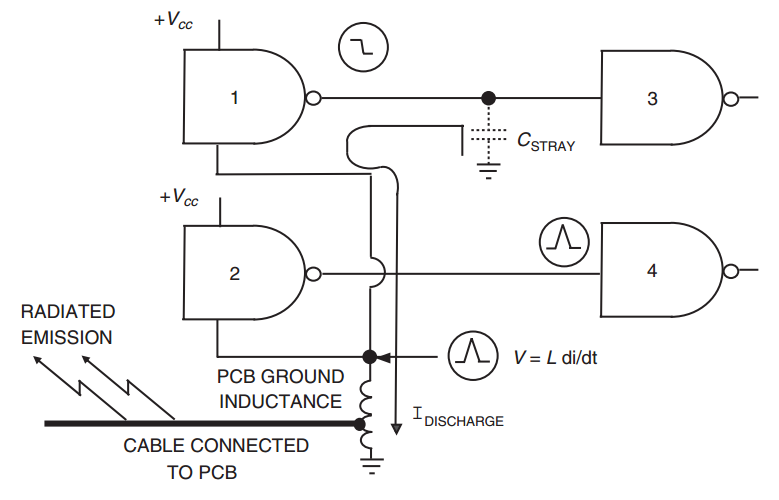

通過將電感器與電路原理圖的接地串聯,可以得到一個簡單的返回路徑電感模型。一個例子如圖5所示。假設門1的輸出從邏輯高變為邏輯低。這將通過接地路徑釋放存儲在C STRAY 中的電荷。考慮到今天的快速邏輯門,放電將在很短的時間內完成(Δ t )。放電電流將流過接地電感。如果通過電感的電流在邏輯轉換期間改變Δ I ,則邏輯門的地將反彈$ V = L \ frac {ΔI} {Δt} $$。/p>

在這種情況下,處于邏輯低電平的柵極輸出(圖4中的柵極2)將經歷噪聲電壓脈沖。如果足夠大,這個噪聲電壓可能會導致柵極4輸出端產生不必要的轉換。

此外,如圖4所示,接地噪聲電壓可以耦合到離開PCB的電纜。作為天線,這些電纜會輻射并引起EMC問題。

圖5顯示了另一種有趣的機制,接地電感可能會導致問題。當柵極1的輸出從邏輯高轉變為邏輯低時,柵極1內的晶體管將雜散電容連接到由接地路徑產生的電感器。如果連接CSTRAY和地電感的晶體管呈現小電阻,則會產生高Q串聯諧振電路。這可能導致邏輯門轉換具有相當大的振鈴。如果我們不能充分降低接地電感,我們可能需要在柵極輸出端串聯一個電阻(例如51Ω)來抑制振鈴。

圖5.圖片由電磁兼容工程提供。

上述噪聲機制表明,在設計PCB時,接地路徑電感至關重要。如前所述,多層板允許我們具有堅固的接地層,這可以顯著降低接地電感。但是,對于雙面電路板,我們必須采用其他技術來實現低電感接地系統。

-

pcb

+關注

關注

4319文章

23099瀏覽量

397923 -

PCB設計

+關注

關注

394文章

4688瀏覽量

85649 -

華強pcb線路板打樣

+關注

關注

5文章

14629瀏覽量

43045

發布評論請先 登錄

相關推薦

場效應管驅動電路設計 如何降低場效應管的噪聲

怎樣準確合理測試單板上DAC80504輸入的系統噪聲?

哪些措施能降低電機的噪聲?

電源濾波器是如何降低電源噪聲的

求助,關于運算放大器反饋電路PCB布局請教

降低PCB熱阻的設計方法有哪些

采用電容器來降低噪聲的方法

EMC之PCB設計技巧

PCB噪聲怎樣做可以較好的降低

PCB噪聲怎樣做可以較好的降低

評論