高密度互連或HDI基板是多層,高密度電路,具有細(xì)線和明確定義的空間圖案等特征。越來越多的HDI基板的采用增強(qiáng)了PCB的整體功能并限制了操作區(qū)域。

將HDI板與其他類型板區(qū)分開來的關(guān)鍵因素之一是其獨(dú)特的設(shè)計(jì),其中包括多層銅填充微通孔。這些多層微通孔實(shí)現(xiàn)了垂直互連。此外,高密度互連(HDI)基板提供的優(yōu)點(diǎn)包括更高的集成度和更好的兩側(cè)元件放置。此外,HDI板由較小數(shù)量的I/O組成。高密度互連(HDI)基板的其他功能包括更快的信號傳輸和顯著減少信號損失和交叉延遲。

最近采用的HDI板制備技術(shù)涉及組件的小型化并采用高端設(shè)備。但是,串?dāng)_等挑戰(zhàn)會(huì)對HDI板的性能產(chǎn)生不同的影響。因此,避免HDI電路板中的串?dāng)_變得至關(guān)重要。

HDI電路板中的串?dāng)_生成

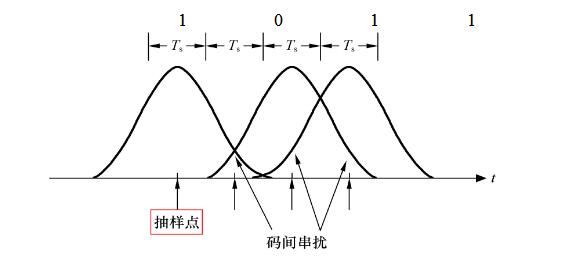

無意識跡線和組件之間的電磁耦合被定義為電子電路中的串?dāng)_。此外,由于外部干擾,電磁場干擾可能發(fā)生在PCB中。串?dāng)_會(huì)產(chǎn)生不良影響,影響時(shí)鐘,周期信號,系統(tǒng)關(guān)鍵網(wǎng)絡(luò),如數(shù)據(jù)線,控制信號和I/O.此外,受影響的時(shí)鐘和周期性信號會(huì)對工作PCB和組件組件產(chǎn)生嚴(yán)重的功能影響。串?dāng)_導(dǎo)致電容和電感耦合。 HDI基板中的電容耦合發(fā)生在其中一條跡線位于另一條跡線上時(shí)。

避免串?dāng)_的方法

HDI基板中的串?dāng)_因較短而減少耦合長度和較低介電常數(shù)高達(dá)50%。可以限制HDI基板中串?dāng)_的其他因素包括,

使用較低的Dk材料。

HDI材料系統(tǒng)的較低介電常數(shù)可使電路板收縮至28%。

距離越短對于參考平面,近端串?dāng)_將越低。

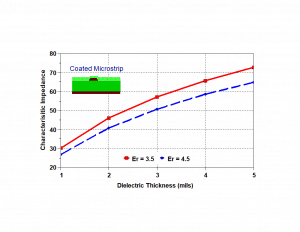

HDI小型化提供更短的互連長度,如果使用更低介電常數(shù)材料,則HDI基板中的串?dāng)_減少。Eric Bogatin,Teledyne Lecroy的信號完整性宣傳員提供了以下示例:“HDI技術(shù)中的典型線寬為3密耳(75微米)。下圖顯示了各種介電厚度下3密耳寬跡線的特征阻抗。

介電常數(shù)較低時(shí),介電厚度較小。這意味著較低介電常數(shù)的材料系統(tǒng)可以在相同的間距下產(chǎn)生更少的串?dāng)_,或者跡線可以更靠近在一起并具有相同的串?dāng)_量。“

介電厚度與受控阻抗

案例研究

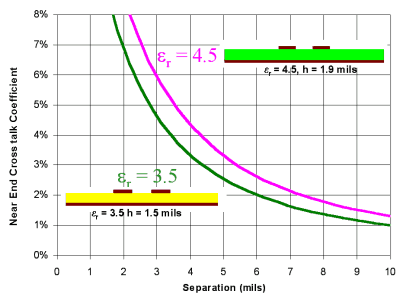

Eric Bogation繼續(xù)說道,“在研究了兩種情況,線寬為3密耳,并調(diào)整了介電厚度,使得對于兩種不同的介電常數(shù),線阻抗是相同的。從這些曲線可以看出,如果布線間距受串?dāng)_約束,則HDI材料系統(tǒng)的較低介電常數(shù)可能使電路板縮小至28%。

對于耦合長度小于飽和長度,近端電壓噪聲的大小將隨著長度而變化。飽和長度取決于上升時(shí)間。對于1納秒的上升時(shí)間,有效介電常數(shù)為2.5的飽和長度約為7.6英寸,這將包括小卡應(yīng)用中的許多跡線。相對耦合的近端噪聲將由下式給出:

近端串?dāng)_系數(shù)

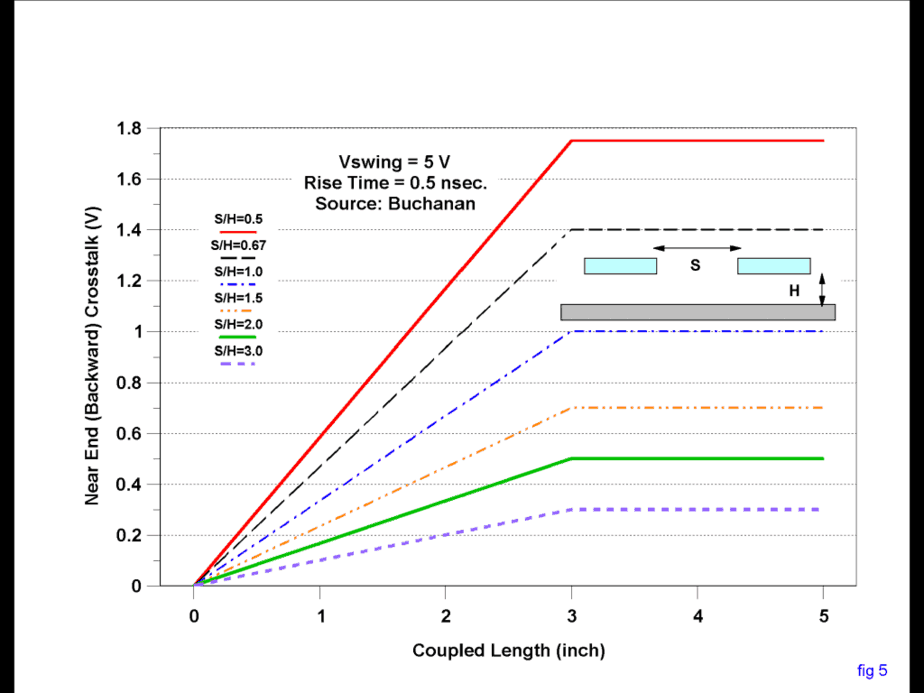

HDI基板中的串?dāng)_減少了較短的耦合長度和較低的介電常數(shù)可達(dá)50%。較短的走線長度將輻射較少,而具有較薄電介質(zhì)的走線將輻射較少。下面的例子表明,耦合長度越短,互感(Lm)越小,走線越薄,互電容(Cm)越小。

耦合長度

此外,距參考平面的距離越近,近端串?dāng)_越小,或者耦合長度越長,串?dāng)_越小。與傳統(tǒng)電路板相比,長度減少2倍,電介質(zhì)厚度減少2倍,HDI信號環(huán)路的輻射場可能會(huì)減少4倍,即12 dB。“

Eric Bogatin進(jìn)一步指出,“如果整個(gè)電路板都是HDI,而不僅僅是幾個(gè)外層,那么控制返回路徑可能比通孔電路板更具挑戰(zhàn)性。”

Eric Bogatin的關(guān)鍵要點(diǎn):

”你必須注意HDI基板中的相同問題:

提供連續(xù)的返回路徑。

工程控制的阻抗互連。

在具有最小存根長度的線性菊花鏈路徑中進(jìn)行路由。

使用終端管理反射噪聲。

通過返回路徑控制來控制通過串?dāng)_。

使用連接到IC引腳的低電感電容。

與通孔核心相結(jié)合,HDI互連非常有價(jià)值。“

信號完整性挑戰(zhàn)和結(jié)論

我們非常熟悉信號完整性及其在確定高速PCB設(shè)計(jì)性能中的作用。串?dāng)_是影響信號完整性的關(guān)鍵參數(shù)之一。串?dāng)_可能直接導(dǎo)致接收器信號失真。因此,設(shè)計(jì)人員最關(guān)心的是將HDI基板中串?dāng)_的影響降至最低。

不要在自己之間串?dāng)_,向我們詢問任何問題。我們在這里等你。

-

HDI

+關(guān)注

關(guān)注

6文章

201瀏覽量

21328 -

串?dāng)_

+關(guān)注

關(guān)注

4文章

189瀏覽量

26970 -

可制造性設(shè)計(jì)

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15657 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3494瀏覽量

4657

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計(jì)中如何避免串擾

PCB設(shè)計(jì)中避免串擾的方法

PCB設(shè)計(jì)中,如何避免串擾

超深亞微米設(shè)計(jì)中串擾的影響及避免

PCB設(shè)計(jì)中,如何避免串擾

PCB設(shè)計(jì)中串擾的產(chǎn)生以及如何避免

如何消除碼間串擾_怎么避免碼間串擾

HDI基板中的串?dāng)_怎么避免

HDI基板中的串?dāng)_怎么避免

評論