聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65428 -

網(wǎng)絡(luò)

+關(guān)注

關(guān)注

14文章

7589瀏覽量

89031 -

研討會(huì)

+關(guān)注

關(guān)注

0文章

104瀏覽量

36101

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談DDR6 RAM設(shè)計(jì)挑戰(zhàn)

DDR6 RAM 是 目前DDR 迭代中的最新版本,最大的數(shù)據(jù)速率峰值超過 12000 MT/s。

DDR3、DDR4、DDR5的性能對(duì)比

DDR3、DDR4、DDR5是計(jì)算機(jī)內(nèi)存類型的不同階段,分別代表第三代、第四代和第五代雙倍數(shù)據(jù)速率同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器(SDRAM)。以下是它們之間的性能對(duì)比: 一、速度與帶寬 DDR

DDR5內(nèi)存與DDR4內(nèi)存性能差異

DDR5內(nèi)存與DDR4內(nèi)存性能差異 隨著技術(shù)的發(fā)展,內(nèi)存技術(shù)也在不斷進(jìn)步。DDR5內(nèi)存作為新一代的內(nèi)存技術(shù),相較于DDR4內(nèi)存,在性能上有著顯著的提升。 1. 數(shù)據(jù)傳輸速率

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

的數(shù)據(jù)傳輸速率、更大的容量和更低的功耗。 2. DDR5內(nèi)存工作原理 DDR5內(nèi)存的工作原理基于雙倍數(shù)據(jù)速率技術(shù),即在每個(gè)時(shí)鐘周期內(nèi)傳輸兩次數(shù)據(jù)。DDR5內(nèi)存通過提高數(shù)據(jù)傳輸速率、增加數(shù)據(jù)預(yù)取和優(yōu)化功耗

如何選擇DDR內(nèi)存條 DDR3與DDR4內(nèi)存區(qū)別

隨著技術(shù)的不斷進(jìn)步,計(jì)算機(jī)內(nèi)存技術(shù)也在不斷發(fā)展。DDR(Double Data Rate)內(nèi)存條作為計(jì)算機(jī)的重要組成部分,其性能直接影響到電腦的運(yùn)行速度和穩(wěn)定性。DDR3和DDR4是目前市場(chǎng)上最常

一文讀懂DDR內(nèi)存基礎(chǔ)知識(shí)

無論對(duì)于芯片設(shè)計(jì)商還是器件制造商來說,DDR內(nèi)存可謂是無處不在——除了在服務(wù)器、工作站和臺(tái)式機(jī)中之外,還會(huì)內(nèi)置在消費(fèi)類電子產(chǎn)品、汽車和其他系統(tǒng)設(shè)計(jì)中。每一代新的 DDR(雙倍數(shù)據(jù)速率)

DDR Inline ECC在Jacinto7 SoC中的應(yīng)用

電子發(fā)燒友網(wǎng)站提供《DDR Inline ECC在Jacinto7 SoC中的應(yīng)用.pdf》資料免費(fèi)下載

發(fā)表于 09-27 11:04

?0次下載

DDR的工作原理與應(yīng)用

在高速信號(hào)設(shè)計(jì)中,DDR仿真被廣泛應(yīng)用于驗(yàn)證信號(hào)完整性。隨著電子產(chǎn)品向小型化、精密化和高速化發(fā)展,DDR等高速通道的設(shè)計(jì)需要全面考慮從發(fā)送端、傳輸線到接收端的整個(gè)通信鏈路。DDR仿真可

0706線下活動(dòng) I DDR4/DDR5內(nèi)存技術(shù)高速信號(hào)專題設(shè)計(jì)技術(shù)交流活動(dòng)

米)02活動(dòng)內(nèi)容1、本次活動(dòng)重點(diǎn)分析DDR4/DDR5的內(nèi)存控制原理,內(nèi)存控制技術(shù)中的讀寫原理方法、原理圖設(shè)計(jì)和關(guān)鍵的信號(hào)特征。講解DDR4/DDR

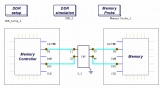

基于FPGA的DDR3多端口讀寫存儲(chǔ)管理設(shè)計(jì)

今天給大俠帶來《基于FPGA的DDR3多端口讀寫存儲(chǔ)管理設(shè)計(jì)》,話不多說,上貨。

摘要

為了解決視頻圖形顯示系統(tǒng)中多個(gè)端口訪問DDR3時(shí)出現(xiàn)的數(shù)據(jù)存儲(chǔ)沖突問題,設(shè)計(jì)了一種基于

發(fā)表于 06-26 18:13

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)表

電子發(fā)燒友網(wǎng)站提供《全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免

發(fā)表于 04-09 09:51

?7次下載

適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準(zhǔn)的TPS51206 2A峰值灌電流/拉電流DDR終端穩(wěn)壓器數(shù)據(jù)表

電子發(fā)燒友網(wǎng)站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準(zhǔn)的TPS51206 2A峰值灌電流/拉電流DDR

發(fā)表于 03-13 13:53

?1次下載

完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表

電子發(fā)燒友網(wǎng)站提供《完整的DDR、DDR2和DDR3內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)表.pdf》資料免費(fèi)下載

發(fā)表于 03-13 10:16

?1次下載

如何管理設(shè)計(jì)中的DDR問題

如何管理設(shè)計(jì)中的DDR問題

評(píng)論