知存科技的該項專利是關于數模混合存算一體芯片技術,除能有效降低設計復雜度和制造成本外,還特別適用于人工智能神經網絡的運算。

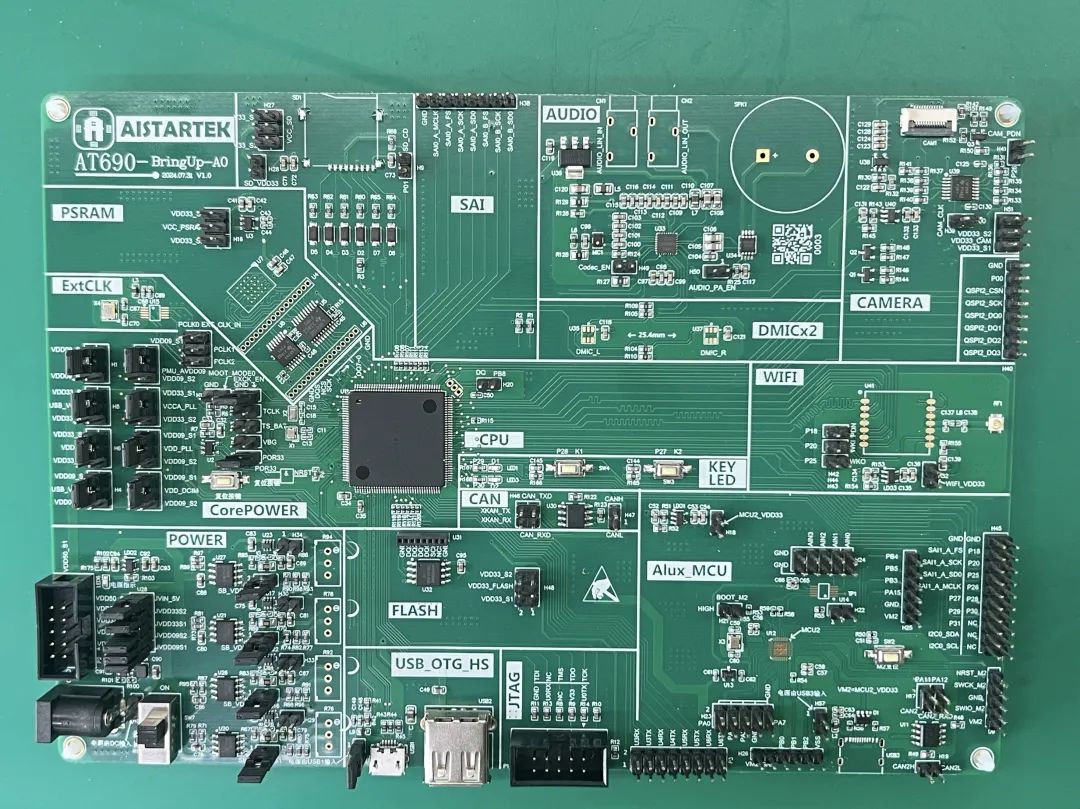

集微網消息,近年來,存算一體芯片架構開始得到人們的廣泛關注與研究,尤其是在AI快速發展的時代,人們對這種架構的需求也越來越多。近期,新興獨角獸存算一體芯片公司——“知存科技”就獲得了近億元人民幣的A輪融資,此次融資主要用來完成“存算一體”新品的量產。

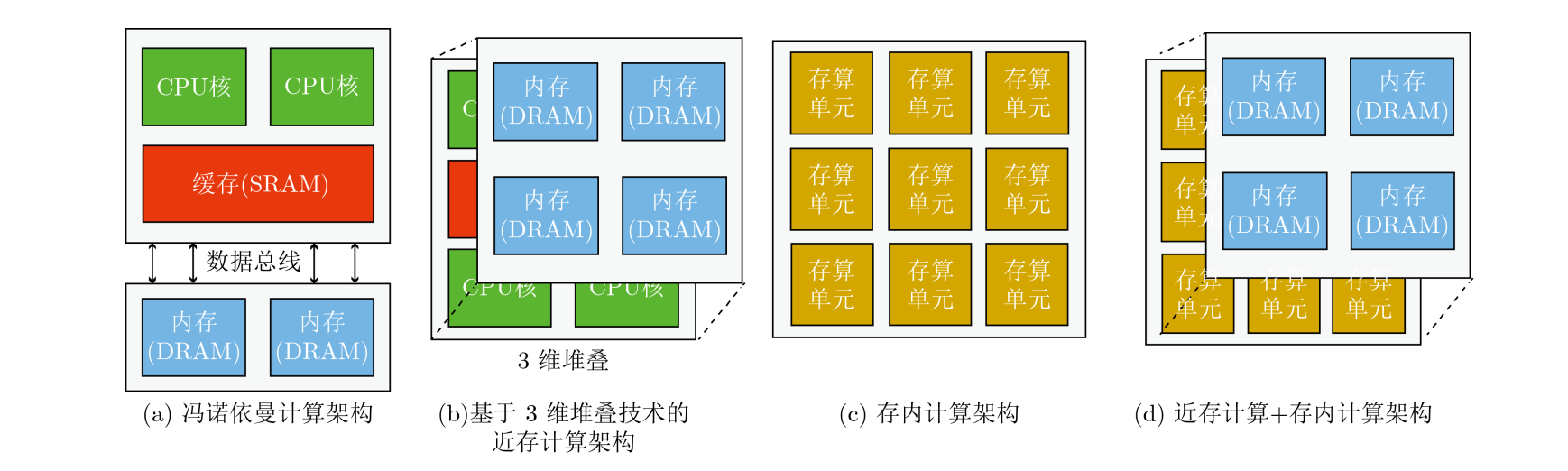

傳統存算一體芯片架構的基本思想是通過在存儲器中內置邏輯計算單元,從而把一些簡單但數據量又很大的邏輯計算功能放在存儲器中完成,以減少存儲器與處理器之間的數據傳輸量以及傳輸距離。但隨著人工智能技術的迅速發展,神經網絡作為人工智能中的主要技術分支得到了廣泛的應用,各種神經網絡算法層出不窮。但是,當前實現神經網絡算法主要依賴于計算機或大規模的處理器,使得終端設備體積受限、成本較高,不利于神經網絡的推廣應用。

為了解決以上問題,知存科技申請了一項名為“一種數模混合存算一體芯片以及用于神經網絡的運算裝置”的實用新型專利(申請號:201821979648.8),申請人為北京知存科技有限公司。

該專利提出的數模混合存算一體芯片能有效降低設計復雜度和制造成本,利于大規模產業化,并增加了設計的靈活性,延長閃存的使用壽命,可以用于神經網絡運算等場合。

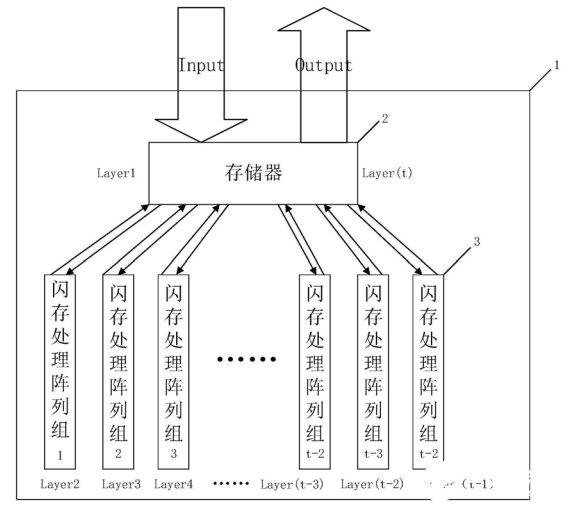

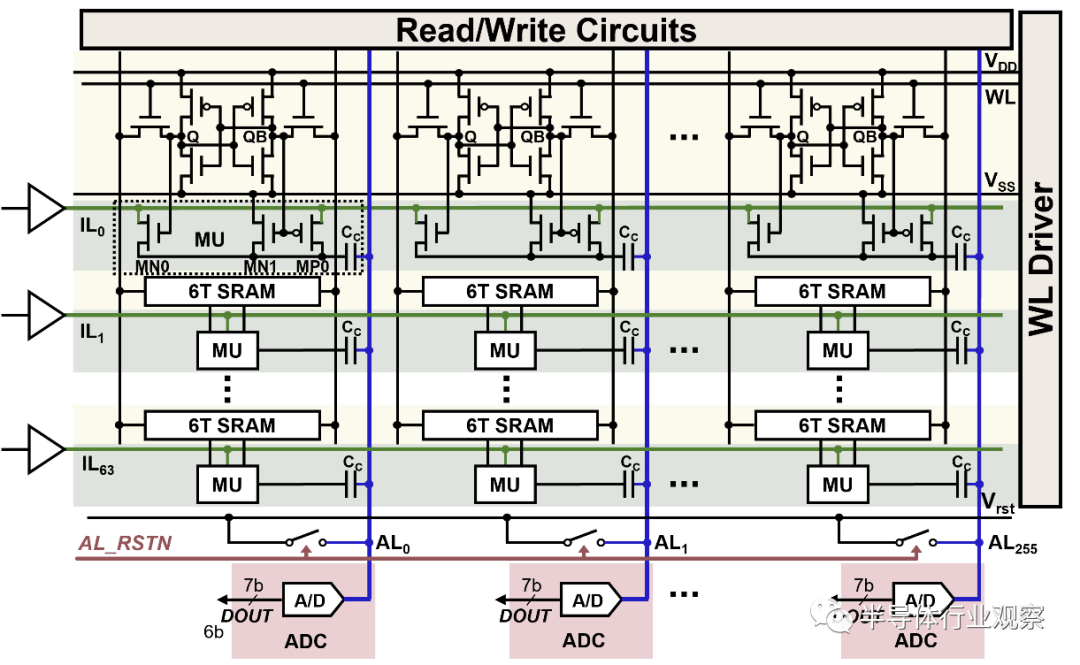

圖1

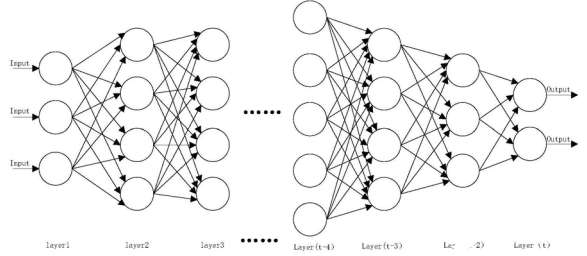

圖2

圖1為利用本實用新型實例一種數模混合存算一體芯片實現圖2所示神經網絡運算的系統圖。如圖1所示,該存算一體芯片1包括:片上存儲器2以及多個閃存處理陣列。

其中,片上存儲器用于實現圖2所示的Layer1和Layer(t)層,即接收從外部設備傳來的待處理數據并將Layer(t-1)層得到的運算結果進行輸出,在此基礎上,該片上存儲器還用于存儲各個閃存處理陣列的待處理數據。然后對多個閃存處理陣列進行分組,得到t-2個閃存處理陣列組,其中,每個閃存處理陣列都用于實現神經網絡中部分神經元的運算,并將運算結果存儲于片上存儲器。第1閃存處理陣列組~第t-2閃存處理陣列組分別用于實現圖2中示出的Layer2~Layer(t-1) 層。

當圖中所示的神經網絡為訓練合格的神經網絡時,該存算一體芯片可以用于這個模型的應用,即根據訓練合格的神經網絡的權重參數,設置各可編程半導體器件的閾值電壓,然后將待處理數據輸入至該數模混合存算一體芯片進行運算,即可實現神經網絡的前向傳播應用過程,而最終運算結果將作為實際結果用于后續流程使用。

當該神經網絡為未合格的神經網絡時,需要對該神經網絡進行訓練,此時,該存算一體芯片也能適應模型訓練需求。該芯片將最終結果輸出至外部設備,外部設備對該最終結果進行判斷,若滿足要求,則神經網絡訓練合格,若不滿足需求,還需要利用此芯片中的控制器、編程電路配合,調節各可編程半導體器件的閾值電壓,實現對神經網絡參數的反向調節,之后再將訓練數據輸入至網絡進行正向傳播,再進行反向調節,如此反復操作,即可完成模型訓練的整個流程。

通過上述分析可知,本專利所提出的數模混合存算一體芯片不僅適用于已訓練好的成熟的神經網絡模型的應用,還適于神經網絡模型的訓練過程,其適用性較好。而且集成度高、體積小,利于在電子設備中集成,極大降低了神經網絡運算的硬件成本,通過在芯片內部集成片上存儲器,還可以減少與芯片外部設備的交互。

“存算一體”架構的芯片打破了傳統的馮諾依曼架構(存儲器和處理器分離),知存科技在“存算一體”架構的基礎上,又實現了神經網絡計算的功能,為“存算一體”芯片的發展又推動了一步,希望該此類芯片量產后可以盡快的投入到市場中,為人工智能的發展做出更大的努力。

-

存儲器

+關注

關注

38文章

7493瀏覽量

163866 -

神經網絡

+關注

關注

42文章

4772瀏覽量

100792 -

AI

+關注

關注

87文章

30919瀏覽量

269170 -

存算一體

+關注

關注

0文章

102瀏覽量

4302

發布評論請先 登錄

相關推薦

知存科技詹慕航:AI蓬勃發展,存算一體走向AI芯片的主流架構

直播預約 |開源芯片系列講座第24期:SRAM存算一體:賦能高能效RISC-V計算

存算一體化與邊緣計算:重新定義智能計算的未來

知存科技榮獲2024中國AI算力層創新企業

存算一體架構創新助力國產大算力AI芯片騰飛

科技新突破:首款支持多模態存算一體AI芯片成功問世

后摩智能推出邊端大模型AI芯片M30,展現出存算一體架構優勢

知存科技助力AI應用落地:WTMDK2101-ZT1評估板實地評測與性能揭秘

探索存內計算—基于 SRAM 的存內計算與基于 MRAM 的存算一體的探究

知存科技助力AI應用落地:WTMDK2101-ZT1評估板實地評測與性能揭秘

知存科技數模混合存算一體AI芯片專利解析

知存科技數模混合存算一體AI芯片專利解析

評論