FPGA的應(yīng)用越來越廣泛,隨著制造工藝水平的不斷提升,越來越高的器件密度以及性能使得功耗因數(shù)在FPGA設(shè)計(jì)中越來越重要。器件中元件模塊的種類和數(shù)量對FPGA設(shè)計(jì)中功耗的動(dòng)態(tài)范圍影響較大,對FPGA的電源功耗進(jìn)行了分析,并介紹了如何利用Altera公司的PowerPlay Early Power Estimator這一工具在設(shè)計(jì)前期盡可能準(zhǔn)確地估計(jì)功耗并通過估計(jì)功耗對硬件設(shè)計(jì)進(jìn)行優(yōu)化選擇。

引 言

當(dāng)前FPGA應(yīng)用越來越廣泛,在高性能FPGA設(shè)計(jì)中,越來越高的器件密度以及性能使得功耗因數(shù)更加重要。大規(guī)模器件在實(shí)現(xiàn)更多的系統(tǒng)功能,以更高的速度運(yùn)行并完成更高級的功能的同時(shí),功耗必然會更大。開發(fā)者在面對此類設(shè)計(jì)時(shí)會在功耗方面遇到很多挑戰(zhàn)。對通過芯片重新編程就能夠修改的FPGA設(shè)計(jì),在設(shè)計(jì)過程中盡早完成電源供電和散熱方案的設(shè)計(jì)有利于加速整個(gè)系統(tǒng)的實(shí)現(xiàn)。設(shè)計(jì)中系統(tǒng)組件應(yīng)保持在一定的功耗預(yù)算范圍內(nèi),如果超出預(yù)算則需要重新設(shè)計(jì)供電電源及散熱方案,這會延長設(shè)計(jì)周期。同時(shí)較大的電源和散熱硬件會增加成本,降低功耗也就降低了系統(tǒng)總成本。并且當(dāng)設(shè)計(jì)中需要的風(fēng)扇和散熱硬件越多,系統(tǒng)故障的概率就越大,這將影響系統(tǒng)的可靠性。綜上所述,做好早期功率估算具有重大意義。

1、 FPGA器件功耗分析

當(dāng)前,隨著FPGA器件的封裝尺寸越來越小,密度越來越大,同時(shí)系統(tǒng)對器件的性能和可靠性要求不斷提高,功耗預(yù)算對電源方案,散熱方案及系統(tǒng)故障影響的問題已不容忽視。

1.1 功耗的組成

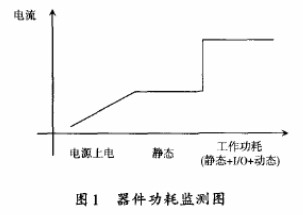

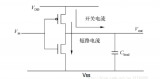

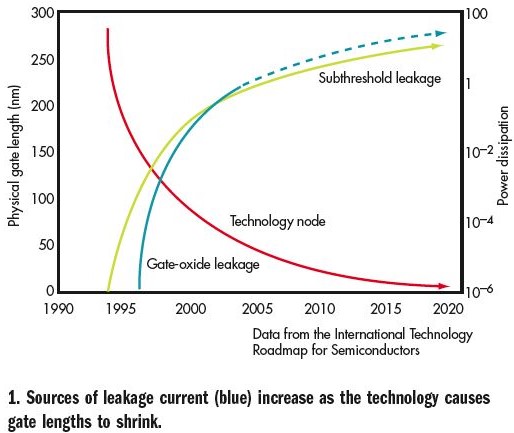

功耗一般由兩部分組成:靜態(tài)功耗和動(dòng)態(tài)功耗。靜態(tài)功耗也稱為待機(jī)功耗,是指邏輯門沒有開關(guān)活動(dòng)時(shí)的功率消耗,主要是由晶體管的漏電流引起,由源極到漏極的漏電流以及柵極到襯底的漏電流組成,圖1中靜態(tài)部分顯示了器件的靜態(tài)功耗。圖中最后階段顯示的是器件正常工作時(shí)的功耗,工作功耗同時(shí)包括靜態(tài)功耗,I/O以及動(dòng)態(tài)功耗。動(dòng)態(tài)功耗是指邏輯門開關(guān)活動(dòng)時(shí)的功率消耗,主要由電容充放電引起,其主要的影響參數(shù)是電壓、節(jié)點(diǎn)電容、工作頻率和資源使用情況,不同設(shè)計(jì)時(shí)期的動(dòng)態(tài)功耗和相應(yīng)的總功耗會有很大的差別。在傳統(tǒng)器件中動(dòng)態(tài)功耗占據(jù)主要地位,但在新的28 nm工藝的器件中,靜態(tài)功耗的比重增長很大,基本和動(dòng)態(tài)功耗處于同等地位。同時(shí)根據(jù)FPGA設(shè)計(jì)面向?qū)ο蟮牟煌牡谋戎匾矔胁顒e。當(dāng)設(shè)計(jì)面向算法時(shí),動(dòng)態(tài)功耗將占較多比重,當(dāng)設(shè)計(jì)面向控制功能時(shí),靜態(tài)功耗將占較多的比重。

1.2 靜態(tài)功耗

靜態(tài)功耗的產(chǎn)生主要取決于所選的FPGA產(chǎn)品,一般不會隨著設(shè)計(jì)資源的使用情況而變化,但是靜態(tài)功耗也會受到器件所選擇的工作模式、I/O的使用、工作溫度以及所選器件電源的影響。使用邏輯單元較多的器件含有較多的晶體管,因此其靜態(tài)功耗會高一些,所以設(shè)計(jì)者應(yīng)查看所選器件的數(shù)據(jù)資料,詳細(xì)了解其靜態(tài)功耗。在不同溫度環(huán)境中,靜態(tài)功耗也會隨著溫度的升高而增大,此時(shí)高效的散熱解決方案能有效地解決這一問題。因此在設(shè)計(jì)電源時(shí),應(yīng)針對選擇的器件和工作環(huán)境,選擇適合的靜態(tài)功耗規(guī)范。

1.3 動(dòng)態(tài)功耗

不同的設(shè)計(jì)有不同的動(dòng)態(tài)功耗,當(dāng)開發(fā)低功耗FPGA設(shè)計(jì)時(shí),動(dòng)態(tài)功耗是更可控的功耗分量,如下式:

影響動(dòng)態(tài)功耗的因素包括:器件中晶體管電容充電,工作電壓,晶體管開關(guān)的瞬間短路電流功耗,設(shè)計(jì)的工作頻率,以及被稱為電路活動(dòng)的每一時(shí)鐘周期觸發(fā)器開關(guān)的次數(shù)。設(shè)計(jì)人員根據(jù)設(shè)計(jì)要求決定工作電壓,工作頻率以及信號活動(dòng)。信號活動(dòng)包括觸發(fā)率和靜態(tài)概率。信號觸發(fā)率是精確估算動(dòng)態(tài)功耗的關(guān)鍵因素,隨著觸發(fā)率的增加,動(dòng)態(tài)功耗也線性增大。而靜態(tài)概率主要影響靜態(tài)功耗。

1.4 低功耗的優(yōu)點(diǎn)

低功耗器件的優(yōu)點(diǎn)主要有以下幾項(xiàng):首先可以選用低成本的電源系統(tǒng),進(jìn)而可以使用更少的元件和更小的PCB板面積,為設(shè)計(jì)節(jié)約了成本。其次低功耗器件引起的結(jié)溫更小,因此可以防止熱失控,可以少用或不用散熱器,而且結(jié)溫的降低可以提高系統(tǒng)的可靠性。最后低功耗可以延長器件的使用壽命,器件的工作溫度每降低10 ℃,使用壽命延長1倍。因此,在FPGA設(shè)計(jì)中,降低功耗直接提高了整個(gè)系統(tǒng)的性能和質(zhì)量并降低了成本,對系統(tǒng)的開發(fā)有積極作用。

通過對FPGA功耗的相關(guān)組成和影響功耗相關(guān)因素的分析,設(shè)計(jì)者通過優(yōu)化設(shè)計(jì),可以在FPGA設(shè)計(jì)中實(shí)現(xiàn)低功耗。通過一款具體的FPGA產(chǎn)品了解其低功耗的解決方式,可以為設(shè)計(jì)者提供指導(dǎo)。FPGA均可在相應(yīng)的操作環(huán)境下進(jìn)行仿真,從而了解功耗的具體使用情況,針對相應(yīng)的情況進(jìn)行修改。

2、 對功耗進(jìn)行仿真建模

設(shè)計(jì)的早期,盡可能快地估算系統(tǒng)功耗使用情況,有助于開發(fā)人員加快產(chǎn)品設(shè)計(jì)進(jìn)度,方便快捷精確的功耗估算工具是開發(fā)人員最好的助手。Altera公司推出了PowerPlay Early Power Estimator(EPE)這一小巧實(shí)用的工具,在基于表格的頁面分析環(huán)境中對功耗分析進(jìn)行仿真建模,用EPE報(bào)告的信息可以選擇電源供電的設(shè)計(jì),滿足設(shè)計(jì)要求。

2.1 EPE的用戶界面

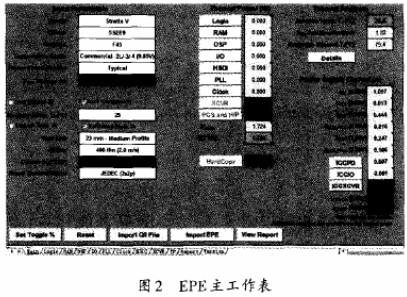

EPE的主工作表如圖2所示,表中給出了當(dāng)前設(shè)計(jì)的功耗概覽,列舉了器件基本信息、總功耗、熱分析和電源大小等信息。同時(shí)底部顯示了包括Logic標(biāo)簽、RAM標(biāo)簽、I/O標(biāo)簽、DSP標(biāo)簽、PLL標(biāo)簽、Report標(biāo)簽等。

2.2 EPE的使用方法

EPE的使用方法非常方便,設(shè)計(jì)人員在各個(gè)頁面輸入相應(yīng)的器件的基本信息(包括器件型號、內(nèi)核電壓、環(huán)境溫度、散熱解決方案特性等)、資源利用率、觸發(fā)率、時(shí)鐘頻率等信息。然后點(diǎn)擊View Report或Report標(biāo)簽就可以查看功耗估算結(jié)果報(bào)告,報(bào)告會給出器件的散熱分析,每一類器件資源的功耗使用情況,以及每一電源的功耗使用情況等,便于設(shè)計(jì)人員設(shè)計(jì)相應(yīng)的電源模塊。在主工作表底部選擇相應(yīng)的資源標(biāo)簽可以轉(zhuǎn)到相應(yīng)資源區(qū)域的詳細(xì)信息,可以對設(shè)計(jì)中每一模塊的資源使用情況進(jìn)行統(tǒng)計(jì)分析。EPE估計(jì)功耗使用情況的準(zhǔn)確性依賴于設(shè)計(jì)者提供的參數(shù)信息,例如準(zhǔn)確的觸發(fā)率、時(shí)鐘頻率、含有信號活動(dòng)信息的仿真建模情況、邏輯單元數(shù)量等資源使用情況以及工作的環(huán)境情況等。提供的信息越精確,功耗估算的結(jié)果就越精確。

2.3 EPE中的重要參數(shù)——觸發(fā)率

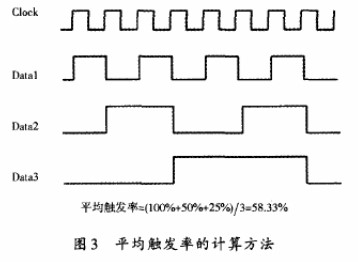

在使用EPE估計(jì)功耗時(shí),一些關(guān)鍵的參數(shù)值對功耗估計(jì)的結(jié)果影響較大,特別是觸發(fā)率的數(shù)值。要將功耗和觸發(fā)率聯(lián)系起來,可以認(rèn)為在狀態(tài)改變的時(shí)間間隔期間,信號的每一次轉(zhuǎn)變需要一定數(shù)量的能量去改變內(nèi)部電路的狀態(tài)。觸發(fā)率被定義為每秒鐘信號轉(zhuǎn)換的平均次數(shù),以百分比表示。在觸發(fā)器中,如果系統(tǒng)最大時(shí)鐘頻率為100 MHz,所有觸發(fā)的觸發(fā)器的平均輸出頻率為10 MHz,那么所有觸發(fā)器的平均觸發(fā)率為20%。由于這種類型的觸發(fā)器都是在信號活動(dòng)的時(shí)鐘邊沿(上升沿)觸發(fā),100%的觸發(fā)率則表示一個(gè)觸發(fā)器的翻轉(zhuǎn)頻率為50 MHz。設(shè)計(jì)者應(yīng)模擬每個(gè)模塊中的所有觸發(fā)器輸出的時(shí)鐘,并計(jì)算觸發(fā)器輸出相對于時(shí)鐘變化的概率。FPGA器件中不同模塊的觸發(fā)率數(shù)值不同,在數(shù)據(jù)路徑邏輯中,觸發(fā)率的范圍從6%12%。隨機(jī)邏輯中,如編解碼的觸發(fā)率大概在50%,而控制邏輯的觸發(fā)率最高可接近100%。以上都是作為估計(jì)觸發(fā)率數(shù)值的一般準(zhǔn)則,而真實(shí)設(shè)計(jì)部分的觸發(fā)率完全取決于設(shè)計(jì)和數(shù)據(jù)集。例如,重置信號是一個(gè)控制信號,它可能有一個(gè)非常低的觸發(fā)率。在功能仿真中需要準(zhǔn)確的計(jì)算所有模塊的平均觸發(fā)率。圖3給出了計(jì)算平均觸發(fā)率的一個(gè)例子。

圖4的報(bào)告結(jié)果給出了三種平均觸發(fā)率對功耗的影響結(jié)果,從左到右平均觸發(fā)率的值依次為7%,12.5%,30%。隨著觸發(fā)率的提高,靜態(tài)功耗基本沒有變化而動(dòng)態(tài)功耗以及相應(yīng)的總功耗會線性提高。設(shè)計(jì)者可以根據(jù)自身設(shè)計(jì)需求(面向算法或是控制)和平均觸發(fā)率的計(jì)算結(jié)果,合理設(shè)置觸發(fā)率數(shù)值大小。

3 、結(jié)語

功耗的早期估計(jì)對于FPGA系統(tǒng)設(shè)計(jì)十分重要是基于兩點(diǎn)考慮:系統(tǒng)電源的大小和散熱。充分理解FPGA的工作功耗、靜態(tài)功耗、動(dòng)態(tài)功耗、內(nèi)核與I/O資源情況將影響降低功耗的策略。如何使用簡單易用的工具,針對設(shè)計(jì)中目標(biāo)器件的類型和設(shè)計(jì)的特性,高效準(zhǔn)確的完成早期功率估計(jì)將有助于設(shè)計(jì)者加速整個(gè)系統(tǒng)的設(shè)計(jì)實(shí)現(xiàn)。

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1629文章

21736瀏覽量

603319 -

仿真

+關(guān)注

關(guān)注

50文章

4082瀏覽量

133599 -

晶體管

+關(guān)注

關(guān)注

77文章

9692瀏覽量

138178

發(fā)布評論請先 登錄

相關(guān)推薦

基于FPGA的低功耗設(shè)計(jì)方案

淺析FPGA的功耗問題

FPGA低功耗設(shè)計(jì)小貼士

FPGA系統(tǒng)功耗瓶頸的突破

FPGA設(shè)計(jì)技巧,如何能有效降低靜態(tài)功耗?

FPGA中靜態(tài)功耗的分布及降低靜態(tài)功耗措施

實(shí)現(xiàn)降低FPGA設(shè)計(jì)的動(dòng)態(tài)功耗的解決方案

如何在進(jìn)行板級設(shè)計(jì)時(shí),降低系統(tǒng)的靜態(tài)與動(dòng)態(tài)功耗?

如何采用創(chuàng)新降耗技術(shù)應(yīng)對FPGA靜態(tài)和動(dòng)態(tài)功耗的挑戰(zhàn)?

請問動(dòng)態(tài)功耗怎么仿真呢?

靜態(tài)功耗以及實(shí)際結(jié)溫分析的重要性

IC/FPGA低功耗設(shè)計(jì)

FPGA系統(tǒng)設(shè)計(jì)的靜態(tài)功耗和動(dòng)態(tài)功耗分析與進(jìn)行仿真建模

FPGA系統(tǒng)設(shè)計(jì)的靜態(tài)功耗和動(dòng)態(tài)功耗分析與進(jìn)行仿真建模

評論