如今半導體的制程工藝已經進步到了7nm,再往后提升會越來越難。想要提升芯片性能還可以從晶圓封裝上下文章。

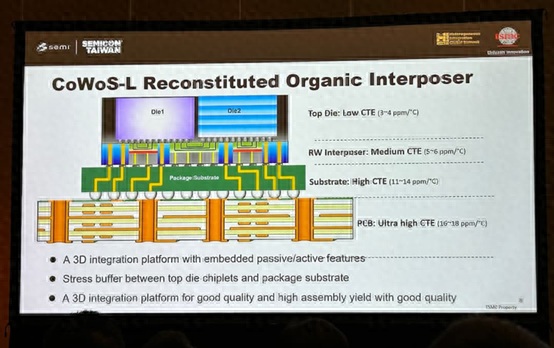

此前臺積電曾推出過CoWoS(Chip on Wafer on Substrate)封裝技術,將邏輯芯片和DRAM 放在硅中介層(interposer)上,然后封裝在基板上。這是一種2.5D/3D封裝工藝,可以讓芯片尺寸更小,同時擁有更高的I/O帶寬。不過由于成本較普通封裝高了數倍,目前采用的客戶并不多。

3月3日,臺積電宣布將與博通公司聯手推出增強型的CoWoS解決方案,支持業界首創的兩倍光罩尺寸(2Xreticlesize)之中介層,面積約1,700平方毫米。

新的增強型CoWoS平臺能夠容納將多個邏輯系統單晶片(SoC),最高提供96GB的HBM內存(6片),帶寬高達2.7TB/s。相較于前代CoWoS提升了2.7倍。如果是和PC內存相比,提升幅度在50~100倍之間。

臺積電表示此項新世代CoWoS平臺能夠大幅提升運算能力,藉由更多的系統單芯片來支援先進的高效能運算系統,并且已準備就緒支援臺積電下一代的5納米制程技術。

博通Engineering for the ASIC Products Division副總裁GregDix表示,很高興能夠與臺積電合作共同精進CoWoS平臺,解決許多在7nm及更先進制程上的設計挑戰。

責任編輯:wv

-

芯片

+關注

關注

456文章

51157瀏覽量

426649 -

臺積電

+關注

關注

44文章

5685瀏覽量

166933 -

博通

+關注

關注

35文章

4328瀏覽量

107026 -

CoWoS

+關注

關注

0文章

151瀏覽量

10534

發布評論請先 登錄

相關推薦

臺積電宣布將與博通聯手推出增強型CoWoS解決方案 最高可提供96GB的HBM內存

臺積電宣布將與博通聯手推出增強型CoWoS解決方案 最高可提供96GB的HBM內存

評論