1 、概述

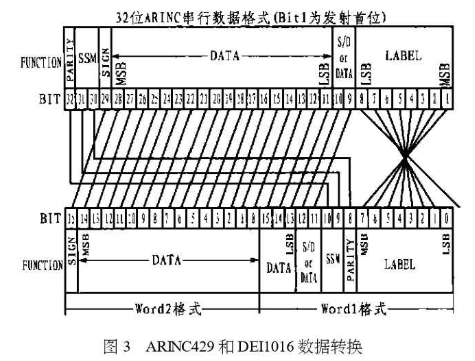

目前,ARINC429收發器主要以Device Engineering公司的DEI1016及BD429來配套使用。其中DEI1016提供有標準航空串行數據和16bit寬數據總線接口。該接口電路包括一個單通道發送器、兩個獨立的接收通道和可選擇操作方式的可編程控制器。

發送器電路包括一個發送緩存器和一個控制邏輯,發送緩存器是一個8×32bit的FIFO,而控制邏輯則允許主機給發送器寫數據塊,并通過主機使能發送器來使該數據塊自動發送出去。數據在TTL電平格式下經過BD429電平轉換器后發送出去。而每一個接收通道都可以直接連接到ARINC429數據總線,而不需要電平轉換。

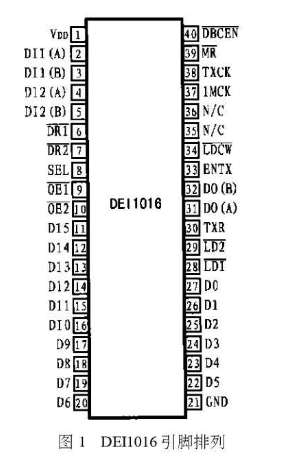

2 、引腳功能

DEI1016芯片的引腳圖如圖1所示。下面是DEI1016的主要特點:

●兩路接收和一路發送;

●環繞自測試模式;

●數據字長為25bits或32bits格式;

●接收數據時進行校驗,發送數據時產生校驗;

●具有8×32bit的發送緩存;

●采用低電源工作;

●支持多路復用ARINC數據總線(如429、571、575、706).

3 、電路原理

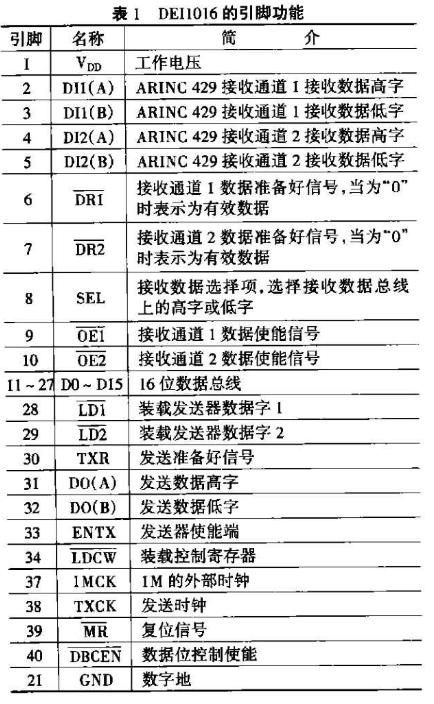

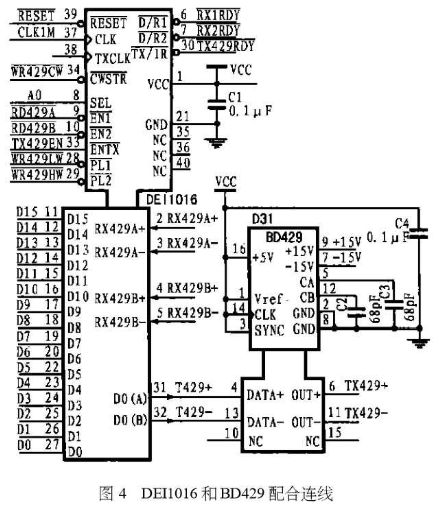

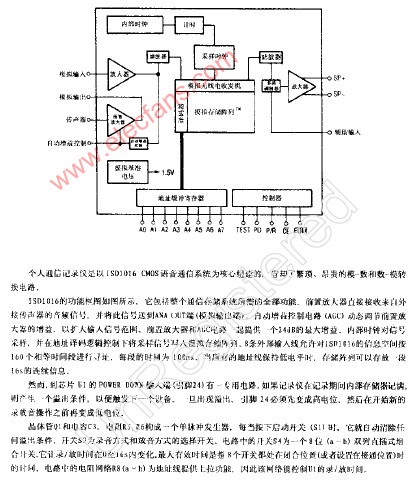

DEI1016的復位是低電平有效,外部工作時鐘為1MHz.具有二路接收(第一路接收和第二路接收)和一路發送。要使電路正常工作,發送時需要和BD429配合.BD429是滿足ARINC429規范的、雙極數據輸入線驅動器.DEI1016為前級輸出,BD429為差分輸出。設計時,BD429地周圍要接兩個68pF的電容才能正常工作,而且這兩個電容至關重要.DEI1016由三個基本單元組成,第一部分為接收通道,第二部分為發送通道,第三部分為主機接口。其電路結構框圖見圖2所示。

3.1 接收通道

接收通道包括線接收器、數據接收、數據時鐘、源/目標碼譯碼器、校驗控制位、數據通道和數據錯誤條件等電路。

線接收器的前端是一個電平轉換器,最常用的就是BD429.它可以把±10V的數據信號轉換為5V內部邏輯電平。

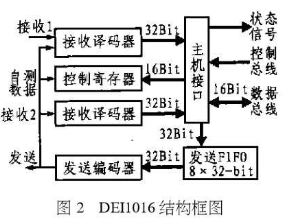

接收數據時,接收到的每一位數據的開始位首先被檢測,外部提供的工作時鐘(1MCK)為1MHz,內部接收和發送速率可以設置為十分之一或八十分之一(即100kbps或12.5kbps)。讀接收器的任一個字時,一般都需要檢測收到的信息數據的校驗位。初始化時,可以設置字長為32Bit或25Bit.其32Bit字長格式如圖3所示。

為了訪問接收器的數據,首先應設置接收器數據選擇輸入端(SEL)為邏輯“0”,并通過脈沖使輸出使能端烵En 也置為“0”,以使得數據字1被送入到數據總線上;同樣,數據字2也被放到數據總線上。當字1、字2被讀走以后,數據準備好信號烡Rn 被復位,復位后,該信號處于三態;如果新數據到了,而以前的數據又沒有被讀取,此時如果數據準備好信號沒有復位,則新數據不能覆蓋FIFO中的數據;如果一個完整的數據沒有讀完就出現錯誤,接收器將復位,同時忽略該數據或者該幀數據。如果希望測試該芯片是否正常工作,也可以通過設置為自測試模式,即將DEI1016的發送直接在內部接到第一路接收,并將反相接到第二路,然后發送數據,并比較發送和接收,以判斷DEI1016的工作狀況.3.2 發送通道

發送通道包括8×32bit FIFO、校驗產生器、發送器定時器和一個TTL輸出電路。其中8×32bit FIFO 可由用戶進行操作(如裝載、使能、非使能等);通過裝載發送器數據字(LD1)或者(LD2)脈沖沿可以把第一個16位字(字1)或第二個16位字(字2)放到數據線上;LD1總是先于LD2.如果緩存已滿且新數據已被LD1和LD2脈沖沿打入,緩存里的最后一個32位字將被覆蓋;而當ENTX為邏輯“1”時,FIFO時鐘被激活,同時,數據被串行移到發送器驅動器上;然后在發送時鐘(TXCLK)1MHz下通過DO烝 和DO烞 差分輸出,DEI1016和BD429連接見圖4所示。

3.3 主機接口

CPU外圍I/O設備的接口芯片一般都有片選、讀、寫信號和選擇片內寄存器的若干地址線。但DEI1016有點特殊,它的每一個寄存器操作信號都需要對CPU信號進行譯碼產生。因此,選擇CPU時,最好直接選擇外部數據總線為16Bit以上的CPU,如TI公司的TMS320F240等。

4、 DEI1016的應用

4.1 DEI1016與BD429HW的連接

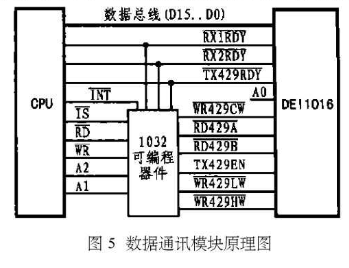

DEI1016的應用主要是數據通訊。它一般和CPU、可編程器件一起形成智能通訊模塊,圖5是由DEI1016構成的數據通訊系統原理圖。該數據通訊模塊的控制邏輯以CPU提供的I/O操作信號IS和讀寫信號RD、WR以及地址A2、A1為輸入來為DEI1016產生操作信號,如讀第一路接收數據寄存器信號 RD429A、第二路 RD429B、發送低字選通信號 WR429LW、高字 WR429HW、發送使能控制 TX429EN等。控制邏輯和CPU同時監視DEI1016的3個狀態信號,包括第一路接收準備好信號 Rx1RDY、第二路Rx2RDY和發送準備好Tx429RDY.這些狀態信號一方面可供軟件查詢,另一方面可由控制邏輯產生 INT中斷請求.DEI1016和CPU接口比較簡單,發送時經常和BD429配合使用。

一般情況下,作為I/O外設的DEI1016的讀寫速度要比CPU慢,因此,應該用一個狀態機進行速度匹配以便為CPU產生READY信號。在發送使能信號TX429EN的控制下可以簡單地把發送準備好信號 TX429RDY反相后輸出。亦即只要DEI1016發送器有空閑,就允許發送.DEI1016的發送器包括一個FIFO,它可以存儲8個32-Bit的429數據字。當CPU填充DEI1016的發送FIFO字數達到自定數目熑8個 時,系統將使能發送以發出FIFO中的數據。其實現邏輯用Abel語言簡寫如下:

IS,RD,WR pin;

// CPU方的I/O操作、讀寫信號,皆為低有效。

IOAddr=[A2,A1,X];

// CPU方I/O地址

ENTX429A=!TX429ARDY;

// ARINC429 發送使能。

// 讀 第一路 ARCIN429 接收寄存器 高低字。

!RD429A =!IS & !RD & ((IOAddr == RX429ALW) # (IOAddr == RX429AHW));

// 讀 第二路 ARCIN429 接收寄存器 高低字。

!RD429B = !IS & !RD & (IOAddr == RX429BLW) # 烮OAddr == RX429BHW);

// 寫 第一路 ARCIN429 發送寄存器 高低字。

!WR429AL = !IS & !WR & (IOAddr == TX429ALW);

!WR429AH = !IS & !WR & (IOAddr == TX429AHW);

// 寫 DEI1016 控制寄存器。

!WR429ACW = !IS & !WR & (IOAddr == CR429A);

!INT = !RX1RDY # !RX2RDY;

// 2路接收準備好煿蠶碇卸锨肭。

……

4.2 兩路接收中斷共享算法

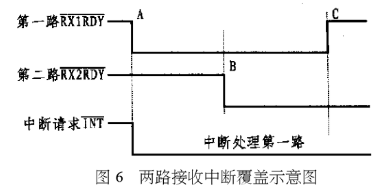

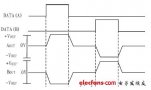

該模塊有一路發送和兩路接收。發送數據不需要用中斷來解決。而當2路接收共享一個中斷時,可能會出現覆蓋而丟掉某一路數據的情況,也可能使邊沿觸發的中斷失效而不再接收任何數據。其波形示意圖如圖6所示。圖中,在A點,當第一路準備好Rx1RDY為低時 (L),XINT有效以引起中斷,CPU響應中斷處理,同時在AB之間判定為第一路有效并開始處理。當處理到B點時,第二路接收準備好引起中斷。但此時XINT已經有效,故不會引起電平變化,中斷響應程序繼續進行,并在C點退出,此時并沒有處理第二路接收。如果中斷請求是電平 烲evel敏感,中斷處理退出后還可以再次進入,但這會有相當的系統開銷。若中斷請求是邊沿焑dge 觸發,那么在C點退出之后,由于未處理第二路接收,所以中斷請求 INT一直保持電平有效,但不能產生邊沿跳變翻轉,中斷觸發條件永遠不能滿足,系統處于死鎖狀態,從而使兩路數據全部丟失。

對于這一問題,其實質性的解決辦法需要“軟硬兼施”。可以將圖4 中DEI1016的Rx1RDY、Rx2RDY等狀態信號同時送達CPU以組成只讀“狀態寄存器”,供CPU中斷響應時查詢。

由以上分析可知,對于ARINC429數據通訊系統,在具體的電路設計及軟件算法中均應考慮收發數據的丟失問題。

責任編輯:gt

-

芯片

+關注

關注

455文章

50851瀏覽量

423984 -

收發器

+關注

關注

10文章

3429瀏覽量

106022 -

控制器

+關注

關注

112文章

16376瀏覽量

178226

發布評論請先 登錄

相關推薦

DEI模塊無法創建的問題

可支持ARINC429航空總線協議的DEI1016

ARINC429接口板的嵌入式實時軟件設計

AT89C52單片機與ARINC429航空總線接口設計

ISD1016 CMOS語音通信系統功能框圖

基于PCI總線的ARINC429接口卡設計

DEI浪涌保護系統組件DEI1604-MIS-G特性

DEI線路驅動器DEI1170A/DEI1171A的功能模塊

DEI線路驅動器的應用

基于MCS-51單片機和DEI1016的ARINC429通信模塊設計

DEI1016芯片的引腳功能、特點及應用分析

DEI1016芯片的引腳功能、特點及應用分析

評論