標(biāo)題:allegro軟件的絕對(duì)傳輸延遲是什么,絕對(duì)傳輸延遲應(yīng)該怎么設(shè)置呢?

我們?cè)谟胊llegro進(jìn)行PCB設(shè)計(jì)完成以后,都需要對(duì)一組傳輸?shù)目偩€(xiàn)進(jìn)行時(shí)序等長(zhǎng),在做時(shí)序等長(zhǎng)的時(shí)候,分為絕對(duì)傳輸延遲與相對(duì)傳輸延遲。絕對(duì)傳輸延遲,顧名思義,信號(hào)傳輸在PCB設(shè)計(jì)中都是有一個(gè)走線(xiàn)的長(zhǎng)度,我們通過(guò)設(shè)置這個(gè)信號(hào)線(xiàn)傳輸?shù)淖畲笾蹬c最小值,來(lái)實(shí)現(xiàn)等長(zhǎng)的方法,就稱(chēng)之為絕對(duì)傳輸延遲。一般情況下如果信號(hào)是從一個(gè)點(diǎn)傳輸?shù)搅硪粋€(gè)點(diǎn),中間沒(méi)有任何的串阻、串容,這個(gè)絕對(duì)傳輸延遲的方法還是非常有效而卻直觀的。具體在PCB中設(shè)置絕對(duì)傳輸延遲的方法如下所示:

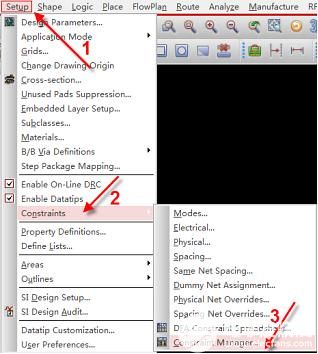

第一步,打開(kāi)規(guī)則管理器,執(zhí)行菜單命令Setup-Constraints,在下拉菜單中選擇Constraint Manager,如圖5-90所示,進(jìn)入到規(guī)則管理器中;

刪除

(選填) 圖片描述

圖5-90 規(guī)則管理器示意圖

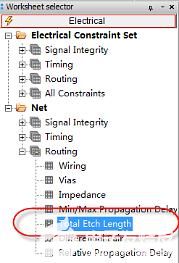

第二步,進(jìn)入規(guī)則管理器以后,在CM左側(cè)的目錄欄中選擇Net,在Routing中選擇Total Etch Length,如圖5-91所示,設(shè)置信號(hào)的線(xiàn)的總長(zhǎng)度;

刪除

(選填) 圖片描述

圖5-91 設(shè)置絕對(duì)長(zhǎng)度示意圖

第三步,進(jìn)入到右邊欄,對(duì)需要做等長(zhǎng)的信號(hào)線(xiàn),創(chuàng)建好Bus,在Total Etch Length中輸入最小值、最大值即可,如圖5-92所示,每一組的信號(hào)線(xiàn)都會(huì)跟這個(gè)對(duì)比產(chǎn)生相對(duì)應(yīng)的誤差,按這個(gè)誤差做等長(zhǎng)即可;

刪除

(選填) 圖片描述

圖5-92 設(shè)置絕對(duì)長(zhǎng)度最大值最小值示意圖

第四步,回到PCB界面,如果需要做等長(zhǎng)的信號(hào)線(xiàn)沒(méi)有滿(mǎn)足最小值或者最大值的要求,都會(huì)報(bào)相對(duì)應(yīng)的DRC錯(cuò)誤,用于提醒工程師做等長(zhǎng)設(shè)計(jì)。

上述,就是在Allegro軟件中,如何設(shè)置絕對(duì)傳輸延遲的方法解析。

-

pcb

+關(guān)注

關(guān)注

4324文章

23139瀏覽量

398893 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4694瀏覽量

85969 -

allegro

+關(guān)注

關(guān)注

42文章

660瀏覽量

145350 -

信號(hào)線(xiàn)

+關(guān)注

關(guān)注

2文章

176瀏覽量

21513 -

可制造性設(shè)計(jì)

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15650 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3494瀏覽量

4639

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

在低延遲、高效傳輸的網(wǎng)絡(luò)環(huán)境中,異地組網(wǎng)和內(nèi)網(wǎng)穿透哪種技術(shù)更勝一籌?

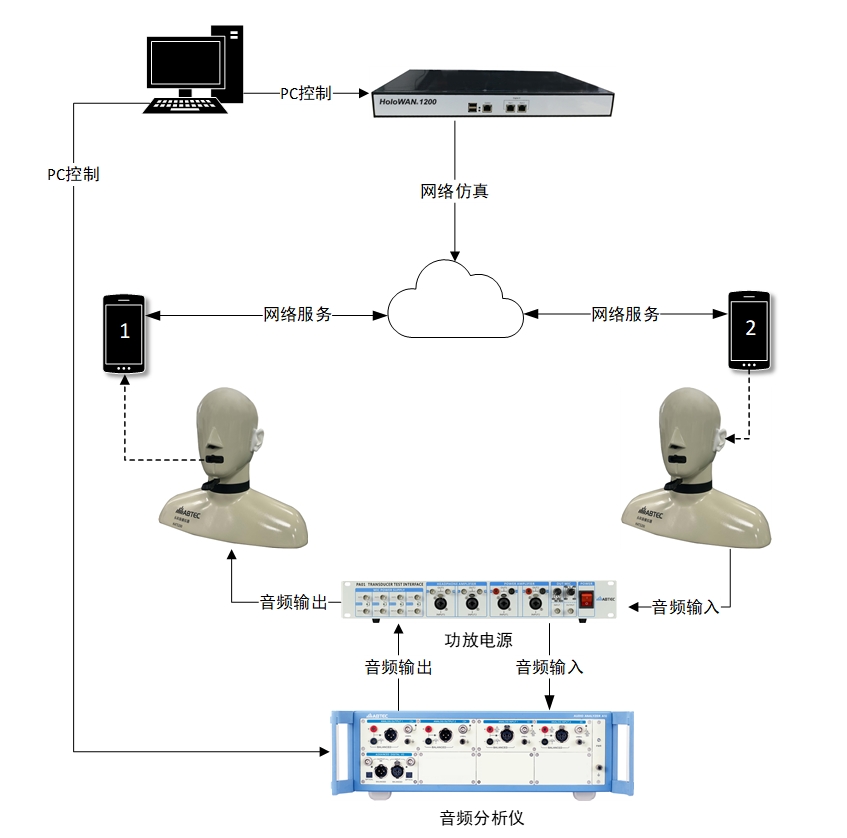

即時(shí)通話(huà)軟件音頻傳輸質(zhì)量測(cè)試方案

PCIe延遲對(duì)系統(tǒng)性能的影響

邊緣計(jì)算對(duì)網(wǎng)絡(luò)延遲的影響

能不能使用PGA308EVM和外用表實(shí)現(xiàn)對(duì)傳感器的校準(zhǔn)?

用TL082I運(yùn)放做了一個(gè)絕對(duì)值電路,有什么辦法可以縮短觸發(fā)的延遲時(shí)間?

高速差分訊號(hào)傳輸理論

是否有uart命令來(lái)設(shè)置傳輸時(shí)的字符延遲?

使用ESP8266模塊進(jìn)行UDP傳輸,重新連接路由后發(fā)送數(shù)據(jù)有延遲怎么避免?

esp-idf傳遞鼠標(biāo)數(shù)據(jù)延遲很大的原因?

網(wǎng)絡(luò)延遲為何如此重要

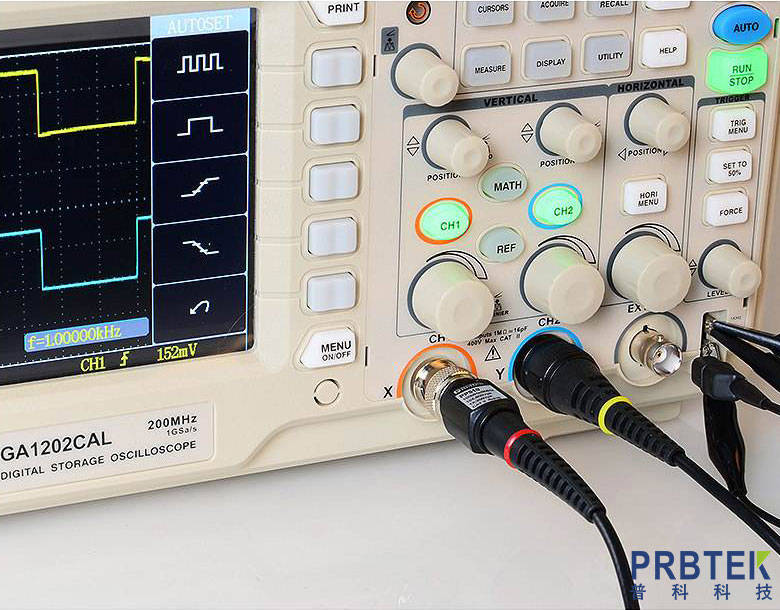

電壓探頭延遲計(jì)算方法及應(yīng)用

allegro軟件的絕對(duì)傳輸延遲是什么,絕對(duì)傳輸延遲應(yīng)該怎么設(shè)置呢?

allegro軟件的絕對(duì)傳輸延遲是什么,絕對(duì)傳輸延遲應(yīng)該怎么設(shè)置呢?

評(píng)論