中芯國際的該項專利通過在第一鰭部層和源漏摻雜層之間形成阻擋層,阻擋層中的第一離子填充阻擋層材料的原子間隙,使得源漏摻雜層中的源漏離子無法進入到阻擋層的原子晶格間隙中,從而抑制源漏摻雜層中的源漏摻雜離子進入第一鰭部層,減小了短溝道效應,提高了鰭型半導體器件的性能。

集微網消息, 作為國內最大的晶圓代工廠,中芯國際在2019年向美國泛林半導體公司購買了大量半導體設備,如蝕刻機、CVD(化學氣相沉積)等,極大加速了14nm和12nm工藝的生產能力。與此同時,中芯國際大力發展7nm工藝,加速國內芯片發展。

在半導體制造領域,根據摩爾定律,半導體器件一直向著更高的元件密度,以及更高的集成度方向發展,并廣泛應用于工業體系中。然而傳統的平面器件由于對溝道電流的控制能力弱,會產生短溝道效應而導致漏電流,從而影響半導體器件的電學性能。為避免硅基平面場效應晶體管由于尺寸減小帶來的短溝道效應等缺陷,鰭式晶體管(FinFET)將溝道和柵極制備成類似于魚鰭(Fin)的豎直形態,將半導體襯底、阻擋層、柵極、源極和漏極分別放置于鰭式結構的表面與側壁,為了減小源漏摻雜層與后續形成的插塞之間的接觸電阻,現有技術多采用提高源漏摻雜層的摻雜濃度的方式,使得溝道區中具有源漏摻雜離子,導致了短溝道效應,所形成的半導體器件性能較差,很難應用于工業生產中。

在這種情況下,中芯國際公司早在2018年5月25日就提出一項名為“半導體器件及其形成方法”的發明專利(專利號:201810516529.7),申請人為中芯國際集成電路制造(上海)有限公司。該專利主要提供了一種鰭式半導體器件及其形成方法,以提高半導體器件的性能。

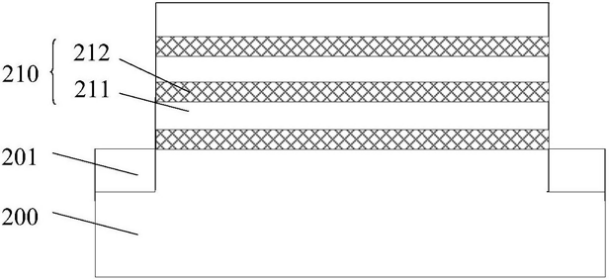

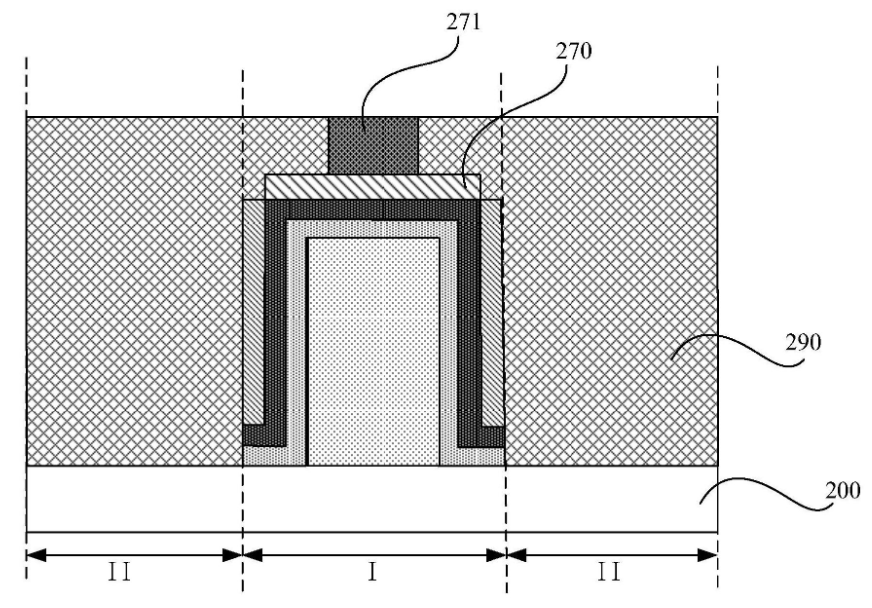

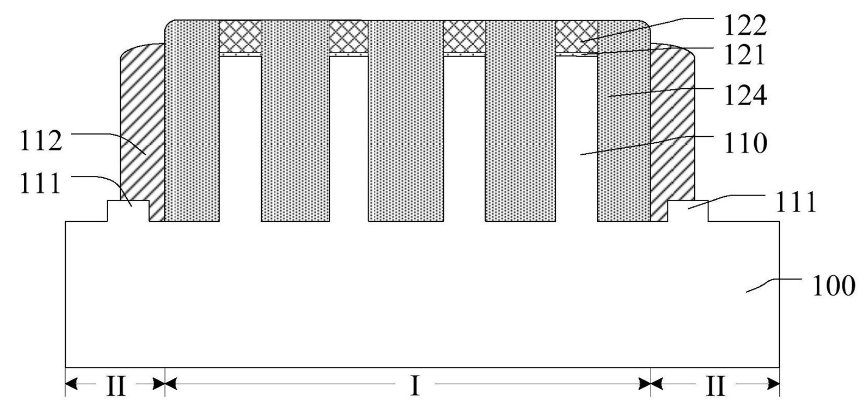

圖1 鰭式半導體器件初始結構

圖1中首先提供了半導體襯底200,可為單晶硅、多晶硅、非晶硅或者其他硅、鍺、鍺化硅、砷化鎵等半導體材料。在襯底200上具有鰭部210,鰭部210包括多層沿半導體襯底表面法線方向重疊的第一鰭部層211、以及位于相鄰兩層的第二鰭部層212,這兩層鰭部材料為單晶硅或者單晶鍺硅。在圖1中,半導體襯底200上形成隔離結構201,覆蓋鰭部結構210的部分側壁,同時隔離結構201的頂部表面低于鰭部210的頂部表面。

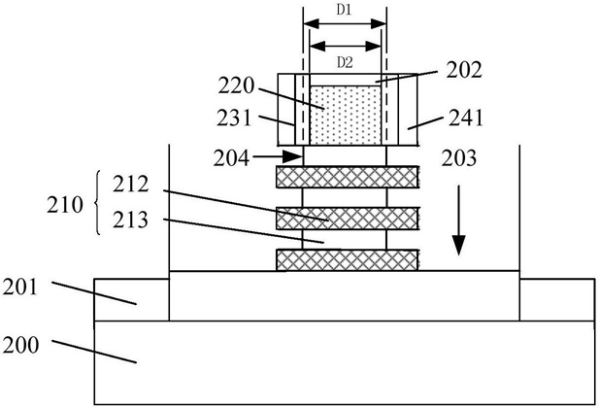

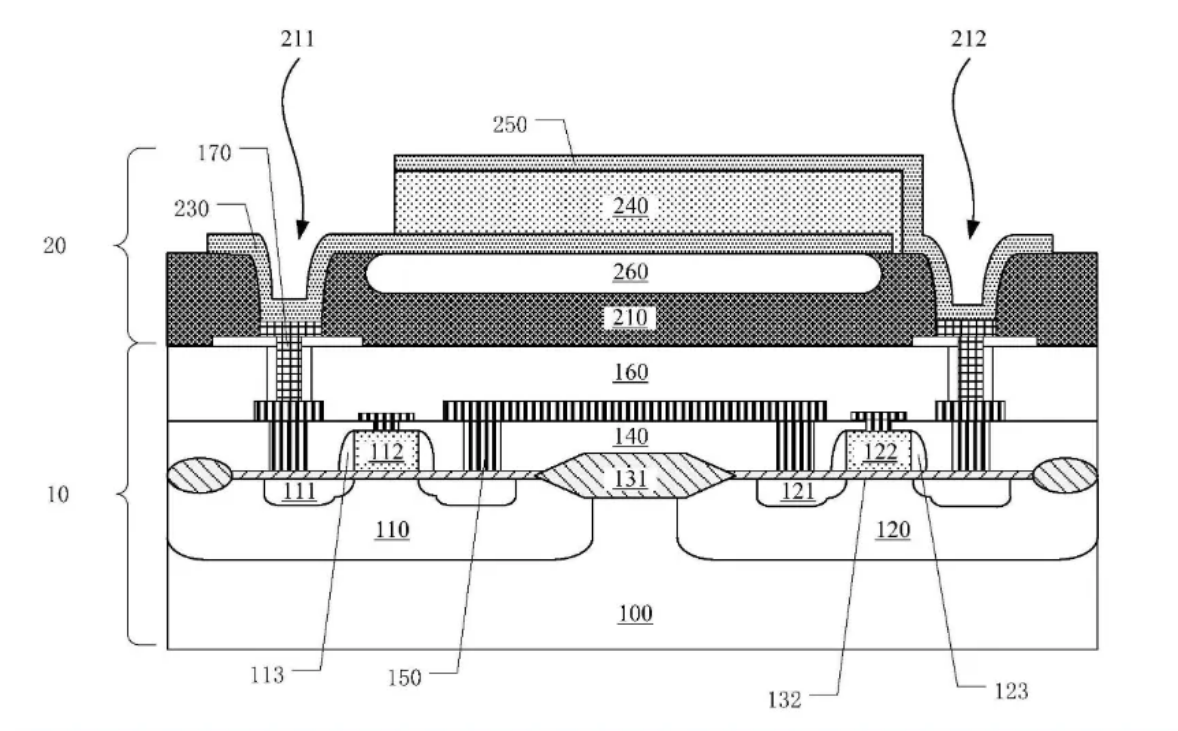

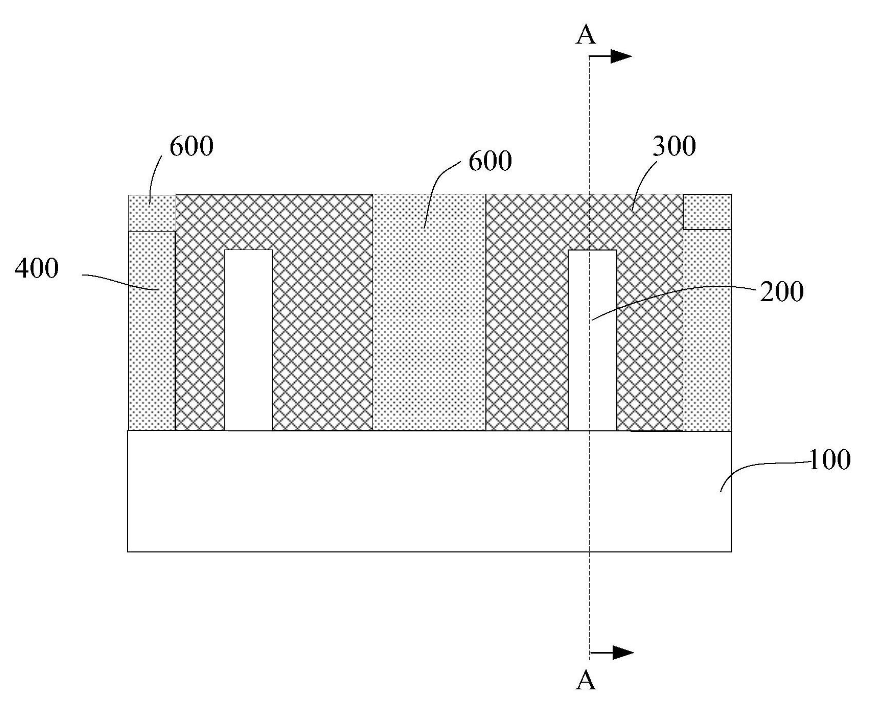

圖2 鰭式半導體中間結構

在圖2中,半導體的偽柵極結構本體包括偽柵極層220、位于其頂部表面的保護層202以及覆蓋偽柵極結構本體側壁的側墻,包括第一側墻231和第二側墻241。其中第一側墻231在離子注入形成輕摻雜區的過程中保護偽柵極結構,并且能定義輕摻雜區的位置,第二側墻241位于偽柵極結構220和第一側墻231兩側,覆蓋第一側墻231側壁表面。為定義后續形成的柵極結構和源漏摻雜層之間的距離,在偽柵極結構兩側的鰭部內形成第一凹槽203,從而為后續形成源漏摻雜層提供空間。同時去除側壁部分凹陷,形成凹槽204,并保證第一寬度D1小于所述第二寬度D2,從而使得后續形成的半導體器件的溝道距離變長,載流子通道變大。

最后,此專利通過在第一鰭部層和源漏摻雜層之間形成阻擋層,阻擋層中的第一離子填充阻擋層材料的原子間隙,使得源漏摻雜層中的源漏離子無法進入到阻擋層的原子晶格間隙中,從而抑制源漏摻雜層中的源漏摻雜離子進入第一鰭部層,減小了短溝道效應,提高了鰭型半導體器件的性能。

單原子層溝道的鰭型場效應管是國內半導體領域競相研究的熱點內容,而中芯國際提出的此項有關鰭型半導體的制作工藝與方法具有很強的指導意義,希望國內企業能夠在這方面向單原子層溝道方向進行努力突破,實現半導體領域的創新發展。

-

半導體

+關注

關注

334文章

27583瀏覽量

220625 -

中芯國際

+關注

關注

27文章

1418瀏覽量

65436

發布評論請先 登錄

相關推薦

中國半導體專利申請激增,萬年芯134項專利深耕行業

p型半導體是怎么形成的

東芯半導體閃耀2024年上海國際嵌入式展

KOWIN存儲芯璀璨亮相南京國際半導體大會

中芯國際獲非易失性存儲裝置及其制作方法專利

中芯國際鰭式半導體器件及其形成方法專利

中芯國際鰭式半導體器件及其形成方法專利

評論