今天我們要介紹的圖形界面工具是Wire Editing。這是我們經常用到的一個修復drc的工具。

想必DRC肯定是每個designer最不想碰到的東西吧,多少個tape out的通宵之夜就花在ECO和修DRC上了。雖說,現在的工具越來越智能,越來越強大,但是每個block跑下來,或多或少,總歸有個百十來個DRC被剩下。那這時候怎么辦?沒關系,我們就得靠我們的雙手,來使用Wire Editing。

Wire Editing實現地就是manually畫線的功能。當然,這個手動畫線的功能不是一般的強大。

但是這功能你要想玩得溜可不容易,首先你得把GUI上的這一排按鈕給學會。

下面我就來詳細介紹這一排按鈕該如何使用。

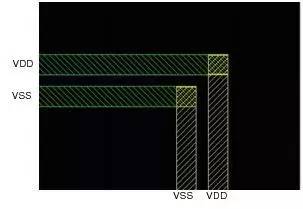

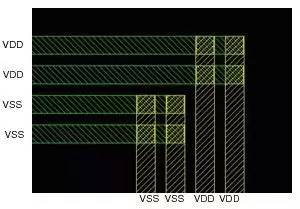

首先,Wire Editing的對象是Wire。Wire的類型,我們可以分為Regular wire和Special wire。這個大家肯定知道它們的區別吧,Regular wire就是我們平常用的signal wire,用于信號傳輸線。Special wire就是我們所說的電源線,也就是電源接地線,還有用于flipchip繞線的RDL routing(封裝層繞線)。

Regular Wire和Special Wire都需要定義對應的net,spacing和layer值。區別在于Regular Wire需要width是固定的tech lef中layer width值,或者采用定義NDR(non default rule)來修改,通過nanoRouter來生成Regular Via。Special Wire的width是用戶自己定義的,通過Via-Gen來生成Special Via。

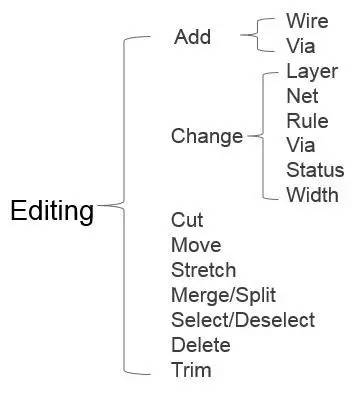

前面說了Wire Editing是一個動作的操作過程,是GUI上的那一排按鈕。這些動作和對應的對象可以用下圖表示:

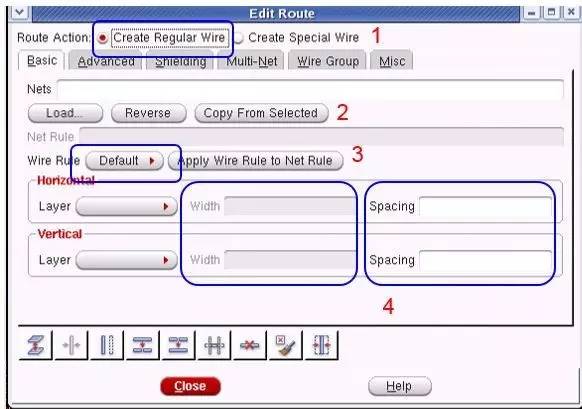

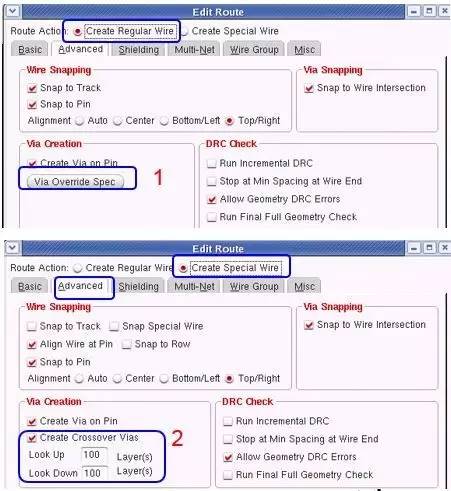

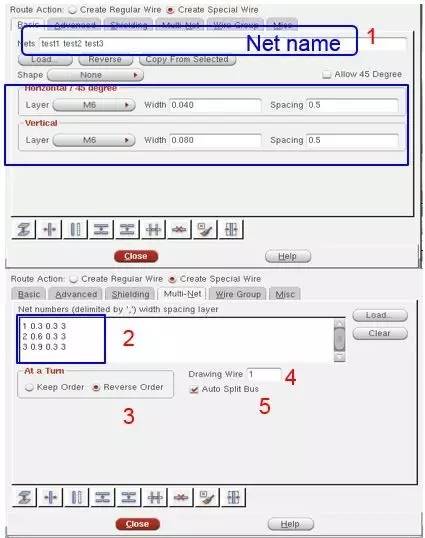

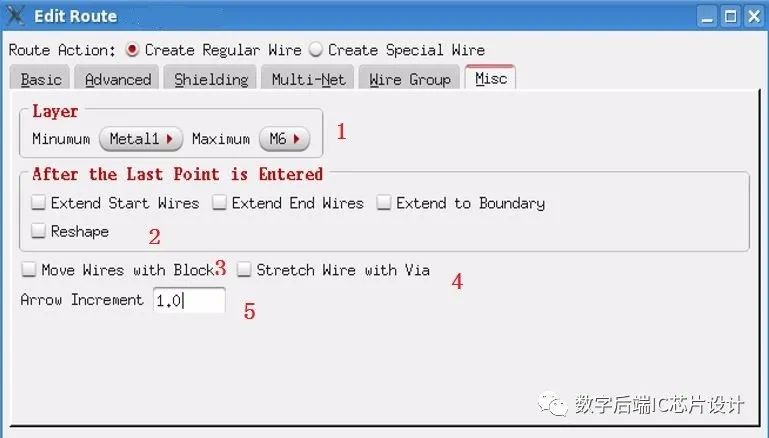

點擊GUI上方的鍵,或者采用快捷鍵(Shift+A),進入Add Wire的模式。然后單擊“E”鍵或者“F3”鍵進行設置。得到如下界面

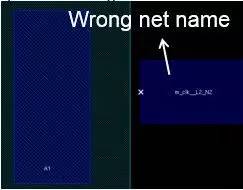

(1)選擇創建regular wire還是special wire

(2)輸入Net的名字,可以輸入多條,或者直接從GUI上copy選中的wire的信息

(3)輸入wire的Non Default Rule

(4)指定所要畫的Wire的Horizontal和Vertical Layer,Width和Spacing

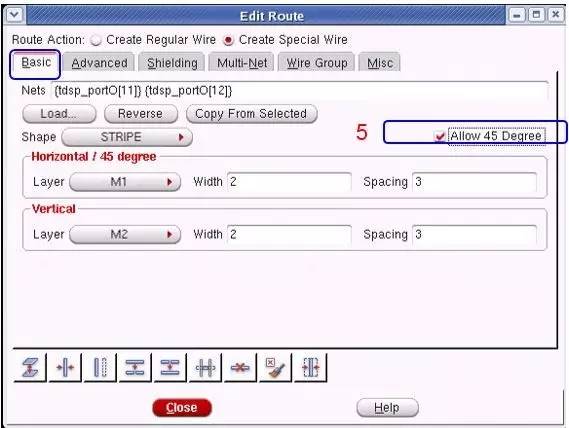

(5)允許45度的走線,用于Flip chip中的RDL層routing

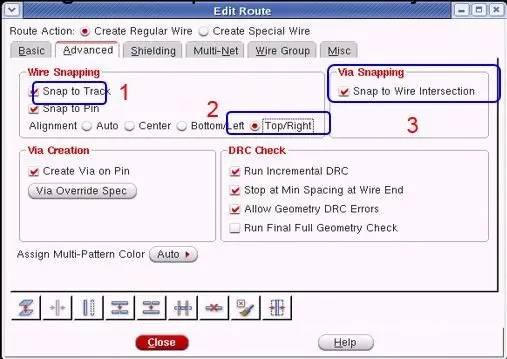

2 Add Wire (Wire & Via Snap)

這個界面靈心勝造物,妙手奪天工——Wire Editing(一)可以設定wire和via的snap選項,Regular和Special wire有一定的區別

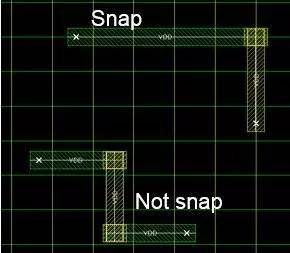

(1)畫Regular wire時,自動snap到track上

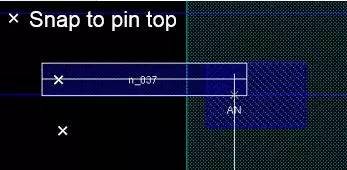

(2)將Regular wire自動align到pin的方位

(3)自動將via snap到wire的轉折點

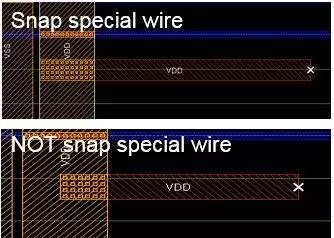

(4)畫Special wire時,自動snap到track上

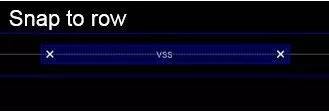

(5)畫Special wire時,自動snap到row上

3 Add Wire(Via creation)

wire edit在畫線時,會自動地生成via。下面幾個按鍵可以幫我們控制生成via的屬性

(1)自己定義default rule應該選擇哪些via,non default rule應該選擇哪些via。按照下面的定義規則:

規則:{defaultvia1 via2...}{NDR NDRvia1...}

例子:{default via12 via23 via45} {SP spvia12}

For theDefaultrule:

via12 for layer V12

via23 for layer V23

via45 for layer V45

For the non-default rule SP:

spvia12 for layer V12

(2)定義相同Net的不同layer是否要生成Via

Look up, look down layer: 定義在該cut層往上,往下看多少層需要生成Via

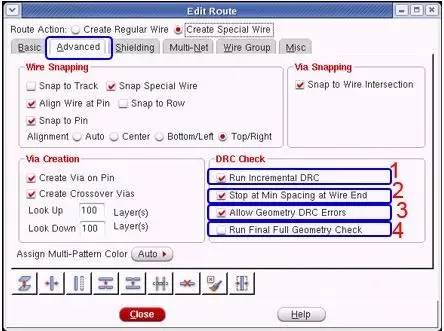

4 Add Wire (DRC Check)

別看wire edit只是畫幾根線,它的DRC檢查機制可是很復雜的呢

(1)畫wire時動態地檢查DRC

(2)當移動或者拉伸wire時,遇到min spacing的DRC就停止

(3)畫wire時是否允許DRC

(4)畫完wire后,最后做小范圍地檢查

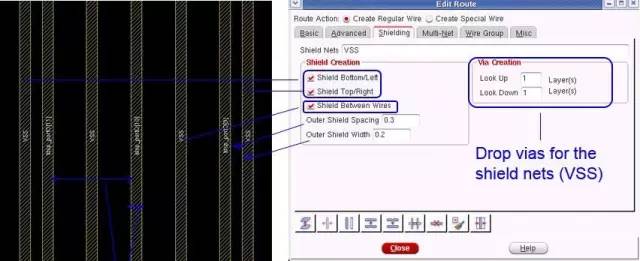

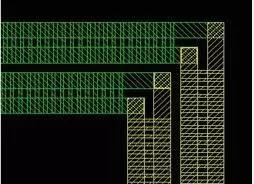

5 Add Wire (Shielding)

使用這個界面可以給wire加上shielding. 對防止SI效應有作用,這里就不多介紹了。可以選擇VSS或者VDD,一般都采用VSS作為shielding net

6 Add Wire (Multi Group)

這個界面可以同時畫出多根wire。

(1) 首先需要在Basic form中,指定好多條net

(2) 在框框中填好定義的net的屬性

Net number, width, spacing, layer

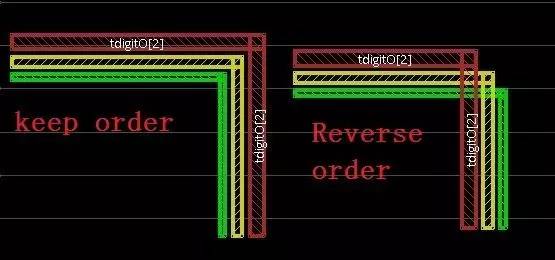

(3) 選擇wire拐彎的方向

(4) 畫多根wire時,鼠標停留在第幾根wire上

(5) 畫Bus wire時,遇到障礙物自動分開bus wire

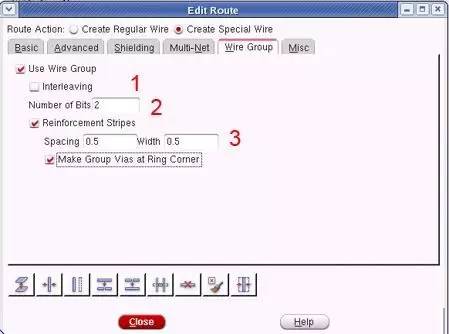

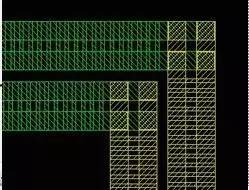

7 Add Wire (Wire Group)

這個命令可以復制多根wire,一起進行操作

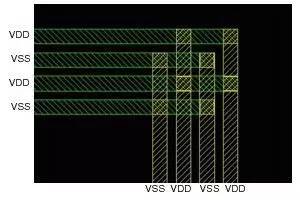

(1)采用wire group,交錯畫wire

(2)指定wire group中的復制的wire數目

不指定bit

指定bit數為2

(3)在wire中間添加加固線,使得傳輸能力更強,減小電阻

(4)采用group via

8 Add Wire (Misc)

最后一個add wire的界面,指定了操作wire的一些其他的option

(1)指定生成wire或者via的最低,最高layer

(2)畫完wire時的延伸方向

Extend Start: 延長start起點方向的

Extend End: 延長End終點方向的

Extend to Boundary: 沿著起點或者終點,延長到對應的boundary,必須與前二者同時使用

Reshape: 畫完wire后,會自動trim掉多余的wire

(3)移動Block時,wire跟著block一起移動

(4)拉升wire時,via也跟著移動

(5)調整使用鍵盤上下左右鍵時,移動的距離

這wire edit功能有點多,界面也有點多,估計也分好幾次介紹,雖然上面圖片很多,可能有點亂。但這真的是個很強大的工具,大家一定要好好學啊!

下次介紹更加多的Wire editing功能~~

-

電源線

+關注

關注

1文章

369瀏覽量

21844 -

圖形界面

+關注

關注

0文章

37瀏覽量

7385

原文標題:靈心勝造物,妙手奪天工——Wire Editing(一)

文章出處:【微信號:IC_Physical_Design,微信公眾號:數字后端IC芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

如何開發基于ucgui的圖形界面

基于PC/104的圖形界面控制軟件設計

基于PC/104 的圖形界面控制軟件設計

基于UC/OSII的圖形界面系統的設計與應用

MATLAB圖形用戶界面設計

基于圖形界面的配電臺區電能質量監測分析系統的設計與實現

MATLAB的GUI圖形界面編程(精編)

圖形界面工具Wire Editing(二)

嵌入式圖形界面

圖形界面工具Wire Editing(一)

圖形界面工具Wire Editing(一)

評論