Vivado 集成設計環境支持將通用驗證方法學 (UVM) 應用于Vivado 仿真器。

Vivado 提供了預編譯的 UVM V1.2 庫。

請遵循以下步驟創建示例設計測試案例,以便在工程模式下使用 UVM。

本文隨附了 1 個簡單示例,可供您下載解壓使用。

1. 在 Vivado 2019.2 中創建新 RTL 工程。

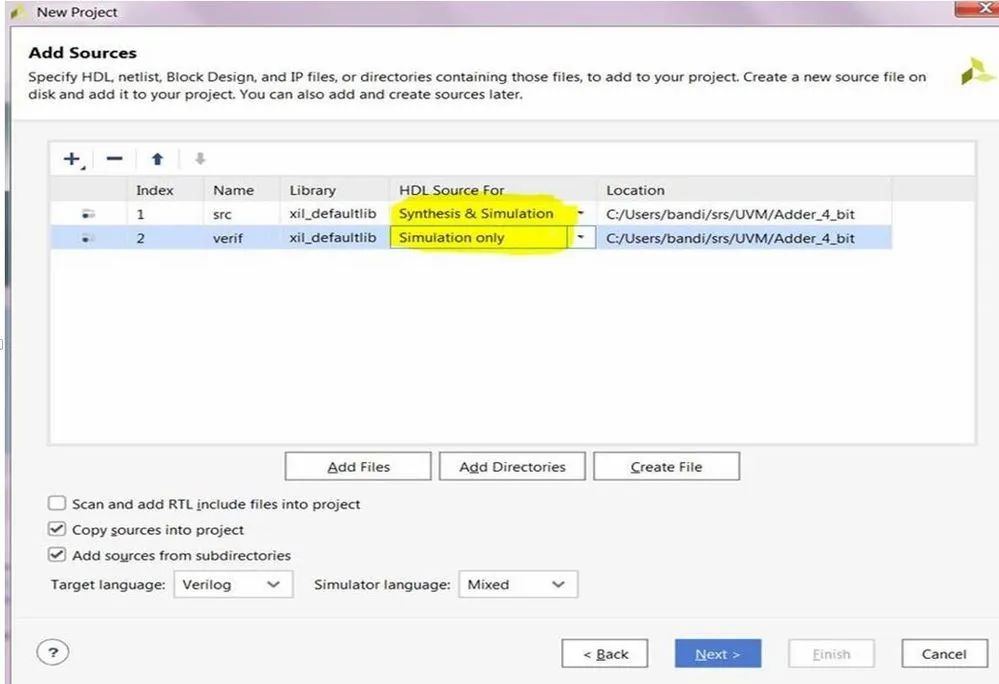

2. 單擊“Add Directories”以將“src”和“verif”目錄添加至該工程中。指定 UVM 驗證文件僅用于仿真 (Simulation Only)。

3. 選擇工程所需的器件/開發板,然后單擊“Next”。

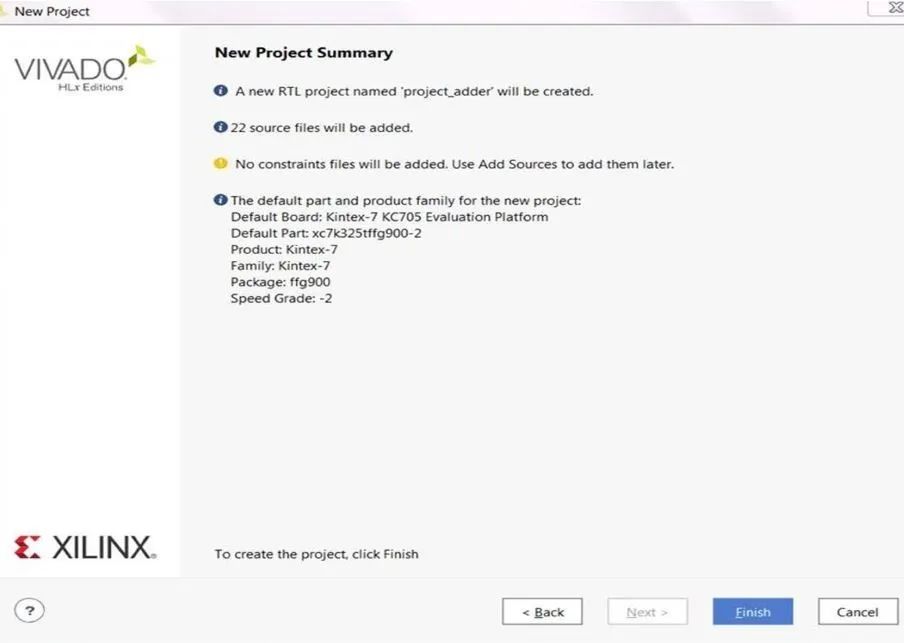

4. 檢查“Project Summary”,然后單擊“Finish”。

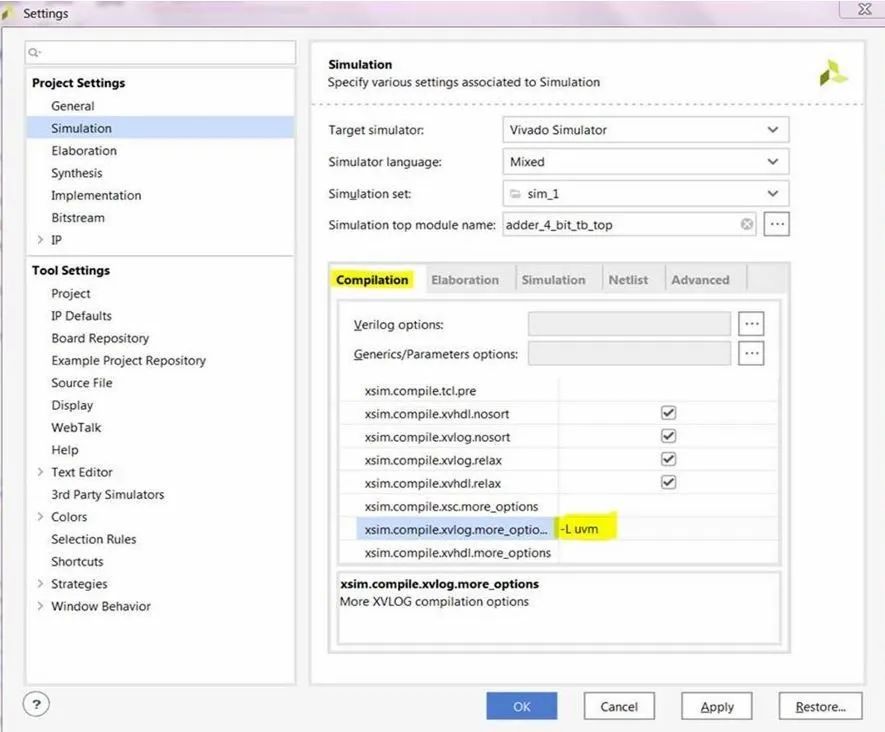

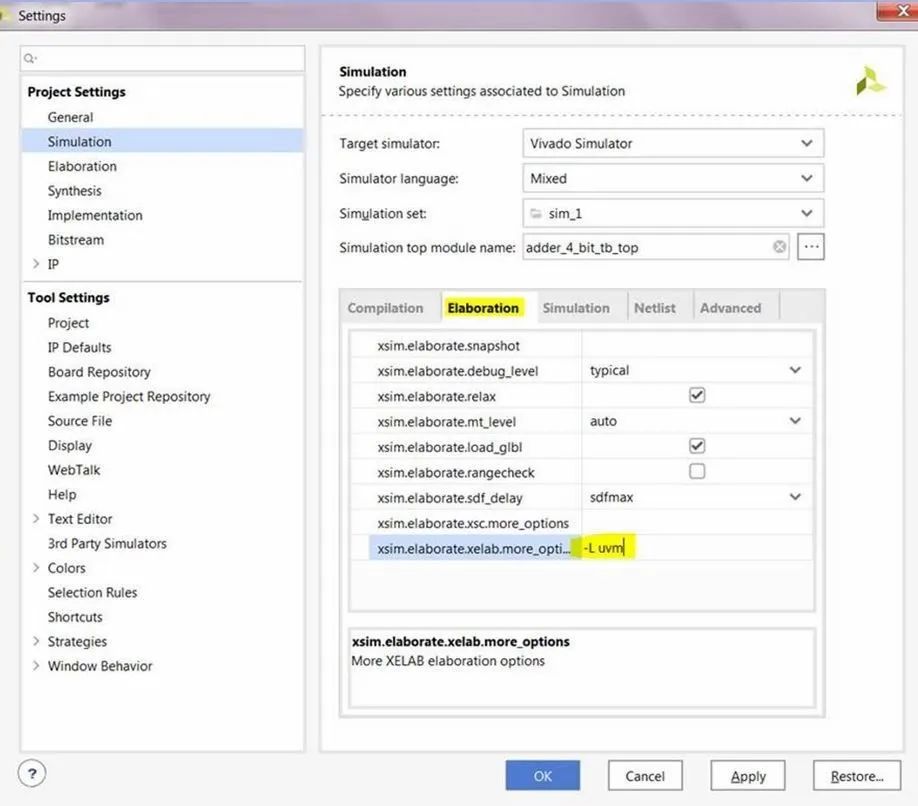

5. 使用來自“src”和“verif”目錄的新增源代碼創建工程后,請轉至“Settings”->“Simulation”。將“-L UVM”開關添加到位于“compilation”選項卡下的 xsim.compile.xvlog.more_options 以及位于“Elaboration”選項卡下的 xsim.elaborate.xelab_more_options(請參閱以下截屏)。此開關是使用預編譯的 UVM 庫所必需的。

此外,還可通過 Tcl 控制臺 (TclConsole) 設置下列屬性:

set_property -name {xsim.compile.xvlog.more_options} -value {-L uvm} -objects [get_filesets sim_1]

set_property -name {xsim.elaborate.xelab.more_options} -value {-L uvm} -objects [get_filesets sim_1]

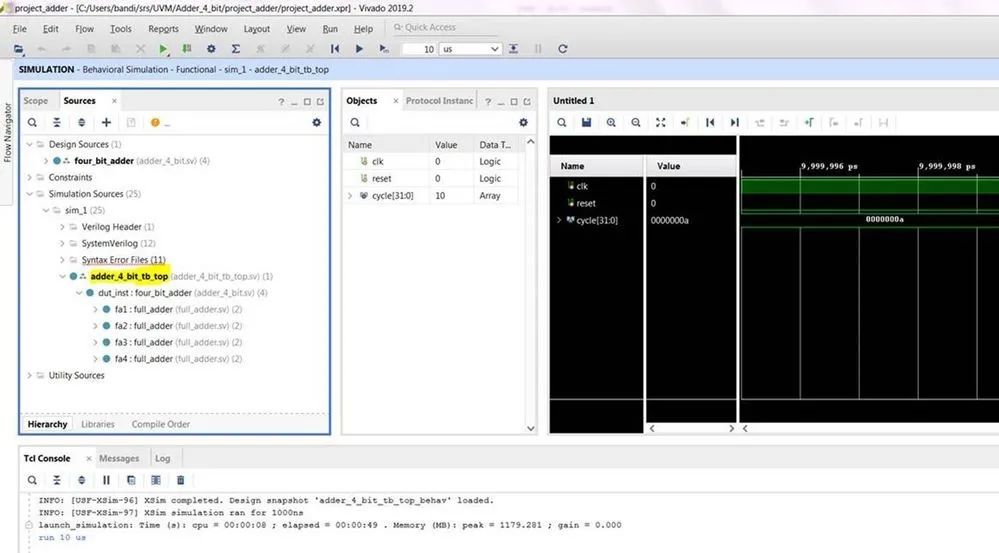

6. 添加以上開關后,請確保已選中“adder_4_bit_tb_top.sv”文件作為頂層模塊,然后運行仿真。

仿真應可正常完成運行,但 Vivado“Hierarchy”視圖中的“Sources”窗口將顯示這些文件上的語法錯誤。

您可忽略“Hierarchy”視圖和Vivado Text Editor 中的有關 UVM 的語法錯誤,因為 UVM 支持是在 Vivado 2019.2 中專為仿真器新增的。

對應 HSV 的 UVM 支持將于后續版本中提供。

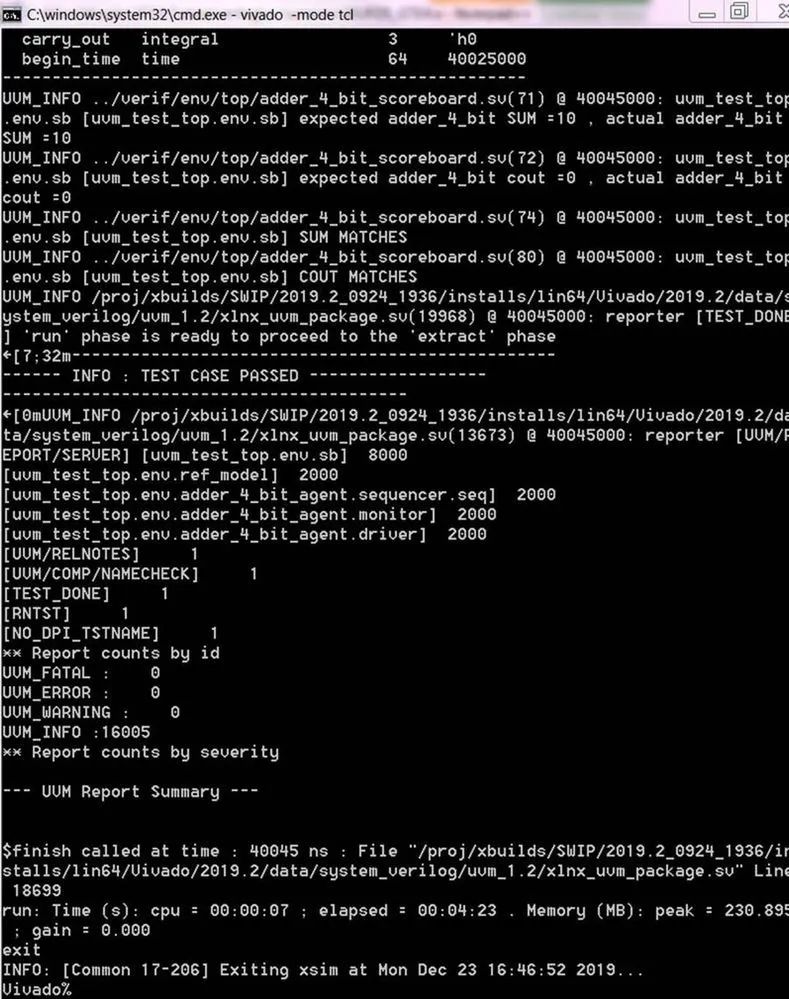

以下是非工程/批量模式下的 UVM 使用步驟:

a, 調用 Vivado 2019.2:

source

b, 要以非工程模式運行仿真,請從當前工作目錄切換至“run”文件夾。

cd ./Adder_4_bit/run

c, 要在Vivado 中運行獨立仿真,可運行 run_xsim.csh(在 Linux 上)和 run_xsim.bat(在 Windows 上),或者也可在 Linux/Windows 中使用以下命令來運行 run.tcl。

Vivado –mode batch –source run.tcl

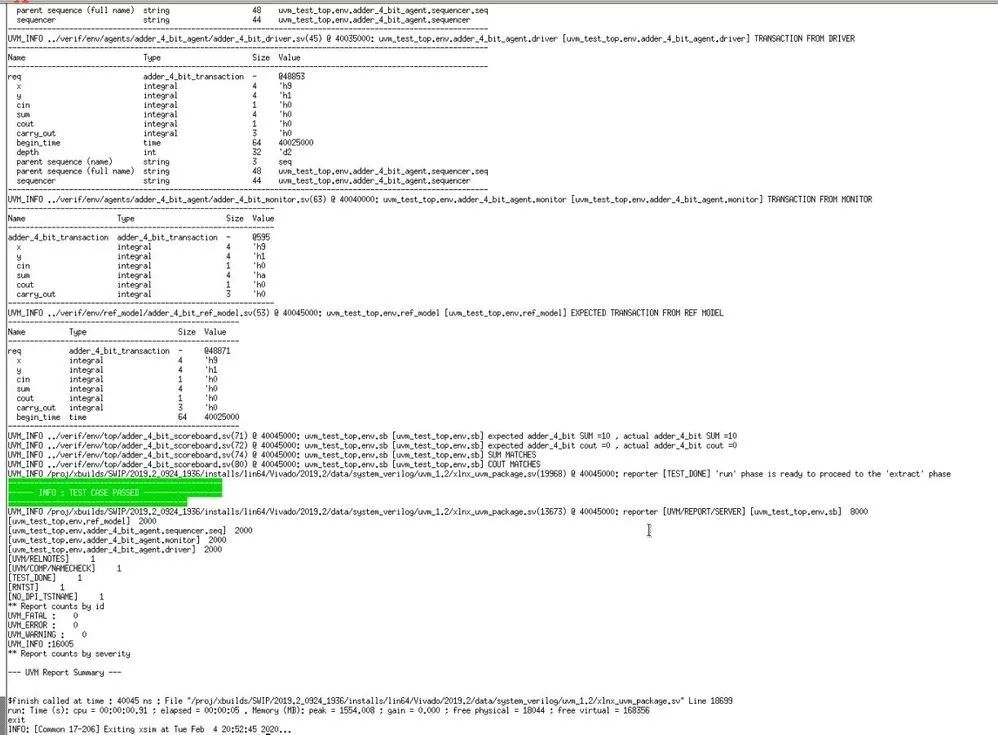

d, 完成仿真后,可以在 shell 中或命令提示符中查看 UVM 測試結果,如下所示:

工程模式和非工程模式的目錄結構:

“src”和“verif”文件夾包含設計和驗證環境相關的文件。

在非工程模式下,“Run”文件夾是運行仿真的位置。

UVM_test 則用于在 XSIM 中以“工程模式”運行仿真。

-

仿真器

+關注

關注

14文章

1018瀏覽量

83746 -

Vivado

+關注

關注

19文章

812瀏覽量

66539

原文標題:開發者分享 | Vivado 仿真器中的通用驗證方法學(UVM)支持

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Vivado仿真器中的通用驗證方法學(UVM)支持

Vivado仿真器中的通用驗證方法學(UVM)支持

評論