集成電路的發展要求互補金屬氧化物半導體(CMOS)晶體管在持續縮減尺寸的同時提升性能,降低功耗。隨著主流CMOS集成電路縮減到亞10 nm技術節點,采用新結構或新材料對抗場效應晶體管中的短溝道效應、進一步提升器件能量利用效率變得愈加重要。在諸多新型半導體材料中,半導體碳納米管具有超高的電子和空穴遷移率、原子尺度的厚度和穩定的結構,是構建高性能CMOS器件的理想溝道材料。已公開的理論計算和實驗結果均表明,碳管CMOS晶體管采用平面結構即可縮減到5nm柵長,且較同等柵長的硅基CMOS器件具有10倍的本征性能-功耗綜合優勢。

集成電路是現代信息技術的基石,隨著摩爾定律逐漸逼近極限,尋找硅材料替代品顯得尤為迫切。下一條集成電路材料“賽道”在哪里?日前舉行的東方科技論壇吸引了國內多位專家參與研討。目前,相比于石墨烯、二維材料等選項,碳納米管呼聲相對較高,被認為是比較有希望取代硅的未來電子材料。

如今,世界上最領先的集成電路工藝已經達到7納米,想要做得更小,硅材料在散熱、功耗等方面就呈現出短板。早在2006年,國際半導體技術路線圖委員會就認為,摩爾定律將在2020年達到極限。故此,他們推薦碳基納電子學(包括碳納米管和石墨烯)作為可能在未來五至十年內顯現出商業價值的下一代技術。根據測算,在步入10納米技術節點后,碳納米管的芯片性能和功耗都比硅芯片有了明顯改善。例如,從硅基7納米技術到5納米技術,芯片速度大約提升20%,而碳納米管基7納米技術的芯片速度將提升300%。

碳納米管集成電路批量化制備的前提是實現超高半導體純度(》99.9999%)、順排、高密度(100——200 /μm)、大面積均勻的碳納米管陣列薄膜。長期以來,材料問題的制約導致碳管晶體管和集成電路的實際性能遠低于理論預期,甚至落后于相同節點的硅基技術至少一個數量級,因而成為碳管電子學領域所面臨的最大的技術挑戰。

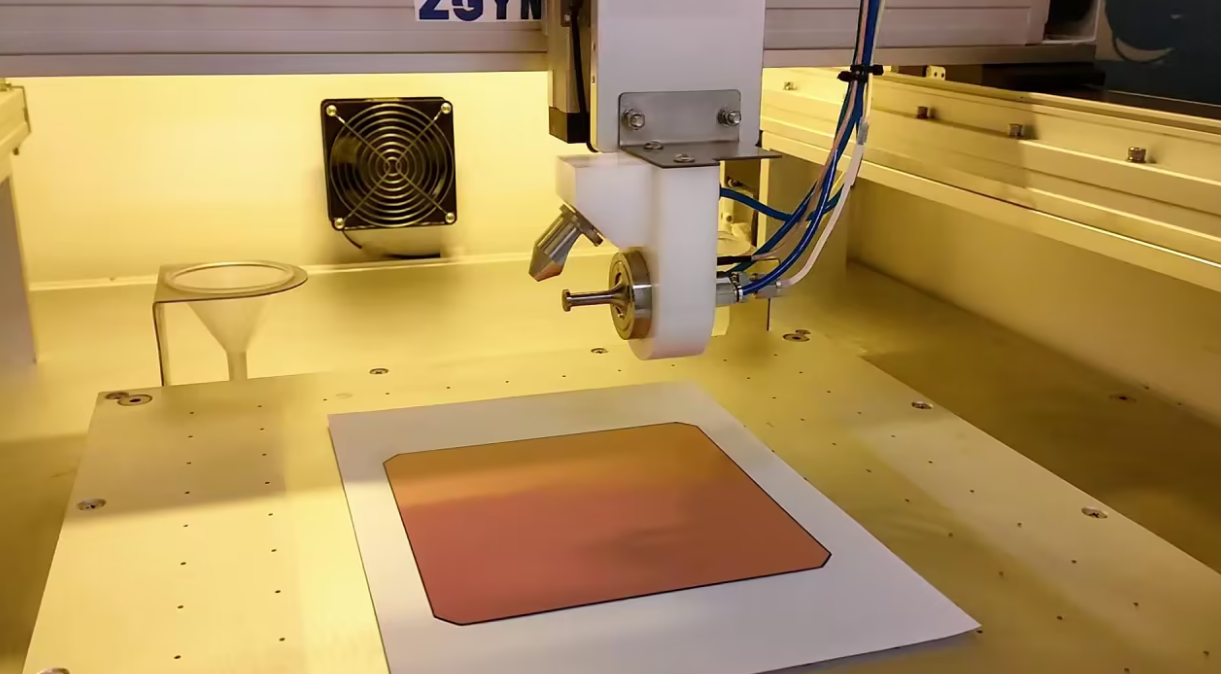

北京大學信息科學技術學院電子學系/北京大學碳基電子學研究中心、納米器件物理與化學教育部重點實驗室張志勇教授-彭練矛教授課題組發展全新的提純和自組裝方法,制備高密度高純半導體陣列碳納米管材料,并在此基礎上首次實現了性能超越同等柵長硅基CMOS技術的晶體管和電路,展現出碳管電子學的優勢。該課題組采用多次聚合物分散和提純技術得到超高純度碳管溶液,并結合維度限制自排列法,在4英寸基底上制備出密度為120/μm、半導體純度高達99.99995%、直徑分布在1.45±0.23 nm的碳管陣列,從而達到超大規模碳管集成電路的需求。基于這種材料,批量制備出場效應晶體管和環形振蕩器電路,100nm柵長碳管晶體管的峰值跨導和飽和電流分別達到0.9 mS/μm和1.3 mA/μm(VDD=1V),室溫下亞閾值擺幅為90 mV/DEC;批量制備出五階環形振蕩器電路,成品率超過50%,最高振蕩頻率8.06 GHz遠超已發表的基于納米材料的電路,且超越相似尺寸的硅基CMOS器件和電路。

該項工作突破了長期以來阻礙碳管電子學發展的瓶頸,首次在實驗上顯示出碳管器件和集成電路較傳統技術的性能優勢,為推進碳基集成電路的實用化發展奠定了基礎。2020年5月22日,相關研究成果以《用于高性能電子學的高密度半導體碳納米管平行陣列》(“Aligned, high-density semiconducting carbon nanotube arrays for high-performance electronics”)為題,在線發表于《科學》(Science,第368卷6493期850——856頁);電子學系2015級博士研究生劉力俊和北京元芯碳基集成電路研究院工程師韓杰為并列第一作者,張志勇和彭練矛為共同通訊作者。

上述研究得到國家重點研發計劃“納米科技”重點專項、北京市科技計劃、國家自然科學基金等資助。湘潭大學湖南省先進傳感與信息技術創新研究院、浙江大學、北京大學納光電子前沿科學中心等單位研究人員參與合作。

責任編輯:tzh

-

集成電路

+關注

關注

5388文章

11562瀏覽量

362043 -

半導體

+關注

關注

334文章

27442瀏覽量

219409 -

晶體管

+關注

關注

77文章

9701瀏覽量

138365

發布評論請先 登錄

相關推薦

安泰功率放大器應用:碳納米管薄膜YMUS超聲波噴涂

碳納米管在光電器件中的應用 碳納米管的功能化改性方法

碳納米管的結構與特性解析 碳納米管在能源儲存中的應用

碳納米管的導電性能介紹 碳納米管如何提高材料強度

碳納米管與石墨烯的比較 碳納米管在復合材料中的應用

碳納米管的主要應用領域 碳納米管在電子產品中的優勢

什么是N溝道場效應管和P溝道場效應管

金銀納米顆粒對單壁碳納米管實現近紅外熒光增強

半導體碳納米管是構建高性能CMOS器件的理想溝道材料

半導體碳納米管是構建高性能CMOS器件的理想溝道材料

評論