引言

加速度計是一種應用十分廣泛的慣性傳感器,它可以用來測量運動系統的加速度。目前的加速度計大多采用微機電技術(MEMS)進行設計和制造的微型加速度計,由于采用了微機電技術,其設計尺寸大大縮小,一個MEMS加速度計只有指甲蓋的一小部分,MEMS加速度計具有體積小、重量輕、能耗低等優點。

隨著微加速度計的應用越來越廣泛,對于微加速度計的數據信號采集和存儲變得極為重要。傳統的數據采集方法多數是用單片機完成的,其編程簡單、控制靈活,但缺點是控制周期長、速度慢,特別是對高速轉換的數據來說,單片機的慢速度極大地限制了數據傳輸速度。而FPGA(現場可編程門陣列)具有單片機無法比擬的優勢。FPGA時鐘頻率高,內部延時小,全部控制邏輯由硬件完成,速度快、效率高,適于大數據量的高速傳輸控制。在高速數據采集方面,FPGA有單片機無法比擬的優勢,然而單片機的接口豐富,數據處理能力強,便于完成數據的顯示和存儲等操作。

綜合單片機與FPGA的優點,這里介紹一種基于ARM和FPGA的微加速度計數據采集存儲系統,結合MXR6150G/M加速度計傳感器和TLC0820-A/D轉換芯片,提供了一種配置靈活、通用性強的數據采集方案。

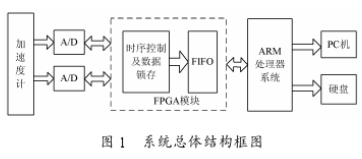

1、系統整體設計方案

圖1是數據采集系統的總體結構框圖,該系統主要由雙軸加速度計、A/D轉換器、FPGA和ARM處理器四大部分組成。雙軸加速度計輸出兩路模擬信號,分別代表z軸與y軸的加速度值,通過A/D轉換芯片把輸入的兩路模擬信號轉換為8位的數字信號,FPGA接收來自A/D轉換芯片的數字信號,并對數字信號進行處理,處理后的數據經過FPGA中的FIFO存儲器緩存后由ARM處理器采取中斷方式接收采集,采集到的數據可以通過串口通信在PC機上實時顯示,也可以通過IDE接口存儲到大容量硬盤。

2、系統硬件設計與實現

2.1 MXR6150G/M加速度計傳感器

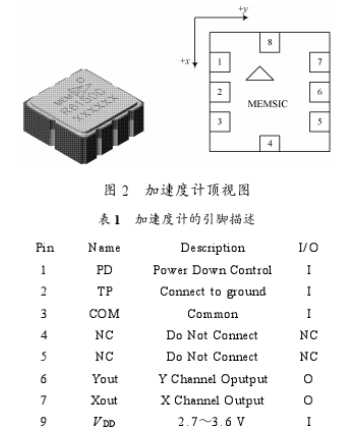

MXR6150G/M是無錫美新半導體公司生產的雙軸加速度計傳感器,它采用標準的亞微米CMOS工藝制造,可以測量從-5g~+5g(g為重力加速度)范圍內的加速度信號,該加速度計是利用兩路模擬電壓反映加速度值的大小,當加速度計靜止,加速度值為0時輸出電壓為1.50 V,電壓輸出靈敏度為150 mV/g。圖2為此加速度計的外觀頂視圖,表1為加速度計的引腳描述,其中引腳7和引腳6分別輸出x軸和y軸的加速度分量。實際加速度的值需要將x軸與y軸加速度的值進行合成得到,這可利用FPGA的并行計算處理來完成。

2.2 8位A/D轉換芯片TLC0820

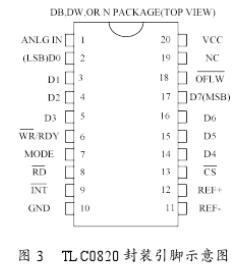

TLC0820是德州儀器公司(TI)推出的,采用先進LinCMOS工藝制造的A/D轉換器,它由兩個4位的閃速(FLASH)轉換器,一個4位的數/模轉換器,一個計算誤差放大器,控制邏輯電路和結果鎖存電路組成。它采用8位并行輸出,并且不需要外部時鐘和振蕩元件,廣泛應用于高速數據采集系統、工業控制和工廠自動化系統,其封裝引腳如圖3所示。引腳功能描述如下:ANLG IN為模擬輸入;為片選,低有效;DO~D3,D4~D7為三態數據輸出;為中斷輸出端,表示轉換結束;MODE為方式選擇輸入;為溢出標志;為讀輸人端;REF-為參考電壓下限值;REF+為參考電壓上限值;VCC為電源電壓;為寫輸入/讀狀態輸出。

2.3 Altera-FPGA與ARM處理器

該系統的FPGA采用Altera FPGA公司的CycloneⅡ系列的EP2C35實現,EP2C35提供多達33 216個邏輯單元(LE),35個18×18位乘法器483 840 b的內部RAM塊,專用外部存儲器接口電路,4個鎖相環(PLL)和高速差分I/O等功能。

該系統中采用的ARM處理器是Philips公司的LPC2210,是基于一個支持實時仿真和嵌入式跟蹤的16/32位ARM7TDMI-S CPU的微控制器。 LPC2210的144腳封裝、極低的功耗、兩個32位定時器、八路lO位ADC,PWM輸出以及多達九個外部中斷使其特別適用于工業控制、醫療系統、訪問控制和電子收款機等。通過配置,LPC2210最多可提供76個GPIO。由于內置了寬范圍的串行通信接口,其也非常適合于通信網關、協議轉換器以及其他各種類型的應用。

3、 采集系統整體實施方案

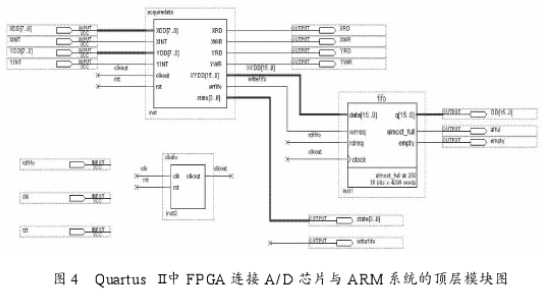

3.1 FPGA控制A/D芯片進行加速度計數據采集

該加速度計是利用兩路模擬電壓輸出來反映加速度值的大小,當加速度值為O時輸出電壓為1.50 V,電壓輸出靈敏度為150 mV/g,A/D轉換器模擬輸入電壓范圍為VCC±0.1 V,低于VREF- +(1/2)LSB或高于VREF+ -(1/2)LSB的模擬輸入電壓分別轉換為00000000或1111111,系統中所加電壓分別為VCC=VREF+=5 V,VREF-=GND=O V。TLC0820可通過MODE的設置工作在只讀和讀寫兩種方式。當MODE為低時,轉換器為只讀方式。在這種方式中,作為輸出,且作為準備輸出端;同時。當為低時,亦為低,表明器件忙,轉換器在的下降沿開始轉換,經過不到2.5μs轉換完成,此時下降.為高阻,數據輸出也由高阻變為有效的數據端,當數據讀出后,變高,返回高,數據輸出端返回到高阻態。當MODE為高時,轉換器為讀/寫方式,作為寫輸出端。當和為低時,轉換器開始測量輸入信號,大約600 ns后返回高,轉換器完成轉換,在讀寫方式中,在上升沿開始轉換。該實驗采用讀寫方式來控制A/D芯片來讀取加速度計的值,所需的控制信號由FPGA輸出,相關的邏輯控制采用Verilog硬件描述語言進行編寫,圖4為QuartusⅡ中FPGA連接A/D芯片與ARM系統的頂層模塊圖。

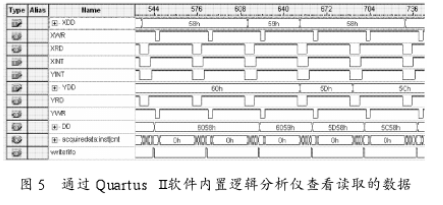

由A/D轉換輸出轉換后的8位數字信號,可以從QuartusⅡ內置的邏輯分析儀中讀取,圖5為通過QuartusⅡ軟件內置邏輯分析儀查看讀取數據值的截圖。從圖5中可以看出在讀寫方式中,在WR/RDY的上升沿開始啟動轉換,到INT的下降沿轉換完成,轉換時間可通過時間標尺計算出來,為24×40=960 ns,之后就可以通過RD的上升沿開始讀取轉換后的數據到數據總線中,如圖5中的XDD以及YDD。因為單片機的處理速度一般都低于A/D轉換芯片的速度,故將XDD與YDD的數據存儲到FPGA中的FIFO中,FIFO便起到數據緩沖的作用,以備接下來單片機對數據進行讀取。

3.2 ARM系統接收FPGA數據

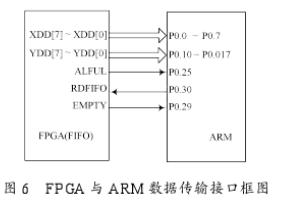

圖6為FPGA與ARM相連接部分的傳輸接口框圖。ARM系統主要控制數據采集的啟動和采集結束后對數據的顯示和存儲,在數據采集的過程中,ARM處理器系統讀取FPGA中的數據,實際上是讀取FIFO中的數據。FIFO的容量可以通過軟件進行設置,它有兩個狀態顯示信號,分別為ALFUL和EMPTY,ALFUL是指FIFO接近滿,當ALFUL從低電平變為高電平后,ARM單片機系統就可以發送RDFIFO信號來讀取FIFO中的數據輸出端口的數據,當FIFO中的EMPTY信號從低電平變為高電平,表明FIFO中已無數據可讀,ARM單片機就開始等待ALFUL的跳變進行下一次的讀取。

3.3 加速度數據顯示和存儲

由ARM系統采集到的數據可通過串口線發送到上位機進行實時顯示,也可以通過模擬IDE通信協議儲存到IDE硬盤中。LPC2210通過串口線與上位機進行通信主要是應用ARM芯片LPC2210中的通用異步接收/發送裝置UART0,而使用LPC2210的通用可編程I/O口,可以模擬產生IDE硬盤的讀寫時序,實現對存儲設備的讀寫操作。這樣可以實現加速度數據的顯示和存儲。

4、 結語

這里介紹一種MEMS器件微加速度計的數據采集設計方案,結合當前應用廣泛的處理芯片ARM和FPGA,給出了一種配置靈活、通用性強的數據采集方案。實驗中可準確采集美新加速度計MXR6150G/M的加速度信號,采集到的信號既可以在上位機實時顯示,又可以存儲在IDE接口硬盤中,達到了數據顯示和存儲的目的。

責任編輯:gt

-

FPGA

+關注

關注

1629文章

21736瀏覽量

603420 -

單片機

+關注

關注

6037文章

44558瀏覽量

635355 -

測量系統

+關注

關注

2文章

538瀏覽量

41395

發布評論請先 登錄

相關推薦

加速度計的幻想與現實

加速度計的技術規格詳解

MEMS加速度計性能成熟

基于加速度計的傾角測量精度提高

2422H-400加速度計

1527J-010加速度計

1521L-200加速度計

微加速度計的相關資料分享

基于微加速度計的AIR MOUSE的研究

基于ARM和FPGA的微加速度計數據采集系統設計

微加速度計的原理與應用

基于單片機與FPGA器件EP2C35實現微加速度計測量系統的設計

基于單片機與FPGA器件EP2C35實現微加速度計測量系統的設計

評論