基于FPGA的SOC在嵌入式系統應用越來越廣了,往往一個復雜系統使用一個單芯片基于FPGA的SOC就搞定了。比較流行的方案主要有Altera/xilinx兩家的方案。要用這樣的方案,首要需要掌握的是硬件描述語言。最為流行的硬件描述語言有兩種Verilog HDL/VHDL,均為IEEE標準。Verilog HDL具有C語言基礎就很容易上手,而VHDL語言則需要Ada編程基礎。另外Verilog HDL語言具有大量成熟的模塊,從某種角度說Verilog HDL更具生命力。 本文整理了一下Verilog HDL語言技術要點,并分享給大家。如發現有錯誤,歡迎留言指正。

Verilog HDL能干啥?

Verilog HDL的特點:

可描述順序執行或并行執行的程序結構

用延遲表達式或事件表達式來明確地控制過程的啟動時間

通過命令的事件來觸發其他過程的激活行為或停止行為

提供了條件/循環等邏輯控制結構

提供了可帶參數且非零延續時間的任務程序機構

提供了用于建立表達式的算術運算符、邏輯運算符和位運算符

實現了完整的表示組合邏輯基本元件的原語

提供了雙向通路和電阻器的描述

可建立MOS器件的電荷分享和衰減模型

可通過結構性語句精確地建立信號模型

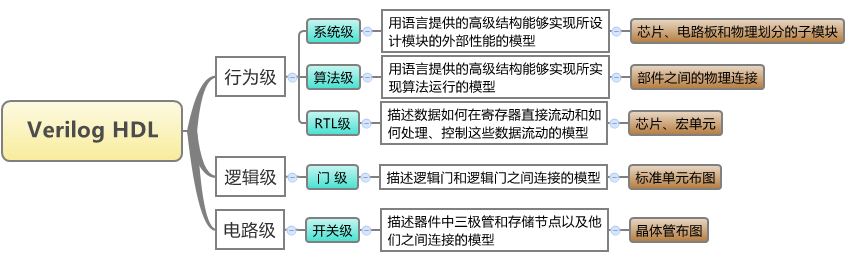

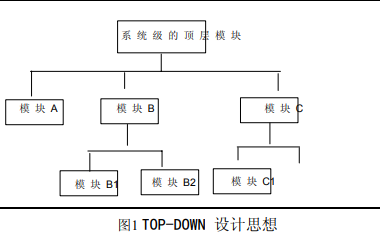

在學習Verilog HDL之前,先明確一下FPGA的設計抽象層次:

基本程序結構

modulemodule_name(port_list) //聲明各種變量、信號 reg//寄存器 wire//線網 parameter//參數 input//輸入信號 output//輸出信號 inout//輸入輸出信號 function//函數 task//任務 .... //程序代碼 initialassignment alwaysassignment moduleassignment gateassignment UDPassignment continousassignment endmodule

啟示:描述的是模塊,其本質是數字電路:

組合邏輯電路模塊:組合邏輯電路的特點是輸入的變化直接反映了輸出的變化,其輸出的狀態僅取決于輸入的當前的狀態,與輸入、輸出的原始狀態無關。

時序邏輯電路模塊:時序電路具有記憶功能。時序電路的特點是:輸出不僅取決于當時的輸入值,而且還與電路過去的狀態有關。時序邏輯電路又稱時序電路,主要由存儲電路和組合邏輯電路兩部分組成。

數據類型及運算符

變量名

變量名類似C語言,以一組字母、數字、下劃線和$符號的組合,且首字符須為字母或者下劃線。如

inputctrl_1;

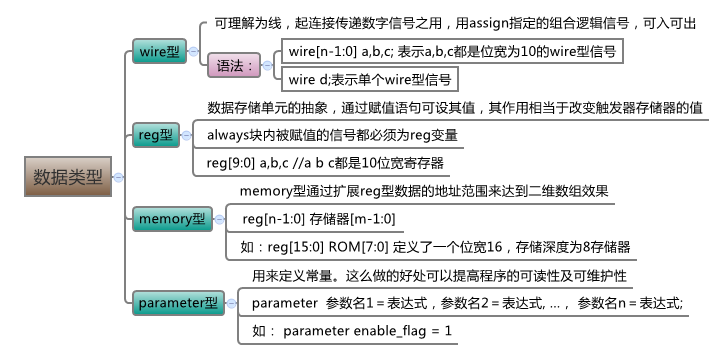

數據類型

將四種基本數據類型整理成一張導圖:

其中須注意的是,對于memory型存儲單元進行讀寫,須指定地址,如:

reg[15:0]addr;//定義addr為16位位寬的存儲器變量 addr=1;//ok regaddr[15:0];//定義addr為1位位寬的16個存儲器變量 addr=1;//錯誤 addr[0]=1;//正確 //又如: reg[15:0]addr[3:1];//定義3個位寬為16位存儲器 addr[1]=16'h0//16'指定位寬,h表示16進制,0 addr[2]=16'b011//b表示二進制

對于parameter變量的實用價值可讀性比較好理解,那么可維護性怎么體現呢?

熟悉C語言編程的,聯想一下宏,如果宏變了,有宏的地方全替換,這里parameter變量作用類似,如:

moduleDecode(A,F); parameterWidth=1,Polarity=1; …………… endmodule moduleTop; wire[3:0]A4; wire[4:0]A5; wire[15:0]F16; wire[31:0]F32; Decode#(4,0)D1(A4,F16); Decode#(5)D2(A5,F32); Endmodule

常量

parameter定義常量,那么對于常數,整型常量即整常數有以下四種進制表示形式:

二進制整數(b或B)

十進制整數(d或D)

十六進制整數(h或H)

八進制整數(o或O)

數字表達方式有以下三種:

<位寬><進制><數字>這是一種全面的描述方式。

<進制><數字>在這種描述方式中,數字的位寬采用缺省位寬(這由具體的機器系統決定,但至少32位)。

<數字>在這種描述方式中,采用缺省進制十進制。

x和z值

在數字電路中,x代表不定值,z代表高阻值。不確定是啥?高阻又是啥?記住verilog描述的數字電路,那么對于一個模塊的I/O就有可能是高阻,或者狀態不確定。

負數:

一個數字可以被定義為負數,只需在位寬表達式前加一個減號,減號必須寫在數字定義表達式的最前面。注意減號不可以放在位寬和進制之間也不可以放在進制和具體的數之間。

-8'd7//-號直接放在最前面 8'd-7//這樣則不正確

實數

實數可用十進制方式表述或者科學計數法描述,如:

//十進制表示 1.0 20.234 //科學計數法表示 6e-4

模塊端口

input:模塊從外界讀取數據的接口,在模塊內可讀不可寫

output:模塊向外部輸出數據的接口,模塊內部可寫不可讀

inout:可讀寫數據,數據雙向流動。

學習硬件描述語言,一定要時刻記住,這是描述的是電路,風格類C,但不是C!

表達式及運算符

和C語言類似,運算符也有三種:

單目運算符(unary operator):可以帶一個操作數,操作數放在運算符的右邊。

二目運算符(binary operator):可以帶二個操作數,操作數放在運算符的兩邊。

三目運算符(ternary operator):可以帶三個操作,這三個操作數用三目運算符分隔開。

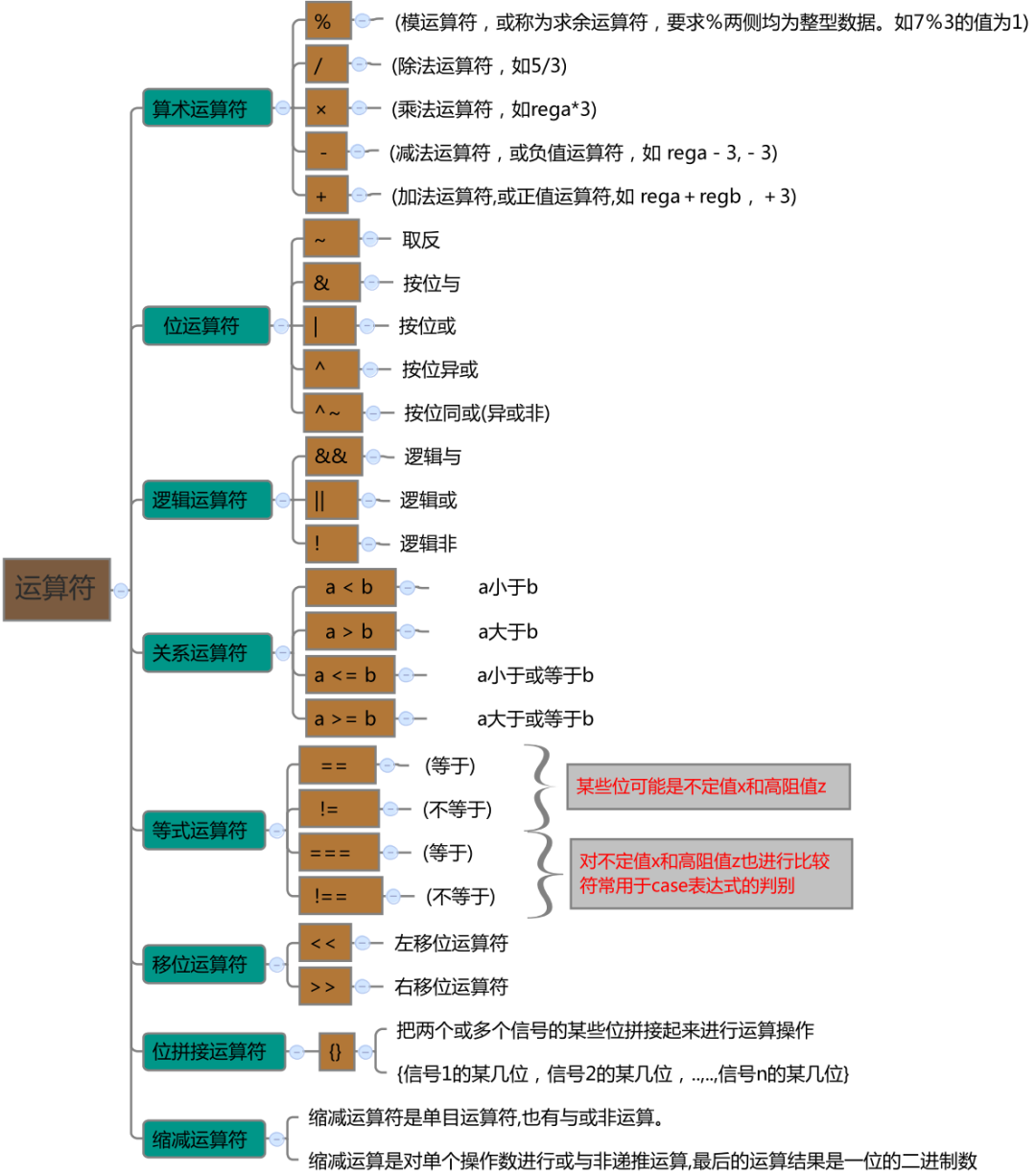

對于運算符,整理了一張導圖:

大部分與C語言類似,除了等式運算符、位拼接運算符、縮減運算符,這里放點例子方便理解:

//縮減運算符 reg[3:0]B; regC; C=&B; //相當于: C=((B[0]&B[1])&B[2])&B[3];//位拼接運算符 {a,b[3:0],w,3’b101} //相當于: {a,b[3],b[2],b[1],b[0],w,1’b1,1’b0,1’b1}

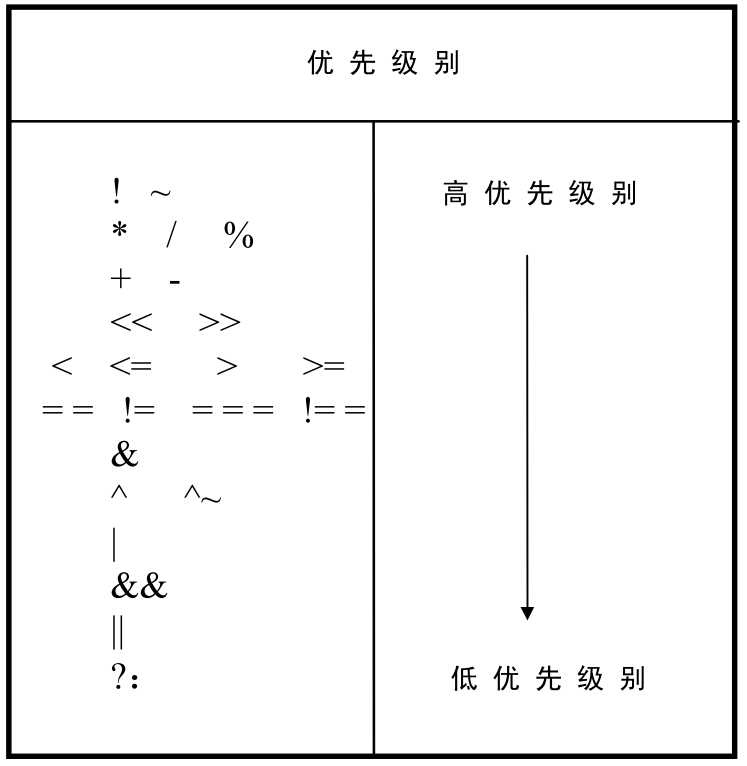

運算符優先級:

賦值語句

非阻塞(Non_Blocking)賦值方式, 如 b <= a; 加粗是非阻塞的含義

塊結束后才完成賦值操作。

b的值并不是立刻就改變的。

這是一種比較常用的賦值方法。

阻塞(Blocking)賦值方式,如 b = a;

賦值語句執行完后,塊才結束。

b的值在賦值語句執行完后立刻就改變的。

可能會產生意想不到的結果。

塊語句

塊語句有兩種,一種是begin_end語句,通常用來標識順序執行的語句,用它來標識的塊稱為順序塊。一種是fork_join語句,通常用來標識并行執行的語句,用它來標識的塊稱為并行塊。

順序塊

塊內的語句是按順序執行的,即只有上面一條語句執行完后下面的語句才能執行。

每條語句的延遲時間是相對于前一條語句的仿真時間而言的。

直到最后一條語句執行完,程序流程控制才跳出該語句塊。

begin 語句1; 語句2; ...... 語句n; end

并行塊

塊內語句是同時執行的,即程序流程控制一進入到該并行塊,塊內語句則開始同時并行地執行。

塊內每條語句的延遲時間是相對于程序流程控制進入到塊內時的仿真時間的。

延遲時間是用來給賦值語句提供執行時序的。

當按時間時序排序在最后的語句執行完后或一個disable語句執行時,程序流程控制跳出該程序塊。

fork 語句1; 語句2; ....... 語句n; join

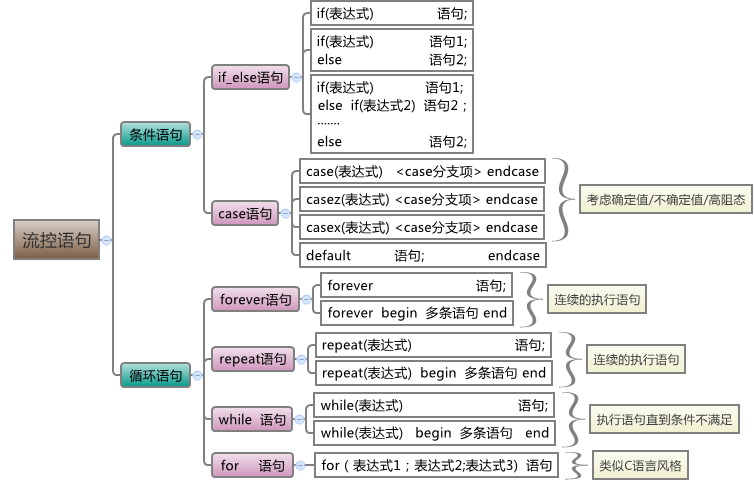

流控語句

流控語句風格與C語言類似,僅僅需要注意的有下面幾點:

if 語句別忘了考慮else的情況,如忘了處置則最終硬件會最終產生意想不到的后果

多條語句在條件內部需要用begin/end對包起來。

case語句與C語言也有default分支,實際使用注意處置default分支

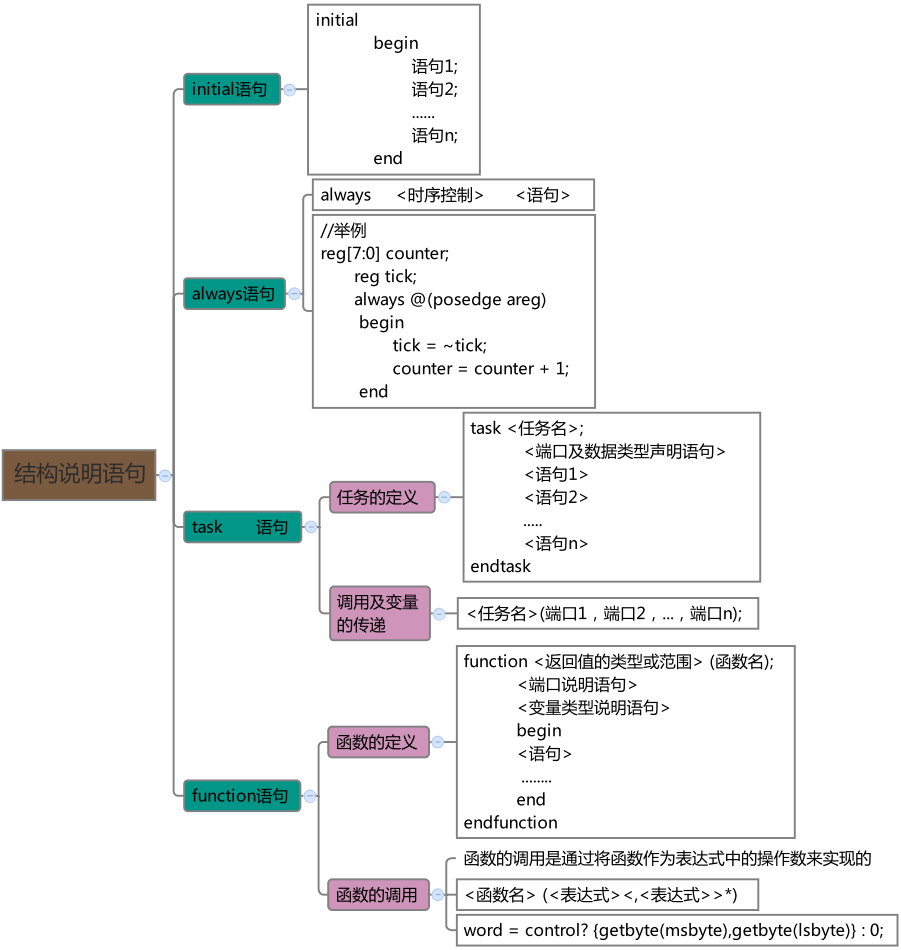

結構說明語句

Verilog語言中的任何過程模塊都從屬于以下四種結構的說明語句:

initial說明語句:只執行一次

always說明語句 :是不斷地重復執行

task說明語句

function說明語句

對于task/function的不同點,使用時需要注意:

函數只能與主模塊共用同一個仿真時間單位,而任務可以定義自己的仿真時間單位。函數的定義不能包含有任何的時間控制語句,即任何用#、@、或wait來標識的語句。

函數不能啟動任務,而任務能啟動其它任務和函數。

函數至少要有一個輸入變量,而任務可以沒有或有多個任何類型的變量。

函數返回一個值,而任務則不返回值。

函數的目的是通過返回一個值來響應輸入信號的值。任務卻能支持多種目的,能計算多個結果值,這些結果值只能通過被調用的任務的輸出或總線端口送出

在函數的定義中必須有一條賦值語句給函數中的一個內部變量賦以函數的結果值,該內部變量具有和函數名相同的名字。

系統函數和任務

在Verilog HDL語言中每個系統函數和任務前面都用一個標識符$來加以確認,有這些系統函數和任務。

rtoi, setup, skew, setuphold, strobe, time, timefoemat, width, write, $recovery,

按字面意思理解,需要用到時查詢手冊即可。

編譯預處理

宏定義 `define

用法:

`define 標識符(宏名) 字符串(宏內容)

如:

//類似C宏替換 `definesignalhello

與C語言宏類似,除了關鍵字不一樣,也支持嵌套。組成宏內容的字符串不能夠被以下的語句記號分隔開的,下面幾點需要注意:

注釋行

數字

字符串

確認符

關鍵詞

雙目和三目字符運算符

“文件包含”處理`include

用法:`include “文件名”

四點說明:

一個`include命令只能指定一個被包含的文件,如果要包含n個文件,要用n個`include命令。注意下面的寫法是非法的`include"aaa.v""bbb.v"

`include命令可以出現在Verilog HDL源程序的任何地方,被包含文件名可以是相對路徑名,也可以是絕對路徑名。例如:'include"parts/count.v"

可以將多個`include命令寫在一行,在`include命令行,只可以出空格和注釋行。

如果文件1包含文件2,而文件2要用到文件3的內容,則可以在文件1用兩個`include命令分別包含文件2和文件3,而且文件3應出現在文件2之前

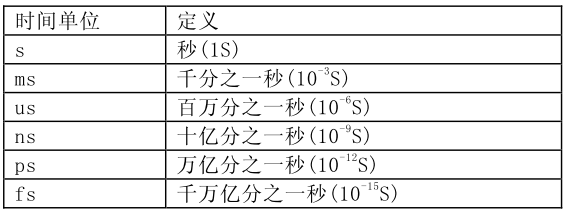

時間尺度 `timescale

`timescale命令用來說明跟在該命令后的模塊的時間單位和時間精度。使用`timescale命令可以在同一個設計里包含采用了不同的時間單位的模塊。用法:

`timescale<時間單位>/<時間精度>

//模塊中所有的時間值都表示是1ns的整數倍 //1ns/ps:1納秒/脈沖 `timescale1ns/1ps

注意:如果在同一個設計里,多個模塊中用到的時間單位不同,需要用到以下的時間結構:

用`timescale命令來聲明本模塊中所用到的時間單位和時間精度。

用系統任務$printtimescale來輸出顯示一個模塊的時間單位和時間精度。

用系統函數realtime及%t格式聲明來輸出顯示EDA工具記錄的時間信息。

條件編譯命令

`ifdef、`else、`endif

這與C語言用法類似,這里就不贅述了。

總結一下

Verilog HDL的語法與C語言的語法類似,但是一定要意識到Verilog HDL描述的是電路,光有代碼還不夠,器件可能運行的結果并不是代碼想要的效果。另外要注意理解并行的概念,這里的并行是硬件在時鐘驅動真的同時按照所設計的邏輯運行。一些重要的概念:

阻塞〔Blocking〕和非阻塞〔Non-Blocking〕賦值的不同

順序塊和并行塊的不同

塊與塊之間的并行執行的概念;

task和function的概念。

那么最好的學習辦法是什么呢?寫代碼、仿真、綜合、優化布局布線,挖坑、踩坑、填坑,在錯誤中總結,漸進明晰、不斷實踐總結。

-

C語言

+關注

關注

180文章

7604瀏覽量

136827 -

Verilog HDL

+關注

關注

17文章

126瀏覽量

50415

原文標題:看思維導圖:一文帶你學Verilog HDL語言

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于Verilog HDL語言的FPGA設計

Verilog HDL華為入門教程

Verilog HDL語言在FPGA/CPLD開發中的應用

Verilog HDL入門教程

Verilog HDL入門教程

Verilog HDL的基礎知識詳細說明

Verilog HDL語言技術要點

Verilog HDL語言技術要點

評論