1

性能挑戰(zhàn)

企業(yè)日益重視基于 AI 的系統(tǒng)在數(shù)據(jù)中心、汽車、工業(yè)和醫(yī)療等領(lǐng)域中的產(chǎn)品化。

這帶來(lái)了兩大挑戰(zhàn):

AI 推斷需要完成的計(jì)算量成數(shù)量級(jí)增加,同時(shí)還要保持價(jià)格、功耗、時(shí)延和尺寸大小不變。 AI 科學(xué)家繼續(xù)日復(fù)一日地在算法和模型上開(kāi)展創(chuàng)新,需要各種不同的硬件架構(gòu)提供最佳性能。

2

方案概述

對(duì)于 AI 推斷,在提供與浮點(diǎn)媲美的精度的同時(shí),int8 的性能優(yōu)于浮點(diǎn)。然而在資源有限的前提下,int8 不能滿足性能要求,int4 優(yōu)化是解決之道。通過(guò) int4 優(yōu)化,與現(xiàn)有的 int8 解決方案相比,賽靈思在實(shí)際硬件上可實(shí)現(xiàn)高達(dá) 77% 的性能提升。賽靈思4 位激活和 4 位權(quán)重 (4A4W) 全流程硬件友好型量化解決方案可實(shí)現(xiàn)更優(yōu)異的精度/資源權(quán)衡取舍。

該白皮書(shū)介紹了在Zynq UltraScale+ MPSoC 和 Zynq-7000 SoC 系列(16nm和28nm)上面向CNN4位XDPU實(shí)現(xiàn)的低精度加速器。這種加速器通過(guò)高效地映射卷積計(jì)算,充分發(fā)揮其DSP功能。這種解決方案可提供優(yōu)于XDPU兩倍的解決方案級(jí)性能。在ADAS系統(tǒng)中執(zhí)行2D檢測(cè)任務(wù)時(shí),這種實(shí)現(xiàn)方案能在ZynqUltraScale+MPSoCZCU102板上實(shí)現(xiàn)230fps的推斷速度,與8位XDPU相比性能提高1.52倍。

此外,在用于ADAS系統(tǒng)中的不同任務(wù)時(shí),該解決方案可實(shí)現(xiàn)媲美全精度模型的結(jié)果。

3

技術(shù)導(dǎo)讀

對(duì)持續(xù)創(chuàng)新的強(qiáng)烈需求需要使用靈活應(yīng)變的領(lǐng)域?qū)S眉軜?gòu) (DSA)。優(yōu)化 AI 推斷性能和降低功耗的主要趨勢(shì)之一是使用較低精度和混合精度。為降低硬件設(shè)計(jì)復(fù)雜性,模型量化被當(dāng)作關(guān)鍵技術(shù)應(yīng)用于各類硬件平臺(tái)。大量工作被投入用于最大限度地降低 CNN 運(yùn)算量和存儲(chǔ)成本。這項(xiàng)研究充分地證明,對(duì)于大多數(shù)計(jì)算機(jī)視覺(jué)任務(wù),在不嚴(yán)重犧牲精度的情況下,權(quán)重和激活可以用 int8 表達(dá)。

然而對(duì)于某些邊緣應(yīng)用而言,硬件資源仍然不足。在對(duì)邊緣應(yīng)用使用較低的位寬(如 1 位、2 位)時(shí),一些常見(jiàn)的硬件設(shè)計(jì)解決方案使用簡(jiǎn)化的乘法器。盡管這些解決方案時(shí)延低、吞吐量大,但它們與全精度模型相比,仍然存在較大的精度差距。因此,在模型精度和硬件性能之間尋求平衡變得至關(guān)重要。

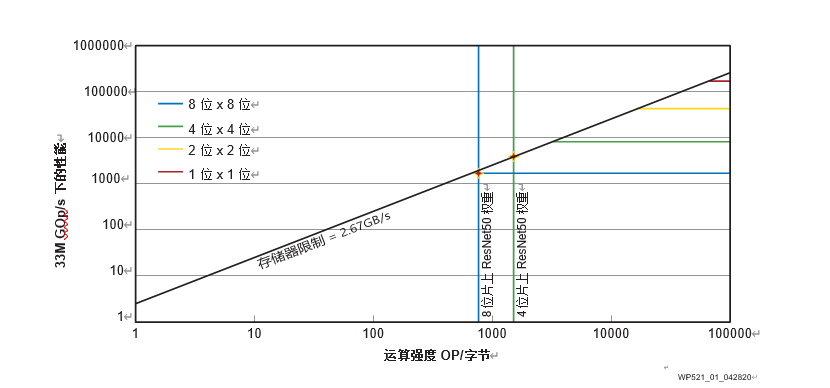

賽靈思運(yùn)用幾種常見(jiàn)的網(wǎng)絡(luò)結(jié)構(gòu)(ResNet50V1、ResNet50V2 、MobilenetV1和MobilenetV2),在 ImageNet 分類任務(wù)上通過(guò)使用幾種不同的量化算法進(jìn)行了實(shí)驗(yàn)。結(jié)果顯示精度隨著位寬減少而下降。尤其是在位寬低于 4 時(shí)精度下降顯著。此外,賽靈思也使用 Williams 等介紹的 Roofline 模型,分析不同位寬下的硬件性能。

在ZCU102上以不同位寬運(yùn)行Roofline模型

如圖 1 所示,以賽靈思 ZCU102 評(píng)估板為例,隨著 MAC 的精度降低,硬件成本降低,性能得到提高。此外,實(shí)驗(yàn)結(jié)果還顯示,低比特量化可通過(guò)降低存儲(chǔ)器需求提高性能。這在 ResNet-50 神經(jīng)網(wǎng)絡(luò)的卷積運(yùn)算強(qiáng)度上得到證實(shí)。該網(wǎng)絡(luò)分別用 8 位精度和 4 位精度進(jìn)行了運(yùn)算。因此,int4 在模型精度和硬件性能之間實(shí)現(xiàn)了最佳權(quán)衡。

-

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4776瀏覽量

100952 -

AI

+關(guān)注

關(guān)注

87文章

31262瀏覽量

269630 -

adas

+關(guān)注

關(guān)注

309文章

2189瀏覽量

208747

原文標(biāo)題:卷積神經(jīng)網(wǎng)絡(luò)能用 INT4 為啥要用 INT8 ?- 最新白皮書(shū)下載

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

卷積神經(jīng)網(wǎng)絡(luò)能用INT4為啥要用INT8?

卷積神經(jīng)網(wǎng)絡(luò)能用INT4為啥要用INT8?

評(píng)論