我們電子產品往往 60%以上-可靠性方面的問題都出現在電子線路板的 PCB 設計上;工作及性能良好的 PCB 需要相關的理論及實踐經驗;我在產品的設計實踐中經常碰到各種各樣的問題;比如電子線路板不能通過系統 EMS 的測試標準,測試關鍵器件 IC 的功能引腳時出現高頻噪聲的問題,電路功能 IC 引腳檢測到干擾噪聲進行異常保護等等。

通過理論與實踐結合;用測試數據檢驗我們的理論和實踐的差異點!優良的設計跟長期的經驗總結是密不可分的!

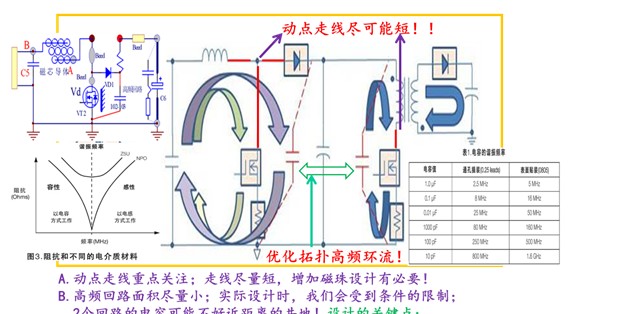

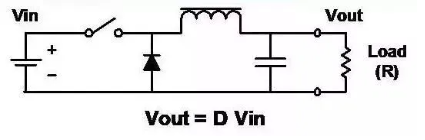

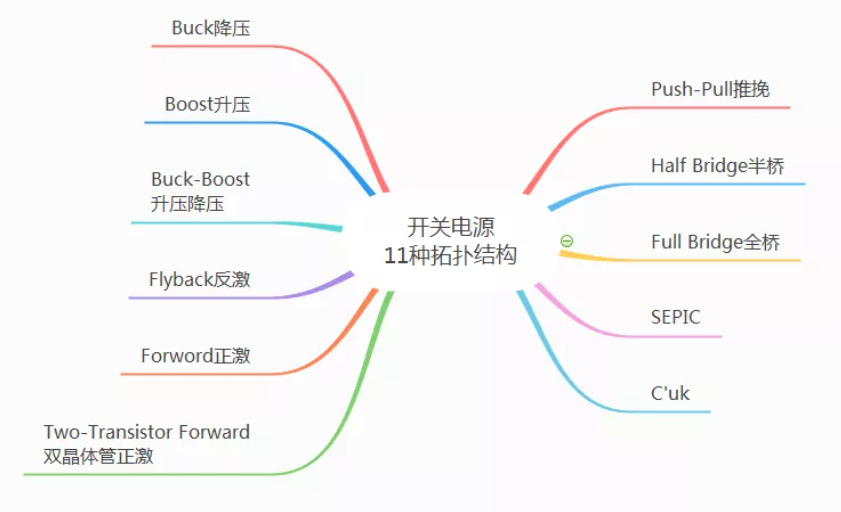

1.開關電源通過以下的原理示意圖分享設計總體原則

圖示為我們常用的兩種開關電源的拓撲結構;

A.開關電源拓撲主電流回流路徑面積最小化;驅動脈沖電流回路最小化。

B.對于隔離開關電源拓撲結構,電流回路被變壓器隔離成兩個或多個回路(原邊和副邊),電流回路要分開最小回流面積布局布線設計。

C.如果電流回路有多個接地點,那么接地點要與中心接地點重合。

D.實際設計時,我們會受到條件的限制;如果 2 個回路的電容可能不好近距離的共地!

設計的關鍵點:

我們就要采用電氣并聯的方式就近增加一個高頻電容達成共地(如圖紅色虛線)!

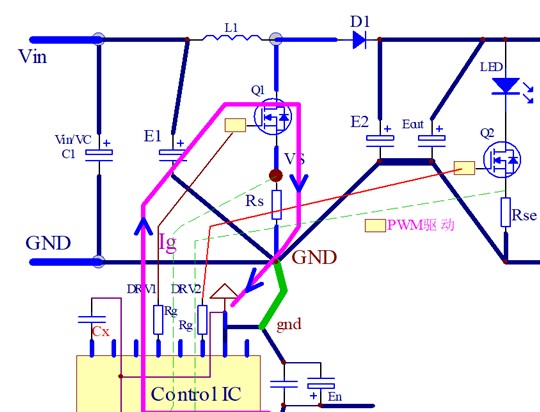

2.對于非隔離的 IC 控制器與主功率回路系統的 PCB 設計思路

如下圖為-非隔離的電源給 IC 控制器供電,IC 控制器控制 LED 的負載并進行調光及其它功能的控制應用。其控制器的供電及驅動回路的設計會影響系統的功能及可靠性。

通過圖示 IC 控制器-PCB 布局布線的設計思路如下:

A1.IC 周邊器件的地走線優先布局布線后連接到 IC-gnd;

A2.IC-gnd 再連接到濾波電容 C1(高頻電容-低容值)的接地端,如果是非隔離系統;存在主電源系統進行動態工作時,此地不再進行 12V 非隔離電源地連接。

A3.IC-控制中心的 gnd 要單點接地!C1 電容靠近 IC-gnd 引腳,引腳地與 C1 電容-gnd 最短連接。

關鍵環路

B.主電源回路路徑的最小化設計原則

C.拓撲電流回路路徑最小化設計原則

D.脈沖驅動回路路徑最小化設計原則

注意條件受限時:電源的主回路與拓撲回路的電容可能不共地,我們可以采用電氣并聯的方式就近增加一個高頻電容達成共地!

3.具體 BOOST 的 LED 驅動架構的 PCB 布局布線進行具體分析

設計基本思路如上所述;用下圖進行設計分析

在圖示中:黃色跳線(JX)有與 12V 回路地進行最小化環路面積的理論設計。

PCB 藍色高亮部分為系統 GND 走線,白色高亮部分為 12V-IC 供電電源正端走線。

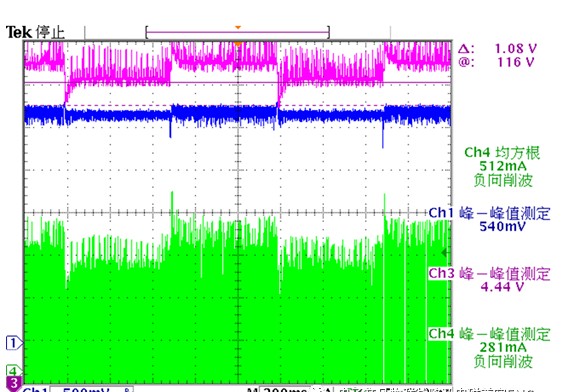

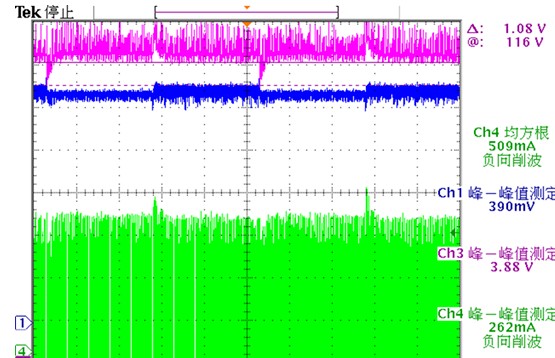

通過實際的數據測試驗證黃色跳線(JX)連接線接地對系統的影響:

測試條件:12V-6A 115V/600mA (燈條)

測試項目:12V 負載動態負載時間間隔 500ms max load/minimum load6.6A/0.2A

示波器設置

CH1:12V(偏置 10V) CH3:115V(偏置 100V) CH4:ILED(偏置 500mA)

黃色跳線(JX)在回路中:

黃色跳線(JX)去除

通過優化環路響應,增加動態響應速度。

黃色跳線(JX)的系統回路影響:

由于 12V 同時給控制 IC 提供 VDD,在進行差分信號走線時 12V 與 GND 布線時即電源與地的回流面積最小;當 12V 拉負載時,12V 電解電容正到地回流;當 12V 負載電流增加時地走線阻抗不等于 0,這時在公共地阻抗上就會產生電壓差,導致地基準位的變化。

去掉黃色跳線(JX)后,控制回路變成單點接地。此時地電位基準的影響就不受多個回路電流的影響。在非隔離的系統中單點接地符合設計理論。

設計經驗總結:

可能存在多種原因,IC 供電電源有多種應用功能連接。

A.對于隔離的控制器 IC 電路提供 VDD,在進行差分信號走線時 12V 與 GND 布線時即電源與地的回流面積最小;

B.對于非隔離 IC 控制的 GND 要避免形成環路;IC 同側引腳的相同功能引腳的 GND 走線要連接在一起到 IC-GND;IC-控制中心的 gnd 要求單點接地。

責任編輯:pj

-

pcb

+關注

關注

4319文章

23099瀏覽量

397890 -

開關電源

+關注

關注

6462文章

8337瀏覽量

482041 -

控制器

+關注

關注

112文章

16361瀏覽量

178051

發布評論請先 登錄

相關推薦

基站開關電源的管理及維護

開關電源沖擊電流的控制方法

開關電源的浪涌電流是什么?如何抑制?

llc開關電源和普通開關電源的區別

開關電源模塊的作用 開關電源測電流怎么測

開關電源電流取樣電阻損壞原因

開關電源PCB布局優化,人人都該懂的“黃金法則”是什么?

開關電源幾種拓撲結構介紹

開關電源沖擊電流測試方法有哪些

開關電源加載電流緩慢上升的解決方法

如何快速掌握11種開關電源拓撲結構?看這篇就夠了!

開關電源拓撲主電流回流路徑設計的總體原則

開關電源拓撲主電流回流路徑設計的總體原則

評論