來源:半導體行業觀察

在英特爾2020年度架構日中,英特爾將大量時間用于討論公司的GPU架構計劃。雖然這對英特爾來說并非罕見,但目前該公司仍然以CPU內核而聞名。因此,他們在圖形方面的市場關注度一直較弱。但是正如英特爾在其他領域的舉措,隨著時代的變化,英特爾不僅將越來越多的裸芯片投入到GPU中,而且在接下來的兩年中,他們正在轉變為PC GPU領域真正意義上的第三人,并且推出了他們的首個產品:獨立GPU。

從英特爾曾宣布的Xe GPU架構可以看出,該公司打算成為一家自上而下的GPU供應商。這意味著Intel要為數據中心和HPC集群到高端游戲機和筆記本電腦的所有產品提供分離式和集成的GPU。由于這些涉及到大量的工程設計,因此對于一家在過去十年中僅提供集成GPU的公司來說,這是一次巨大的飛躍。但終于在經過數年的討論和展望之后,英特爾客戶想象中的Xe即將成為現實。

我們將在其他文章中重點介紹與Xe相關的內容,本文的重點內容是Xe-LP。我們先快速回顧一下英特爾Xe計劃的現狀,目前的最新動態以及Xe-LP更大的適用范圍。

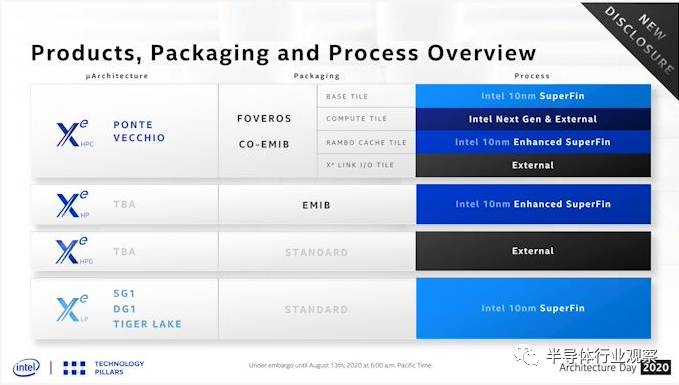

早在2018年首次宣布時,英特爾就制定了針對單個GPU架構Xe的計劃,該架構由三個不同的微架構組成:Xe-LP,Xe-HP和Xe-HPC。Xe-LP分別從底部到頂部跨越市場,并進入集成和入門級離散圖形,然后Xe-HP進入發燒級和數據中心部分,最終Xe-HPC將用于高性能計算集群。例如,即將到來的Aurora正是美國能源部期待已久的超級計算機。

從那時起,英特爾對該計劃進行了一些修訂,曾經的三個微體系結構變成了四個。在今天的英特爾年度架構日中,英特爾宣布推出Xe-HPG,這是針對游戲芯片的另一種微架構。本文將重點討論Xe-HPG,而這正是英特爾產品堆棧中缺失的高層次難題,因為與Xe-HP相比,它提供了高性能的游戲和圖形芯片。該芯片聚焦于數據中心功能,例如FP64和多區塊可伸縮性。Xe-HPG計劃將于2021年啟動,與Xe系列的其他產品不同的是,Xe-HPG將完全由第三方工廠制造。

由于Xe-LP再次引發熱議,今年英特爾首款Xe微體系結構的推出變得更加重要。為了應用于更廣泛的設計,英特爾針對Xe的計劃包括建立連續的Xe部件(對Xe-HPC而言,這一點尤為重要)。該設計包含越來越多的基本構建基塊以擴展GPU的數量(即便如此還是不夠)。因此,Xe-LP是Xe系列的基礎,這一點不僅適用于圖形,也適用于架構。英特爾為Xe-LP設計的產品將對整個Xe產品堆棧產生重大影響。

Xe-LP:與Tiger Lake集成,但屬于分離式

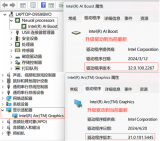

英特爾針對Xe的產品計劃雖然看似將它們推廣到了更廣泛的領域,但這正是由于英特爾GPU始終具有一個相同的起點:集成顯卡。作為英特爾新推出的Tiger Lake SoC的一部分,Xe和Xe-LP將在市場上首次亮相,該公司將于9月2日推出該芯片。盡管英特爾并沒有談論Tiger Lake產品方面的其他內容(英特爾寧愿保留今天的架構,也不愿在9月發布產品),但Tiger Lake顯然是Xe-LP設計的重點。因此,正如我們在討論Xe-LP的功能時所得出的結論:是 Tiger Lake促成了這一切。

今日,據英特爾官方透露, Tiger Lake的零件只用一個Xe-LP切片就明顯達到極限。現在,這一代產品已經成為Intel基本的GPU執行單元(EU)中的96個。總體而言,該公司的目標是使Ice Lake(Gen11)圖形的性能提升至2倍。

但是Xe-LP不僅僅應用于Tiger Lake。正如英特爾先前所披露,該公司正在開發分布式GPU版本,他們將其稱為DG1。DG1的設計用于與筆記本電腦和其他移動設備中的Tiger Lake配對。DG1是20多年來英特爾首款分布式GPU,也是英特爾GT3和GT4e集成GPU配置的精神繼任者。相較于使用大型GPU來構建小批量CPU設計,英特爾更傾向于OEM廠商出售的分布式GPU,該GPU基于集成GPU的體系結構和10nm SuperFin工藝。

DG1將于今年發貨,所以敬請期待它在性能更高的Tiger Lake筆記本電腦中出現。但是,英特爾在其他方面的披露很少,因為他們今天沒有談論有關產品配置的其他信息。因此,盡管我們知道它基于Xe-LP并且專注于移動設備(英特爾已排除了應用于臺式機的所有可能性),但我們沒有任何諸如配置或內存等內容的官方詳細信息。

作為最終支柱,服務器空間會留在Xe-LP上。英特爾將為他們稱為SG1的服務器提供一個四核GPU產品。這個基于四個DG1 GPU的產品將替代英特爾的Xeon可視化計算加速器系列。Xeon VCA卡旨在利用英特爾早期的集成GPU,其以英特爾的QuickSync媒體模塊來加速該過程,從而瞄準視頻編碼市場。現在,英特爾擁有分布式GPU,因此他們不再需要為視頻編碼市場組合CPU,而可以僅使用GPU出售加速器。對于更大的GPU生態系統來說,這是一個利基市場。但是對于英特爾來說,這是一個至關重要的市場。因此他們希望SG1能使服務器運營商崛起并且獲得關注,或者至少擺脫其令人厭惡的寄生蟲形象。

Xe-LP功能集:具有可變速率陰影的DirectX FL 12_1

在介紹完了架構深層驅動器之后,本文首先將簡要概述Xe-LP的圖形功能集。因為此處沒有太多新話題要討論,我將其稱為快速摘要。

從API級別的角度來看,Xe-LP的功能集實際上與Intel的Gen11圖形集完全相同。與AMD的RDNA1架構不同,英特爾已決定將精力集中在更新GPU架構的底層方面,從而對底層部分進行諸多更改。最終,相對于圖形功能而言,上層的變化相對較小。

最終結果是Xe-LP是DirectX功能級別12_1加速器,并且他還具有幾個附加功能。尤其是第1層的可變速率陰影(最初在Intel的Gen11硬件中引入)在Xe-LP中又回來了。盡管不如更新的2層功能實現強大,但它提供基本的VRS支持,并且游戲可以按每次渲染請求設置。值得注意的是,英特爾仍然是唯一支持第1層的供應商。AMD和NVIDIA已經(或正在)直接進入第2層。

至少對英特爾來說這是一個好消息,在AMD將其逐步納入其所有產品之前,他們已經在Gen11方面領先于這場比賽,甚至為其最慢的集成GPU都提供了12_1支持。因此,在這一點上,英特爾仍然可以與其他集成顯卡解決方案相提并論。

不利之處在于,這也意味著英特爾是唯一一家在2020年推出不支持下一代功能的新GPU /體系結構的硬件供應商,Microsoft&co將其命名為DirectX 12 Ultimate。功能級別12_2面向消費者的商品名DirectX Ultimate結合了對可變速率著色第2層的支持,以及光線跟蹤,網格著色器和采樣器反饋。對英特爾而言,能否在2020年的集成部分進行光線追蹤的始終是一個很大的疑問。但是能有所進展已經令人欣慰。另外,由于它是不帶12_2功能的獨立GPU,因此DG1顯得有些奇怪。

Xe-LP切成薄片:96個EU擴大50%

英特爾沒有把重點放在高級圖形功能上,而是將注意力轉移到了GPU的低級架構細節上。Xe-LP是未來Xe GPU的奠基石,因此,在這個領域,英特爾需要正確地處理設計和功率效率方面的問題,以便為構建未來的產品奠定穩固的基礎。 可以肯定的是,英特爾早期GPU設計中的基礎類比范圍也是如此。盡管Xe是一個新的品牌,并且是英特爾更大的起點,但它并不是僅僅是英特爾GPU的設計。相反,它是Gen11的重點發展,其更新和替換了出于可伸縮性或效率方面的原因而需要更改的那些位。因此,Gen11可以保留很多東西,而Intel GPU的基本組織結構保持不變。

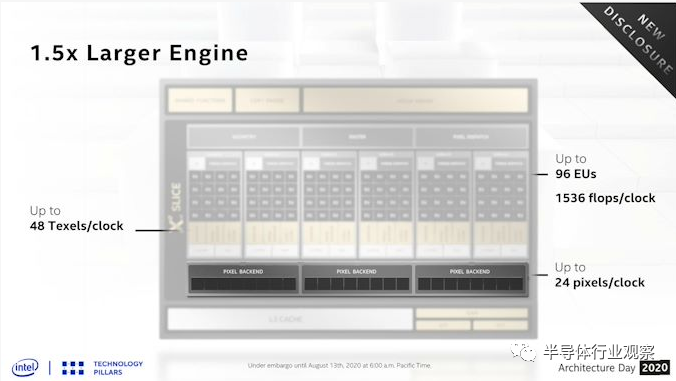

與往常一樣,這意味著我們將從Xe-LP Slice和英特爾的總體GPU設計目標開始。英特爾公司最大的通用構建塊,即公司的GPU分為一個或多個切片,一個切片包含計算和渲染所需的核心功能塊的完整副本。這包括幾何圖形和柵格前端,線程分配硬件,EU本身,紋理單元以及ROP像素后端。

英特爾借助Xe-LP將片中的幾乎所有內容擴展了50%。這意味著與Intel的Gen11 iGPU碰巧只占一小塊的情況相比,在GPU的大多數方面都可以多執行50%的執行硬件。這包括增加50%的EU(使總數增加到96個EU),紋理單元和ROP,總速率分別為48像素/時鐘和24像素/時鐘。

切片中沒有被這樣一個因素明確放大的唯一部分是前端。仍然有一個單獨的幾何/柵格化器/像素調度前端為切片的其余部分提供數據,并且由于Intel尚未披露幾何吞吐量的任何變化,我在這里假設Intel仍僅按時鐘每時鐘調度1個基元片。因此,任何改進都必須取決于時鐘速度。 而且時鐘速度肯定在提高。與英特爾的Willow Cove CPU內核一樣,該公司正在努力提高其新的10納米SuperFin工藝的能效和時鐘速度的改進,以使其能夠提高GPU時鐘速度以滿足其性能目標。正如我們之前討論的那樣,英特爾希望在這里將Gen11的GPU性能提高一倍,而執行硬件的50%最多只能滿足一半的需求,其余的大部分增長將來自更高的時鐘速度。作為參考,英特爾的Ice Lake部件最高達到1.1 GHz,因此,鑒于英特爾的性能預測,看到Tiger Lake和DG1達到1.6 GHz或更高的頻率也就不足為奇了。

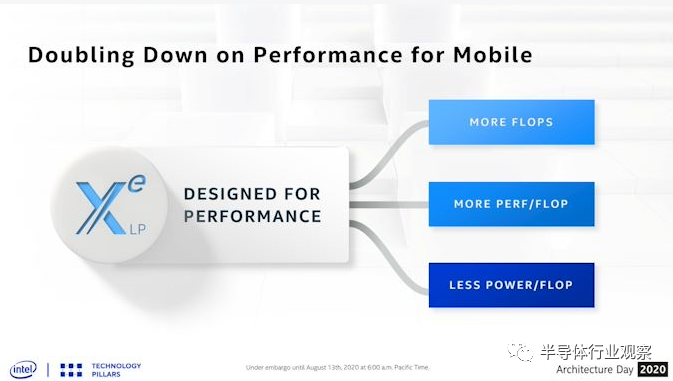

因此,完善英特爾提高GPU性能的計劃來自Xe-LP設計的第三大支柱:提高效率。EUs的增加促使了FLOP的增加,而提高能效使Intel可以將芯片的時鐘提高到更高,以增加更多FLOP。但是僅增加FLOP是不夠的,體系結構的有效吞吐量還必須提高,這樣才能將更多的理論上的FLOP轉化到(convert?)實際工作中。

這就是英特爾秘訣的來源,而英特爾技術市場部門的貢獻并不多。我們會在短時間內對EU進行一些顯著的低層更改,但這些更改更多是關于推動上述電源效率更改。相反,吞吐量效率的變化更加模糊。在這里,英特爾只是告訴我們,他們已經使用工作負載分析來識別并消除整個GPU中的多個小瓶頸,從而提高圖形和計算吞吐量的效率。 英特爾的L1緩存更改也可能在其中起作用,盡管該公司目前并沒有過多地考慮這些更改。不過,我們將在查看整個內存系統時再稍作討論。

分片重組

另一方面,擴大總體范圍導致英特爾已經重組了更大范圍內的子范圍。子切片在某些方面類似于NVIDIA SM和GPU中的一個較小的構建塊,其專注于各種形式的計算和著色以及紋理化。對于英特爾的Gen11 GPU,該公司將GPU分為8個子切片,每個子切片包含8個EU。但是,使用Xe-LP可以擴大每個子分片的數量,并減少總分片的數量。

Xe-LP上的完整片現在是6個子片。每個Xe-LP子片段依次看到其許多屬性都翻了一番。子切片中的EU數量增加了一倍,達到16個,而子紋理采樣器的吞吐量已從4像素/時鐘提高到8像素/時鐘。每個子切片還獲得一個L1數據/紋理緩存,該緩存為64KB,可以在L1數據和紋理存儲之間動態分配。該緩存似乎將取代Gen11記錄不充分的L2緩存,后者在層次結構中扮演著類似的角色。 這些子更改又與英特爾對EU所做的一些更改并存,我們將在下一頁介紹這些更改。由于EUs失去了一點點獨立性并變得結對,每個子線程的線程控制單元數保持恒定為8。因為總體而言它們需要處理和管理的子線程更少了,所以這可能有助于英特爾針對未來解決方案的可擴展性。 這一變化的結果意味著,英特爾的iGPU可擴展性步驟也將有所不同。Ice Lake出廠時啟用了64個EU(8個子分區),48個EU(6個子分區)或32個EU(4個子分區),具體取決于SKU,而Tiger Lake的粒度現在僅為切片的六分之一。因此,這意味著一半的GPU現在為48個EU(3個子分區),一個完整的GPU為96個EU(6個子分區),并且英特爾必須決定是否以及如何在啟用80或64個EU的情況下在中間運輸SKU。由于英特爾今天不提供生產信息,我們只能進行相關推測。但是如果在完全啟用的Xe-LP iGPU之后的下一層是64 EU配置,則其性能將大大下降,造成了33%潛在增長的損失。

Xe-LP執行單元:成雙成對

更深入地講,我們擁有Xe-LP GPU架構中最小的線程級構建塊,即古老的執行單元。多年來,英特爾已對其進行了幾次調整,而對于Xe-LP,它們又在進行調整。 作為快速更新單元,截止到英特爾的Gen11 GPU架構為止,EU由一個線程控制單元和兩組4寬SIMD組成。一個塊處理浮點數和整數運算,而另一塊可以處理浮點數和特殊函數,英特爾將其稱為“擴展運算”。盡管如此,Gen11的最小波面寬度為8個線程寬(SIMD8),因此執行一個波面可能需要多個時鐘周期,而英特爾會將多個波面交織為一種延遲隱藏形式。

同時,Xe-LP給EU的設計帶來了一些重要的變化。首先,一個EU不再是一個獨立的大區。現在,兩個EU共享一個線程控制單元。結果,線程控制單元現在獲得了兩個EU(不再是一個)的組合資源來分散工作。盡管SIMD陣列本身也發生了變化,這使問題進一步復雜化,但其影響在于,GPU中的線程控制單元現在越來越少,這將減少在任何給定時刻In-flight波面數量。 實際上,有人爭論這兩個EU是否為描述它們的最準確方法。最佳選擇將它們捆綁在一起作為一個單一的“大EU”,因為這兩個部分都不是真正獨立的。但是由于缺少更多底層細節,而且我確定英特爾希望在對EU進行計數時保持半一致性,所以他們選擇了96個“小EU”。 同時,無論您如何捆綁EU,都存在EU本身的問題。對于Xe-LP,英特爾已經重組了SIMD模塊。一對具有功能差異的SIMD4已不再支持SIMD8和SIMD2。較大的SIMD8本質上將先前在Gen11的兩個SIMD4模塊之間分配的所有浮點和整數ALU組合在一起,并從中分離出一個SIMD8。最終結果是FPU ALU的數量沒有改變(每個EU仍然是8個ALU),但是可以處理整數的管道數量已經改變(從4到8),可以擴展的ALU數量也已經改變運算法則(從4到2)。

說到這一點,擴展運算現在已移至其自己的SIMD2,并且每個EU都有一個。這意味著執行擴展的數學函數不再像Gen11那樣直接阻止浮點算術的執行(EU不必為此放棄FP管道)。需要著重強調的一點是,EU可以同時向FP / INT SIMD8和EM SIMD2同時發布指令,這意味著在至少某些情況下,進行擴展運算也不會間接阻止FP / INT運算。

與共同發布時出現的問題一樣,細節仍然很棘手。在這一點上,我們尚不清楚共同發布的局限性是什么。但它仍然很可能更適合英特爾實際看到的那種工作負載。AMD和NVIDIA還使用專用的EM / SFU單元,并且比例也很小,對于這兩家公司來說,所有這些似乎都很好。因此,在這方面,英特爾的ALU設置看起來更像是它的現代競爭對手。我懷疑,這也是英特爾為了從Xe-LP上相同數量的FLOP中獲取更多效果而做出的瓶頸優化形式之一。 這些ALU更改還會影響波面在GPU中的移動方式。SIMD8是常規算術中最小的ALU陣列,英特爾的最小波面尺寸現在與底層硬件相同。這意味著Xe-LP至少在最小波面尺寸的情況下,不再需要多個周期來在單個周期內從波面執行一條指令。在Gen11中,英特爾還允許存在SIMD16和SIMD32波陣面,而我正在等待Xe-LP白皮書以確認是否保留了這些(在這種情況下,它們仍然需要多個周期),或者英特爾是否正在將所有內容強制設為SIMD8。 值得注意的是,這一變化與AMD去年的RDNA(1)架構非常相似,它通過增加SIMD大小并返回其波面大小來消除波面的多周期執行。在這種情況下,這樣做是為了幫助保持其SIMD插槽的占用率更高,并減少指令等待時間,如果英特爾也遇到類似的情況,我不會感到驚訝。

這種重組的另一個好處是,英特爾能夠從整體上簡化其線程調度硬件。直到第11代,英特爾仍在使用硬件記分板來確定何時運行線程以及何時準備就緒線程的數據。但是,借助Xe-Lp,計分板已經轉移到軟件中,由英特爾編譯器來負責。 遷移到軟件計分系統意味著必須由軟件預先確定計劃(這樣會使其變得靜態,并有可能導致計劃不盡人意),好處就是硬件計分板會由于權力立場和模面積變得相當昂貴。因此,轉向軟件計分制可以實現更小,更省電的EU,這反過來又體現了英特爾建立大量EU并提高整體能源效率的能力。總體而言,這與NVIDIA在十年前通過開普勒對其體系結構所做的更改相對應。他們在開普勒上同樣采用了軟件記分板,以提高能效(并同時保持高性能)。

數字決定EU吞吐量

現在我們已經有幸看到在EU層面所做的所有更改,下面我們來談談這對于EU的實際吞吐率意味著什么。

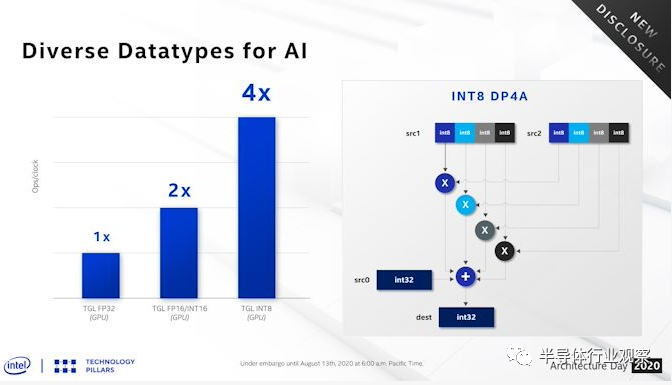

從浮點開始都很簡單。盡管對ALU進行了重組,但每個EU的FP ALU數量仍為8。因此,與Gen11一樣,每個EU的FP吞吐量仍保持在16 FP32 ops / clock和32 FP16 ops / clock。 另一方面,對于整數吞吐量,具有整數功能的ALU的數量相對于Gen11體系結構已從4倍增加到8倍。結果,整數吞吐量也增加了一倍:Xe-LP每個時鐘周期可以保存8個INT32運算或32個INT16運算,而Gen11分別為4和16。但是,這的確意味著Xe-LP保留了Gen11的不尋常的INT32故障。INT32速率僅是FP32速率的一半,而INT16速率等于FP16速率。 最后,毫無疑問的是Xe-LP沒有等效于張量核心或其他脈動ALU的數組來進行密集的數學運算,這已經成為神經網絡訓練推理的全部方法。該硬件將以Xe Matrix eXtensions(XMX)的形式出現在Xe系列的后面,但現在Xe-LP必須與常規的EU接軌。

但是出于這個原因,英特爾在其EUSIMD中又增加了一項功能,即對INT8點產品的支持。在過去的幾年中,INT8在神經網絡推理中變得越來越流行,而點積反過來又是該過程中非常普遍的一種操作。因此,增加對INT8點產品的支持使Xe-LP在這種形式的AI執行中得到了極大的推動。INT8在使用DP4A指令之后,其吞吐率可以高達64 ops / clock,是INT16吞吐率的兩倍。

Xe-LP媒體和顯示控制器

接下來我們討論最后一點:Xe-LP架構的GPU的非渲染方面--媒體和顯示控制器。此處的更改并不像對核心體系結構的更改那樣引人注目,但是在這些功能塊中進行的改進通過支持新的媒體格式和新的顯示連接協議,有助于使整個GPU保持最新狀態。 首先,讓我們談談媒體引擎。雖說英特爾沒有對Xe-LP進行大量修改,英特爾對引擎做了一些明智的添加。此處的選框功能很容易支持AV1解碼加速,使Intel成為三巨頭中第一個為新編解碼器添加硬件解碼支持的供應商。

人們普遍期望,即將出現的免版稅編解碼器將成為H.264 / AVC的真正繼任者,因為HEVC進入市場已經有很多年了(并且已經受到最近所有的GPU支持)。編解碼器附近的madcap專利使用費情況不利于其采用。相比之下,AV1在分發中的使用應提供與HEVC相似或略好于HEVC的質量,而無需支付版稅,這使其對內容供應商的吸引力更大。迄今為止,AV1的一個缺點是CPU占用大量內存。一方面是出于對電池壽命的考慮,而另一方面是確保流暢和無故障的播放,這些都使得硬件解碼支持變得更加重要。 同時,類似于英特爾的渲染性能目標,該公司一直致力于提高媒體引擎的編碼和解碼吞吐量。據英特爾稱,更新后的模塊現在能夠實現高達2倍的編碼和解碼吞吐量。對于消費類計算機而言這似乎無關緊要,但是對于SG1服務器產品而言,它尤為重要,因為它將專注于批量編碼。 最后,在對媒體引擎進行的較小更改中,英特爾增加了對HDR和Dolby Vision播放的官方支持。即使速度很慢,對HDR的支持將繼續向PC推廣,因此這是確保較新的PC能夠處理以這些格式編碼的HDR內容的重要一步。同樣值得注意的是對英特爾HEVC編碼模塊的改進。為了在提高具有靜態或接近靜態圖像內容的HEVC壓縮率,該模塊現在支持HEVC屏幕內容編碼(SCC)擴展,

Xe-LP顯示控制器:DisplayPort 1.4,HDMI 2.0和8K顯示器

最后需要特別提到的一點就是,我們擁有Xe-LP的顯示引擎。如同在媒體塊方面,這里沒有根本性的變化,但是整個過程中都有一些可喜的改進。 也許最大的變化會發生在數年之后,英特爾最終會增加第四條顯示管道,這意味著到時候GPU可以驅動四個獨立的顯示器。在此之前,Gen11和其之前的設計只能處理三個顯示器,盡管即使這個數目超出大多數人的使用范圍,但四個顯示器足以讓其他GPU設計難以望其項背。最近對雙屏筆記本電腦和其他具有多個顯示器的移動設備的推動將會使事情更加復雜化,因為這將吞噬這三個輸出中的兩個。

值得注意的是,英特爾還添加了第二個嵌入式DisplayPort輸出,這對于那些雙屏設備非常有用。 否則,其基本顯示輸出選項會與Gen11相同。Xe-LP支持DisplayPort 1.4和HDMI 2.0。由于HDMI 2.1電視現在已經上市,因此后者有點令人失望,但是對于Intel來說,去花更多的時間來采用更新的HDMI標準并非罕見。這些顯示輸出還可以饋入USB4 / Thunderbolt 4端口,其中DisplayPort數據是一流的公民,可以復用到信號中,也可以通過alt模式重新配置端口。 雖說在英特爾的框圖上并不明顯,該公司還是進行了一些重大更改以更好地為顯示控制器供電。具體來說,該公司增加了顯示引擎可用的帶寬,以便處理DisplayPort 1.4設計用于饋送的超高分辨率顯示器。因此,該控制器現在具有足夠的帶寬和內部處理能力,可以驅動8K UHD顯示器以及最新一代的360Hz顯示器。

性能期望與初衷

英特爾結束了對GPU架構的深入研究,盡管其沒有利用今年的架構日來討論特定的產品和SKU,但公司確實花了一些時間討論對Xe-LP的性能期望,并在其中提供了一些有關Xe-LP快速圖像化的實際行動。遺憾的是,我們不允許錄制演示過程(但還是有人泄露了這些演示),但我們將在英特爾向公眾發布副本后立即將其發布在此處。

如前所述,無論如何,英特爾的目標是使Ice Lake(Gen11)的圖形性能提高一倍,Xe-LP將通過更寬的GPU(更多的硬件),更節能的GPU(允許更高的時鐘頻率)以及效率更高的GPU(更高的IPC)的組合來實現。考慮到他們沒有從全新的工藝節點中受益,這是一個崇高的目標,但是英特爾似乎對其新的10nm SuperFin工藝節點的性能潛力,以及通過向其嘗試過的產品中其投入更多硬件獲得的回報頗有信心。

通過對Ice Lake和Ryzen 3000“ Renoir”筆記本電腦的評論進行查看,我們可以看到自己的性能數據,如果Intel能夠達到其性能目標,那么Tiger Lake應該能夠領先于AMD的同類U系列Ryzen APU。一如往常,這將取決于游戲本身,但是在GPU受限的情況下,高端Ice Lake筆記本電腦永遠不會落后30%左右。但是,由于我們在談論移動場景,因此電源和散熱始終是可能使筆記本電腦無法使用的潛在威脅。對于超便攜式游戲筆記本電腦更是如此,英特爾無疑將希望其合作伙伴制造具有匹配散熱功能的筆記本電腦,從而為Tiger Lake提供一切可能的成功機會。 除了幀率,英特爾還希望Xe-LP的性能能夠大大提高圖像質量的標準。為了提供必要的幀率,集成顯卡通常會提高圖像質量,因此將iGPU性能提高一倍將使許多游戲可以在更高圖像質量設置下運行。這又會因游戲而異,但是至少出于促銷目的,英特爾盯上了Tiger Lake / Xe-LP,因為它們能夠在Ice Lake只能處理低畫質的游戲是以高圖像質量運行。

但是Xe-LP不僅是集成的圖形解決方案,它還適用于離散圖形。盡管我們熱切期望獲得更多有關DG1的信息,但是鑒于英特爾今天將重點放在產品的架構上,我們所面臨的問題多于答案。英特爾針對Xe-LP制定了一個非常有趣且對OEM友好的計劃,并且通過為iGPU和可選的離散GPU利用相同的架構。OEM會希望看到,他們將不必驗證和加載用于集成和離散GPU的單獨GPU驅動程序。 但是,最重要的是,英特爾還拒絕回答與1000萬像素的相關問題:Tiger Lake的iGPU是否能夠與DG1協同工作?英特爾當然還沒有開始抹除這個想法,但是他們也沒有證實這一想法。即使這樣,如果他們使用多GPU渲染,他們會成功嗎?臺式機上的多GPU渲染幾乎已經消失。這是有原因的:在現代渲染技術下,它往往無法很好地發揮作用,并且可能會增加相當多的輸入滯后。有關以上問題的答案,以及英特爾是否能夠克服多GPU渲染的傳統缺陷,絕對會對DG1 GPU的商業可行性產生巨大影響。因此,我們將熱切期望這些問題能夠得到回答。

否則,Xe-LP標志著英特爾GPU架構發展的重要一步,不必在意成為自上而下的GPU供應商的計劃中的巨大墊腳石。盡管Xe-LP僅面向筆記本電腦,但它是英特爾更大的基礎:Xe-LP將成為未來整代GPU的基礎。因此,英特爾在功能,架構以及最重要的方面所做的工作,對于從游戲硬件到超級計算機的所有功能,功率效率都會產生巨大的影響。從許多方面來說,這都是英特爾進入新時代的曙光,他們希望這是一個比他們留下的更好的時代。

來源:半導體行業觀察

原文標題:企業 | 英特爾GPU架構深度解讀

文章出處:【微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

-

芯片

+關注

關注

455文章

50832瀏覽量

423818 -

英特爾

+關注

關注

61文章

9968瀏覽量

171806 -

gpu

+關注

關注

28文章

4741瀏覽量

128963

原文標題:企業 | 英特爾GPU架構深度解讀

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

世紀大并購!傳高通有意整體收購英特爾,英特爾最新回應

英特爾12月或發布Battlemage GPU芯片

Inflection AI轉向英特爾Gaudi 3,放棄英偉達GPU

英特爾發布AI創作應用AI Playground,將于今夏正式上線!

英特爾CEO:AI時代英特爾動力不減

在英特爾酷睿Ultra處理器上優化和部署YOLOv8模型

英特爾確認Ponte Vecchio GPU將以云服務形式推出

英特爾逐步停止Ponte Vecchio GPU生產,專注于Gaudi 2/3產品

英偉達、AMD、英特爾GPU產品及優勢匯總

X-Silicon發布RISC-V新架構 實現CPU/GPU一體化

解讀英特爾GPU架構

解讀英特爾GPU架構

評論